100G以上骨干网用高速PCB孔损耗技术研究

2015-02-05韩雪川深南电路股份有限公司广东深圳518053

韩雪川(深南电路股份有限公司,广东 深圳 518053)

100G以上骨干网用高速PCB孔损耗技术研究

Paper Code: S-081

韩雪川

(深南电路股份有限公司,广东 深圳 518053)

在发送端,100G信号被分为10路或4路高速信号,加上OTN和FEC开销,每路信号为10G+bit/s或更高的25G+bit/s,体现在印制电路板上则为单对差分阻抗线实现10G+bit/s、25G+bit/s的传输速率。文章主要从减少孔损耗的角度分析了实现了单PCB走线速率100Gbit/s,突破了背钻技术、跳孔技术,有效保证了100G以上骨干网高速印制电路板的技术实现。

100G;高速;损耗;背钻;跳孔

1 前言

随着大数据、云计算、光纤宽带的应用和普及,对骨干网传输损率的要求越来越高,原有的40G方案在性能和成本上已经无法满足实际的需求,100G传输系统逐步被大家认可和接受,而此系统对PCB传输信号速率的要求也从1G、3G提升到10G、25G。

当信号沿着PCB线路以超过1Gbps的速率传输时,此时的信号通路应视为有损传输线模型,其中电磁能量一般以五种形式损失:辐射损耗、耦合到邻近的线条上、阻抗不匹配、导线损耗和介质损耗[5]。阻抗不匹配、导线损耗和介质损耗是传输线上信号衰减的主要贡献者,为在完整的背板链路中实现10Gbps+甚至于25Gbps+的长距离传输[通道总长度通常从508 mm(20 in)到1016 mm(40 in)不等],PCB板厂必须严格控制阻抗并确保无源通道的信号完整性,以减少趋肤效应损耗、介质损耗、串扰和反射。这就要求PCB厂更多地关注线路形状、布线方式、通孔结构、焊盘形状、介质材料的选择以及铜箔粗糙度等对信号传输的影响,诸如更先进的布线方式、更多埋盲孔、更低损耗的无卤基材、更低轮廓的铜箔、先进半导体封装方式、标准化的SERDES以及更多均衡、预加重等措施[1]。 关于布线方式、产品图形设计、阻抗匹配及PCB相关的各种加工精度,如线宽、介厚、层偏等,部分是客户设计相关的,部分是PCB加工一直研究和管控的,本文主要从孔的损耗上进行研究,也就是从减少孔STUB方面进行研究和阐述。

2 背钻技术

传统多层板各层间一律采PTH做为互连工具。例如某8层板之某通孔仅执行L1与L4的互连时,所多出的孔壁称为Stub。Stub越长寄生电容愈大而插入损耗S21也愈严重。

然而由于STUB本身的电感,以及信号孔与接地孔两者之电容,另加上下两孔环间的电容,均将严重影响到信号完整性。STUB若经扩孔背钻掉而消除其共振后,则其插入损耗将可大幅降低,如图1。

图1 插损与STUB关系示意图

以一款14层板的为例进行仿真,走线方式为1、3层换层走线,设计不同的背钻深度,得到对应插损表现如图2。

图2 插损与STUB关系仿真图

由图示看出仿真得出的不同的背钻深度即STUB长度,会产生不同频率的谐振点,谐振频率越高,代表此系统可传输的信号速率越高;通过表1可知,实现10 GHz的速率传输至少需要STUB长度控制在0.30 mm(12 mil)以内。

表1 谐振频率与STUB长度的对应关系表

目前背钻的设计由原来的通孔孔径0.5 mm以上逐步缩小到0.2 mm,随之背钻难度也大幅度提升,主要体现在孔径变小、背钻时排屑困难导致堵孔,随着高速高频材料的越来越广泛化使用,小孔背钻成为不可或缺的加工工艺,所以此问题也需要得到快速有效的解决。

2.1 实验方案

设计实验方案如下

(1)试验板件选择为小孔背钻板件;加工机台选为Schmoll机;

(2)板件加工参数选为BDR参数(背钻专用加工参数);

(3)板件加工时注意断钻、缠丝问题,加工完毕后保留钻头,观察钻头磨损及崩缺情况;

(4)采用三种钻头进行验证且对孔位精度进行验证;

(5)板件加工完毕后,做好标识,按照正常流程向后转工;

(6)板件在蚀刻后按照标识的指定位置取切片观察孔壁质量;

(7)板件加工方案如表2。

表2 加工方案

2.2 实验现象与结果

加工完成后观察钻头磨损、断钻及缠丝情况,并统计背钻堵孔比例、测量背钻孔位精度。

表3 钻头磨损、断钻及缠丝结果

表4 背钻堵孔比例

表5 背钻孔位精度

2.3 试验分析

(1)钻头结构:①目前我司常备钻头,钻尖角130°,螺旋角为40°,芯厚为0.12,为UC型号钻头,排屑性能及刚性较好;②此钻头为UC改良型钻头,为加大排屑性特意减薄芯厚至0.03~0.05左右,排屑性能优秀,相对应刚性较差;③此钻头为UC改良型钻头,为改良排屑性能而减少芯厚至0.08~0.09左右,相应的刚性为之降低;

(2)钻头磨损量及断钻、缠丝:因此类钻头为背钻所用,所需切削的介质为锡、树脂、电镀铜,其中钻头最主要的磨损为切削电镀铜导致;对比以上三种钻头,芯厚越薄的钻头磨损量相对大,但加大了排屑槽空间的钻头缠丝会大幅减少。

(3)孔位精度及对位情况:从数据上分析,三种钻头在孔位精度上均可为满足我司要求,且从对位数据上分析,B型号钻头在对位上相对差一些,但也可满足40 μm以内,根据目前我司背钻孔径大于通孔150 μm,单边间距为75 μm,可以保证背钻孔无残铜现象。

2.4 小结

汇总试验结果如表6。

表6 背钻试验结果

通过对以上三种钻头进行对比测试,只有钻头C可以满足小孔背钻要求,目前已经实现批量稳定生产

3 跳孔技术

3.1 工艺介绍

跳孔设计即是了L1-L3的盲孔,盲孔孔径设计8 mil ~ 14 mil,实现L1-L3跨阶互联, 加工原理在普通盲孔工艺流程基础上增加跨阶激光钻孔、大盲孔电镀、大盲孔塞孔、盲孔POFV等工艺实现,此工艺替代两阶叠孔HDI并较少一次压合子板流程,可以极大减少一次压合流程成本实现L1-L3层跨阶互联;真空塞孔替代盲孔填平工艺降低电镀成本。此工艺既提高了局部的布线密度,增加的单板的信号容量,也在设计上进一步降低了成本,且此设计也可以看做是“0”STUB的设计,对高速率信号的传输实现了最低的损耗。

从加工工艺可分为含POFV工艺跳孔和不含POFV工艺跳孔两种工艺,含POFV工艺跳孔技术需要解决了(0.2 mm ~ 0.36 mm)大盲孔激光钻孔、真空塞孔+POFV、通盲孔电镀兼容、层间对位,等工艺难点;不含POFV工艺的跳孔技术需要解决了0.2 mm ~ 0.36 mm)大盲孔激光钻孔、通盲孔电镀兼容、层间对位,等工艺难点,但是此工艺表面凹陷较大;含POFV工艺跳孔技术,解决了(0.2 mm ~ 0.36 mm)大盲孔激光钻孔、真空塞孔+POFV、电镀兼容等方面。其优点主要有以下几点:此方案的优势是减少一次压合流程成本实现L1-L3层跨阶互联;真空塞孔替代盲孔填平工艺降低电镀成本。

3.2 工艺流程

跳孔工艺流程图如图3。

3.3 跳孔缺陷分析

3.4 塞孔缺陷分析

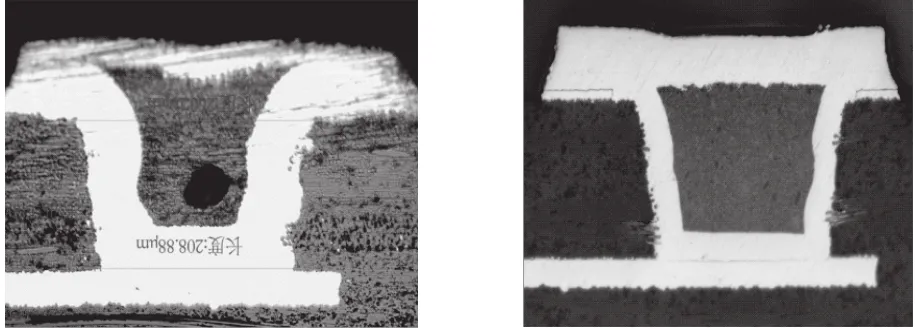

跳孔工艺塞孔使用普通丝印方式存在孔内气泡无法排除导致塞孔,采用真空塞孔可有效改善塞孔气泡凹陷问题。两种塞孔效果如图5。

图3 跳孔工艺流程图

图4 跳孔工艺底部残胶、偏盘缺陷图

图5 跳孔工艺丝印塞孔、真空塞孔

3.5 小结

跳孔工艺与与普通两阶盲孔叠孔工艺相比,可以,提高了PCB乃至电子产品的集成化程度,实现跨阶连接并且减少一次压合制作流程,降低PCB制作成本。

4 总结

本文主要介绍了两种减少孔损耗、即减少STUB的技术,随着的速率越来越快,此类设计的应用也会越来越普遍,背钻工艺将成为普遍设计,跳孔也会逐步在高端产品上应用。

韩雪川,技术专家,开始负责高速及HDI产品,并组建高速产品团队,并主导大尺寸单板、深微孔、哑铃孔产品及任意层互连HDI产品等多项产品技术的开发。

The research of loss for hole with high speed PCB above 100G

HAN Xue-chuan

This article made research from the perspective of reducing the loss of the hole to achieve a single PCB traces rate 100Gbit/s, breaking the back-drilling technology, jump-hole technology, effectively ensuring the 100G high-speed backbone network over the printed circuit board technology.

100G; High Speed; Loss; Back Drill; Skip Via

TN41

:A

1009-0096(2015)03-0017-05