基于FPGA的TMS320C6678 DSP的电源和时钟设计

2015-01-25施庆展袁乃昌

施庆展,冯 起,罗 慧,袁乃昌

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

作为高性能多核信号处理器的代表,TMS320C6678 DSP在导弹制导,医学成像,测控与自动化以及高性能计算方面取得了广泛的应用。单核处理速度达到1.25 GHz,八核同时工作时的处理速度可以达到10 GHz。定点运算处理能力40 GMAC,浮点运算处理能力20 GFLOP[1]。基于以上优良的性能以及超高的信号处理速度,这使得对于TMS320C6678 DSP系统的硬件和软件设计都提出了较高的要求。作为系统正常工作的前提,TMS320C6678 DSP的上电时序以及精确的时钟控制尤为重要。错误的上电时序或不精确的时钟输出可能造成芯片的损坏以及错误的时序逻辑操作,从而造成无法预料的后果。

目前,FPGA作为现代集成电路设计验证的主流技术,其最大的特点是具有现场可编程特性,是硬件系统设计中不可或缺的设备之一。FPGA芯片具有丰富的IO资源、灵活的编程操作、精确的时序控制以及强大的信号并行处理能力[2],这使得其作为TMS320C6678 DSP的上电和时钟控制时具有其它器件无法比拟的优越性。因此,基于FPGA的电源和时钟系统设计具有很大的可行性,并预期会得到理想的结果。

1 系统硬件设计

1.1 TMS320C6678 DSP的上电时序

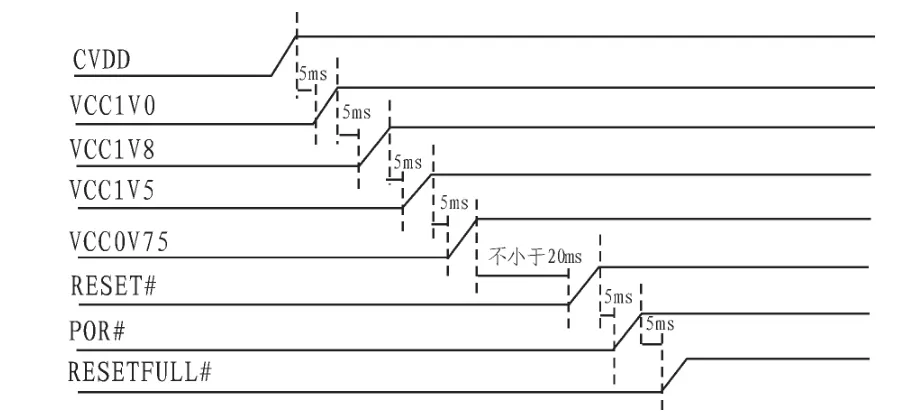

由于TMS320C6678 DSP具有不同功能的逻辑模块,各个模块的电源电压不尽相同,为了有效且适当的启动TMS320C6678 DSP芯片,各个的模块的电源启动时序有一定的要求。另外,输入的时钟信号在电源稳定前必须保持在高阻状态,否则会造成芯片的损坏[3]。TI公司提供了两种TMS320C6678 DSP芯片的上电时序解决方案,一种是内核先于IO的上电顺序,另一种是IO先于内核的上电时序解决方案,图1给出的是内核先于IO的上电时序图。

图1 内核先于IO的上电时序图Fig.1 Core-before-IO power sequencing diagram

TMS320C6678 DSP的上电初始化分为两个阶段。第一个阶段是从第一个电源上电开始到最后一个电源上电结束,第二个阶段是POR#和RESETFULL#两个复位信号的释放,这两个复位信号相继释放后完成芯片的上电初始化过程[2]。输入时钟是在1.8 V的电源上电完成之后开始进行配置,配置完成后再继续完成后续的上电过程。

1.2 硬件电路实现

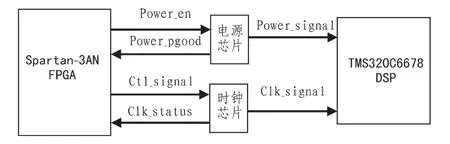

FPGA作为电源和时钟管控的核心,控制着DSP电源的上电时序以及时钟的配置和输出,因此FPGA在硬件设计中起着非常重要的作用[4]。Xilinx公司的Spartan-3AN系列的FPGA不仅具有Spartan-3A系列的全部特性,而且Spartan-3AN芯片内部集成了Flash存储器[5],这就避免了另外在芯片外部为FPGA配置Flash存储器的麻烦,从而在一定程度上大大减少了布线密度及电路板面积,增加了系统设计的可靠性。图2是硬件电路功能框图。

图2 硬件系统功能框图Fig.2 Hardware system function diagram

FPGA通过控制电源使能信号来控制各个电源的上电顺序,通过检测Power_pgood信号来确定某个电源信号是否达到稳定状态。对时钟芯片的操作是通过SPI接口对寄存器进行配置,来产生需要频率的时钟信号并控制其输出使能。Clk_status是用来检测输出时钟信号状态的,当其为高电平时表明输出时钟已经达到稳定。产生的各种电源和时钟信号直接连接到DSP的电源管脚和时钟管脚,通过DSP的SYSCLKOUT引脚测出的输出信号的频率可以来检测芯片是否正常工作。

2 软件实现

FPGA对整个系统的控制主要包括两部分:电源控制和时钟控制。系统软件的设计其实就是要满足各个电源上电的时序要求,硬件电路设计完成之后,相应的软件设计也就随之完成了。软件设计的关键是精确的上电时序控制以及对时钟芯片寄存器的配置。图3给出的是软件设计的流程图。

图3 软件设计流程图Fig.3 Software design block diagram

系统上电后,FPGA首先开始工作。根据DSP各个不同功能模块的上电时序要求,FPGA对不同的电源芯片进行使能控制。FPGA首先使能CVDD的输出控制信号,然后检测CVDD_pgood信号的状态,当检测到CVDD_pgood为高时,延时一段时间,然后再去使能下一个需要上电的电源芯片的输出控制信号,依此流程完成TMS320C6678 DSP上电。时钟信号的配置是在电平上电过程中完成的,当VCC1V8的电平输出稳定后,FPGA开始配置时钟芯片,当需要时钟信号输出稳定后,FPGA继续完成其它电源的上电。

3 仿真与测试结果

3.1 FPGA对时钟芯片的配置

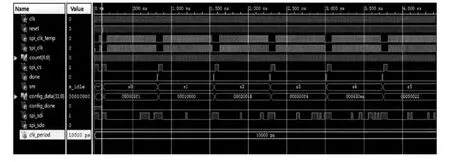

在进行设计时,FPGA对时钟芯片的配置是通过SPI的方式进行的。首先外部输入的50 MHz的系统时钟经过十分频后作为SPI通信的基准时钟。一次SPI通信的数据信息格式是32位,数据的最高有效位是R/W信号,为1时表示FPGA对时钟寄存器进行读操作,为0表示FPGA对时钟寄存器进行写操作。30至27位是保留位,26至16位表示所要操作寄存器的地址,低16位表示数据信息[6]。图4是SPI通信仿真结果。

图4 SPI仿真结果Fig.4 SPI simulation result

由于本设计主要是产生系统所需的时钟信号,所以对寄存器进行的是写操作。在SPI_CS信号有效之后,在下一个时钟的上升沿开始进行数据的写入,每位数据的写入都是在时钟的上升沿完成的。一次SPI通信结束时,done信号被拉高并保持一个时钟周期的高电平,然后SPI_CS信号置为无效,一次SPI通信完成。然后接着进行下一次的通信。FPGA对整个时钟芯片的寄存器配置完成后,config_done信号被拉高并一直保持。图4的仿真结果证明该通信是可行的。

3.2 测试结果分析

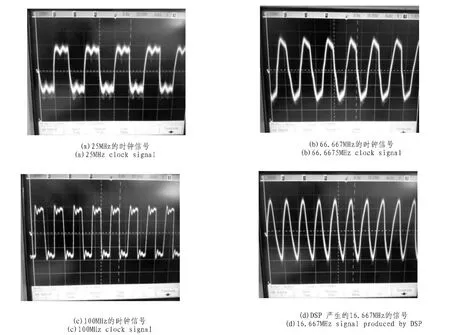

将上面仿真设计好的程序烧到FPGA的Flash中,然后对整个设计系统进行测试。系统上电后,测量时钟芯片的输出时钟和TMS320C6678 DSP的SYSCLKOUT引脚的输出时钟,以此来判断上电控制和时钟控制两部分功能是否完美实现。 用示波器观察的结果如图 5 中(a)、(b)、(c)、(d)所示。

从上图(a)、(b)、(c)的测试结果可以看出,FPGA 对时钟芯片的配置结果是正确的,能够得到系统所需要频率的信号。图(d)的测试结果表明DSP的电源和时钟配置都是正确的,只有上电时序以及输入的时钟信号正确DSP内部才能产生16.667 MHz的信号出来。测试结果表明该系统的硬件和软件的设计方案是合理可行的。

4 结束语

图5 测试结果Fig.5 Test results

文中针对高性能信号处理器TMS320C6678 DSP芯片的电源和时钟设计提供了一种比较有效的解决方案。软件仿真和最终的硬件系统测试结果都验证了设计方案的可行性,并得到了比较理想的效果。该系统设计方案设计灵活,易于修改,适应性强,可以移植到任何包含TMS320C6678 DSP芯片的系统平台上,为TMS320C6678 DSP的广泛应用提供了保障。

[1]TI.TEXAS INSTRUMENTS.TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor Data Manual[EB/OL].(2013).http://www.ti.com/product/tms320c6678.

[2]林英撑,童晓华,刘向宇.FPGA嵌入式系统设计与开发指南[M].北京:中国电力出版社,2012.

[3]TI.TEXASINSTRUMENTS.Hardwae Design Guide for Key-Stone Devices[EB/OL].(2011).http://www.ti.com/product/tms 320c6678.

[4]吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010.

[5]Xilinx.Spartan-3AN FPGA Family Data Sheet[EB/OL].(2011).http://www.xilinx.com/support/documentation/data_sheets/ds557.

[6]TI.TEXAS INSTRUMENTS.CDCM6208 DataSheet[EB/OL].(2014).http//:www.ti.com/product/cdcm6208.