电子提花机花型传输及存储系统设计

2015-01-04江慧娜王一钧王淑鸿孙慧瑜

江慧娜,王一钧,王淑鸿,孙慧瑜

(北京石油化工学院 信息技术教学与实验中心,北京 102617)

提花机是实现织物经纱提升控制的装置,通过控制经纱提升与否从而形成织物图案。传统的机械式提花机需要将设计好的图案变成控制织机的纹版,而纹版通常采用由冲压机在硬纸板上打孔来存储数据的方式获得,该环节非常耗时且会造成纹版的大量消耗。电子提花机则取消了纹版的制作过程,可根据由纹织CAD软件设计出的代表织物花型的数字化处理文件控制相关经纱的动作,配合提针结构实现高速无纹版提花功能。相对于机械式提花装置而言,电子提花装置可显著提高生产效率[1-2]。在电子提花机中,需要将上位机设计的花型数据文件写入到控制器中,花型数据的正确写入和有效存储决定了提针机构能否完成预定花型编织功能。本设计选用STC公司生产的8位低功耗高性能CMOS微控制器STC89C52RC作为主控芯片[3],采用串行通讯和FLASH存储实现主控制器与上位机间的花型数据传输及存储,能够满足提花机生产过程中花型数据的可靠传输及存储要求。

1 总体设计

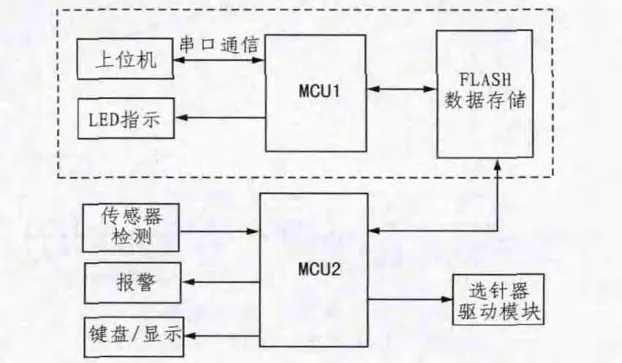

电子提花控制系统总体构成如图1。图中虚线框内即为花型数据传输及储存模块,MCU1处理器采用串行通讯方式将上位机设计好的花型文件写入FLASH存储模块,生产过程中MCU2处理器读取FLASH存储模块中花型数据,再根据该数据文件控制选针器驱动模块,有选择地驱动电磁阀线圈,电磁阀吸,则经纱提升;电磁阀不吸,则经纱不提升。织机据此即可根据花型数据文件所提供的信息织出所需的提花花型,完成整个提花织造过程。本设计将针对图1所示虚线框内花型数据传输及存储部分的软硬件设计实现进行介绍。

图1 提花机控制系统框图Fig.1 Structure diagram of the control system in jacquard machine

2 系统硬件设计

花型数据传输及存储系统硬件部分主要由单片机模块、RS232串口通讯电平转换模块、FLASH存储模块及其他辅助部分电路组成。

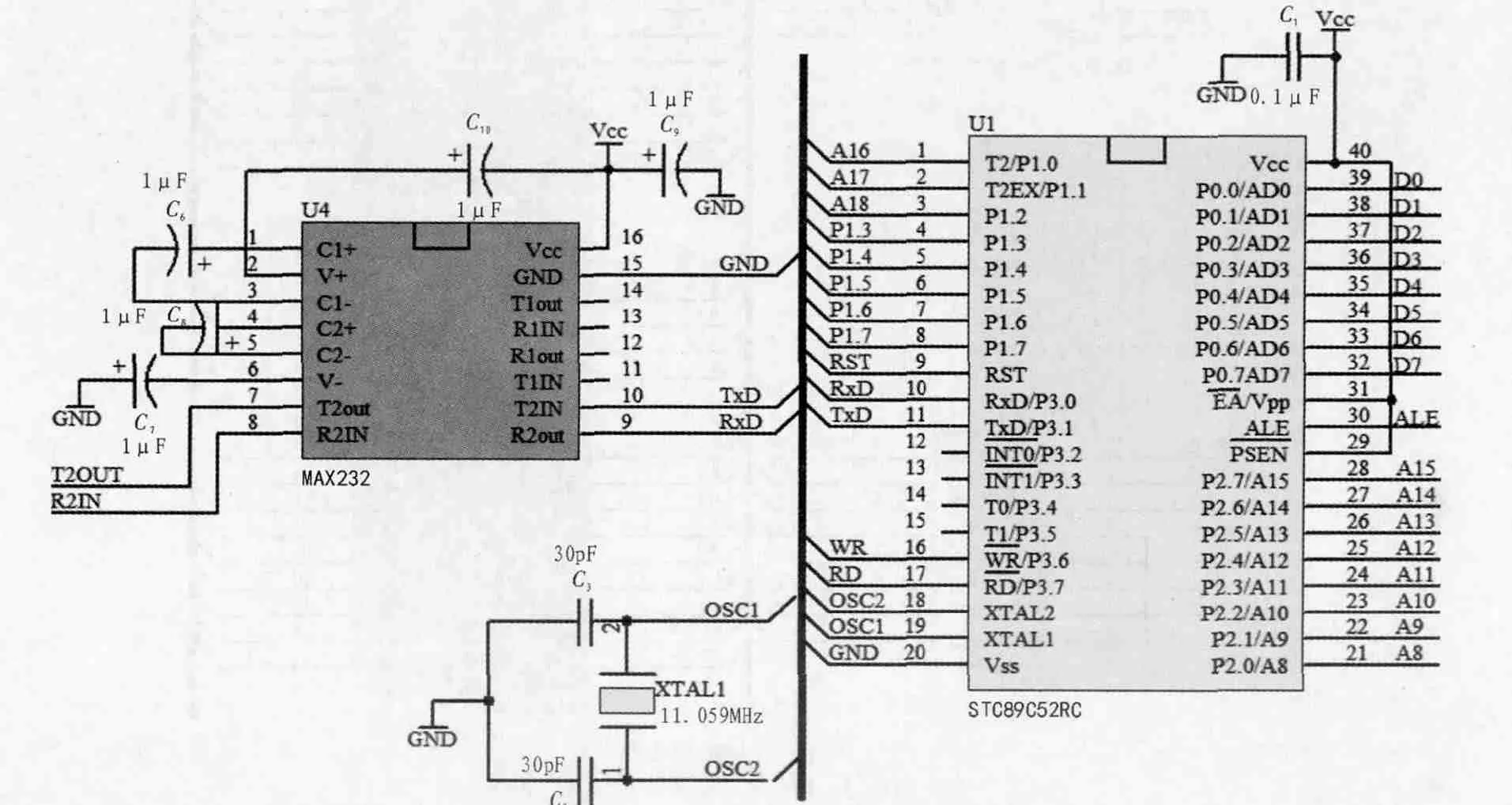

2.1 电平转换及单片机部分电路

本设计中单片机选用8位低功耗高性能CMOS微控制器STC89C52RC,在实现单片机与上位机之间的串行通讯时,由于单片机给出的信号TXD/RXD为TTL电平,而上位机端串行通讯口为RS232电平,故需采用MAX232芯片实现两者间的电平转换[4]。由于RS232电平较高,接通时产生的高瞬时电涌可能会导致芯片损毁,所以在使用中应尽量避免热插拔。

2.2 Flash存储模块电路

图2 RS232电平转换及单片机部分电路Fig.2 RS232 level conversion unit and microcontroller unit circuit

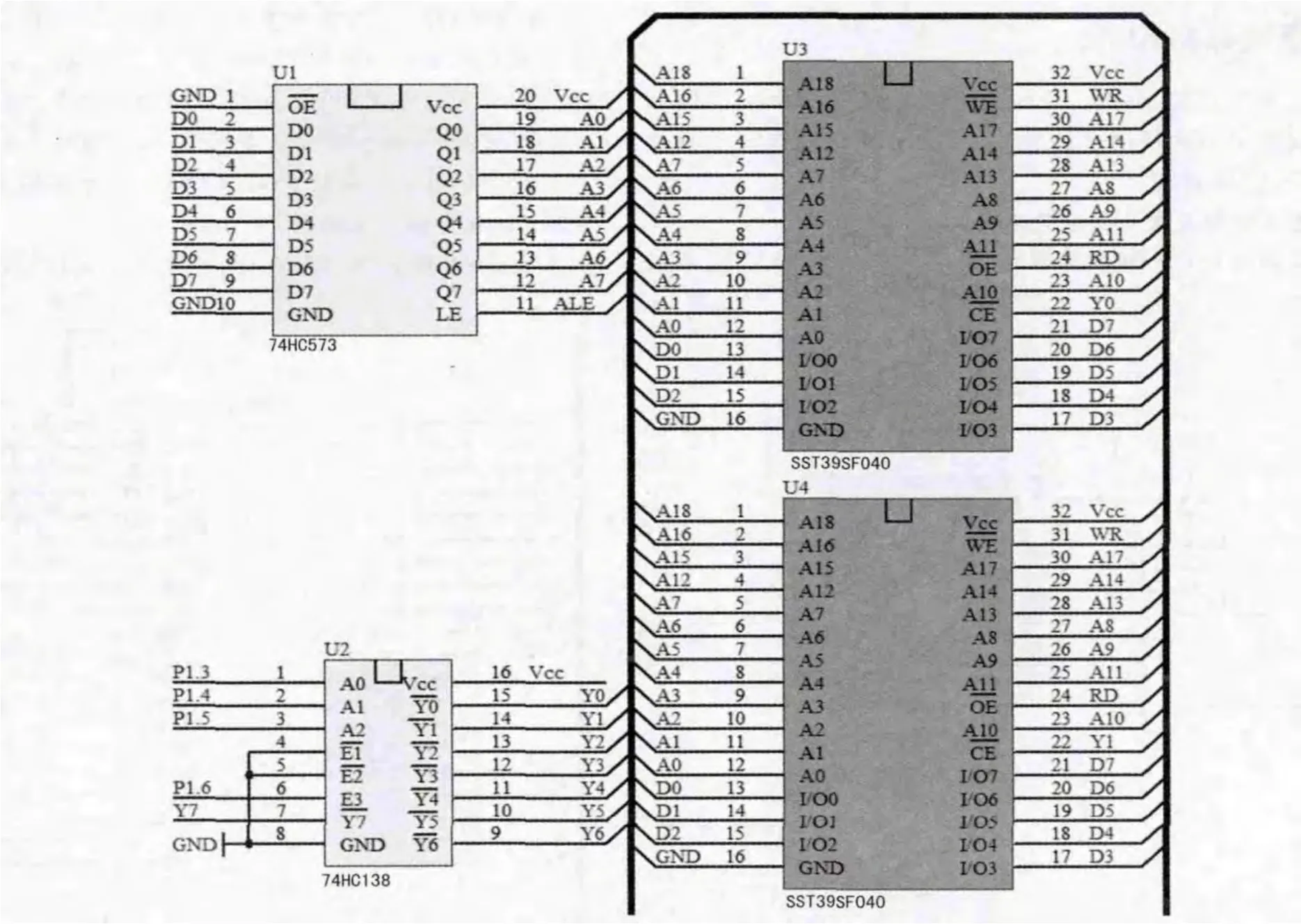

Flash存储器具有低功耗、容量大且速度快的优点,同时也具备很强的电磁抗干扰能力与抗震能力[5],因而在嵌入式开发领域里作为数据存储设备得到广泛应用。在本设计中花型数据文件的存储也采用非易失性 Flash存储器来完成,由于其断电后信息不会丢失,使得系统再次开机后可不需要经过上位机而直接从存储模块调出加工以方便生产。所选存储空间的大小由花型文件的经纱和纬纱数决定,根据提花机的实际工作需要,要求存储系统能满足约2MB的花型数据存储的生产要求,预留一定的扩展升级空间,拟定存储系统存储空间为4MB。综合考虑存储器读取速度,稳定性以及经济型指标,选择SST公司推出的基于SuperFlash技术的NOR Flash系列存储器SST39SF040作为存储芯片,该存储器属于并行闪速存储器系列,适用于需要程序在线写入或大容量、非易失性数据重复存储的场合。由于该存储器单片容量为512KB,故本设计中采用8片SST39SF040以满足4MB的存储空间需求。

由SST39SF040存储器构成的存储模块驱动电路如图3所示(图中仅给出两片SST39SF040的接口电路),当需要进行花型存储时,单片机将控制信号P1.6置高,使能译码器74HC138输出,控制信号P1.3~P1.5的译码输出结果Y0~Y7控制八片SST39SF040的片选端CE,选择指定Flash存储器进行读写操作。STC89C52RC单片机的数据端口P0、读写控制端口WR/RD可直接与SST39SF040的相对应端口直接相连。至于地址端口,由于该Flash存储芯片容量为512KB,对应地址线为19位,超过了单片机的可寻址范围,设计中单片机采用P1.2~P1.0作为页面地址选择位与存储器的高3位地址端口A18~A17连接,同时由于该型单片机数据端口和地址端口低8位为复用端口,故在发送数据之前须用74HC573芯片将低8位地址锁存。

3 系统软件设计

系统软件设计部分主要包含单片机Flash存储读写程序实现、串口通讯实现以及上位机软件界面设计。本文主要介绍Flash存储读写及上位机软件界面设计实现。

3.1 单片机读写Flash软件实现

3.1.1 SST39SF040存储器指令序列

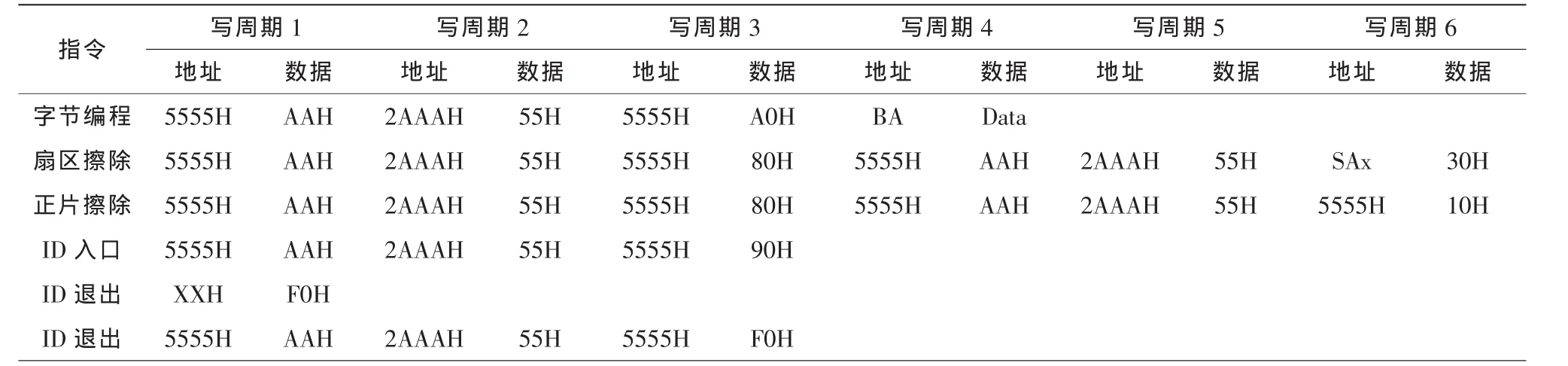

SST39SF040的软件指令包含普通读指令和命令指令两大类。普通读指令与RAM的读操作类似,当OE和CE信号同时为低电平时,即可从芯片读取数据;芯片命令指令包括芯片ID识别、字节编程、扇区擦除以及整片擦除等。所有这些操作均可由如表1所列的软件指令序列来实现,其中BA为待编程字节的地址,Data为字节编程数据,SAX为待擦除扇区的地址。所有指令中地址位只有低15位有效,高4位可任意设置[6]。

图3 存储模块驱动电路Fig.3 Driver circuit of storage unit

SST39SF040的软件操作命令序列实际上是由一个或多个总线写操作组成的。以SST39SF040的扇区擦除为例,其操作过程包括3个步骤:首先开启擦除方式,用表1中给出的第1至第5周期的总线写操作来实现;然后装载扇区擦除命令(30H)和待擦除扇区的地址,用其对应的第6周期的总线写操作来实现;最后进行内部擦除,擦除时间最长为25 ms。

表1 SST39SF040存储芯片软件指令序列Tab.1 Software instruction sequence of storage chip SST39SF040

3.1.2 SST39SF040存储部分软件设计

SST39SF040存储部分软件设计主要工作为编写单片机对该Flash存储的操作功能实现代码,包括ID读取、扇区或整片擦除以及字节编程等。下面给出用C语言实现的ID读取程序代码,其他操作功能代码可参照表1中软件指令序列编写。

//读FLASH ID的函数,

//入口参数:FLASH的manuf_ID及device_ID,出口参数返回1或0

uchar Read_Id(uchar manuf_ID,uchar devi_ID)

{

Sst39vf040_Ce=1;

XBYTE[0x5555]=0xAA;

XBYTE[0x2AAA]=0x55;

XBYTE[0x5555]=0x90;

manufacturer_id=XBYTE[0x9000];

device_id=XBYTE[0x9001];

if((manufacturer_id==manuf_ID)&&(device_id==devi_ID))

return 1;

else

return 0;

XBYTE[0x5555]=0xAA;

XBYTE[0x2AAA]=0x55;

XBYTE[0x5555]=0xF0;

Delay10us();

Sst39vf040_Ce=0;

}

3.2 上位机软件设计

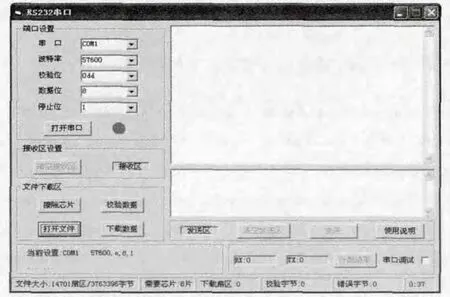

上位机软件设计的主要功能为将纹织CAD软件生成的花型文件通过串口通讯的方式将文件传输至单片机,与此同时,为保证数据传输的可靠性,要求对写入到Flash存储器中花型数据进行校验。上位机程序采用C#语言编写,该程序中可使用 MSComm(Microsoft Communication Control)控件与单片机通信[7],设计出的上位机软件界面如图4所示。

图4 上位机软件界面Fig.4 Interface chart of the control system

为了提高生产效率,必须在保证花型数据的正确传输和可靠存储的同时尽可能缩短数据传输及校验环节总体时间。为避免因个别字节数据传输错误导致校验失败而须重新写入所有数据的情况,程序设计中采用分批传送和传送过程中增加CRC校验字节的方式来保证数据有效性。具体实现方式为:当启动写入程序时,首先将读取到的花型文件按照99个字节一组进行拆分后存入指定的花型数组中,同时对每组数据进行CRC16校验,校验生成的字节也存入指定校验数组;文件分析及校验完成后,将由99个花型数据和1个校验字节数据传递给单片机,单片机接收到连续100个串口通讯数据后,对前99个花型数据也启动CRC16校验,将校验结果与传递过来的校验字节进行对比,结果一致则将该组花型数据写入Flash存储并给PC返回参数正确传输标志,要求进行下一组数据传输;反之则给PC返回数据传输失败标志,要求重新传送该组数据。

4 结论

设计的基于低功耗高性能CMOS微控制器STC89C52RC和并行闪存SST39SF040的电子提花机花型传输和存储系统,采用串口通讯方式实现了与上位机的数据交互,并通过数据分段传输和增加CRC校验的方式保证了数据的可靠传输和正确存储。该花型数据传输和存储系统配合主控制器在某型电子提花机上的使用结果表明,该存储系统工作可靠,能够满足实际应用需求。

[1]李祥.电子提花技术与产品开发[M].北京:中国纺织出版社,2000.

[2]蔡重凯.基于ARM的电子提花机控制器设计[D].杭州:浙江大学,2006.

[3]何伟刚,吴其琪.煤矿井下小型无线定位器的设计[J].煤矿机械,2013,34(10):154-156.HE Wei-gang,WU Qi-qi.Design of small coal mine wireless locator[J].Coal Mine Machinery,2013,30(10):154-156.

[4]向红军,雷彬.PC与便携式仪表的串行通讯及数据处理程序设计[J].电子测量技术,2007,30(1):20-22.XIANG Hong-jun,LEI Bin.Design of serial port communication and data processing between PC and portable meter[J].Eelectonic Measurement Technology,2007,30(1):20-22.

[5]郑文静,李明强.Flash存储技术 [J].计算机研究与发展,2010,47(4):716-726.ZHENG Wen-jing,LI Ming-qiang.Flash storage technology[J].Journal of Computer Research and Development,2010,47(4):716-726.

[6]万方,汪世明.大容量NOR Flash与8位单片机的接口设计[J].单片机与嵌入式系统应用,2007(8):25-27.WAN Fang,WANG Shi-ming.Design of Interface between large capacity NOR flash and 8-bit microcontroller[J].Microcontroller&Embedded System,2007(8):25-27.

[7]章辉,叶建芳.基于MSComm控件串口通信的实现[J].电子测量技术,2011,34(8):126-129.ZHANG Hui,YE Jiang-fang.Realization of serial communica based on MSComm controls[J].Eelectonic Measurement Technology,2011,34(8):126-129.