35 kV数字变电站合并单元模拟信号采集卡研究

2014-12-18彭地卓徐学军

彭地卓,徐学军,,汤 沁,李 骥

(1.长沙理工大学物电学院,湖南长沙 410004;2.长沙理工大学计通学院,湖南长沙 410004)

近年来,为贯彻落实智能电网“十二五”专项规划,变电站作为智能电网的关键支撑点,其智能化建设得到快速发展。与110 kV以上高压变电站智能化程度相比,35 kV变电站的设备数字化、系统智能化程度较低。目前在对35 kV变电站的数字智能化建设,主要是通过对旧站升级改造,完成数字化技术变电站的高性价比[1]。

由于原有35 kV变电站没有合并单元这一物理器件,而合并单元作为智能变电站过程层的关键环节,不可或缺。合并单元最早是在IEC60044-7/8中提出,合并单元统一同步接收汇总来自高压侧互感器的电流、电压数字信号,然后对多路电流电压信号信息进行处理,再按照规定的帧格式发送给保护测控装置[2-4]。对于传统电磁式互感器输出的模拟量电流、电压信息,合并单元同样能进行数据处理和组帧[5]。

合并单元和互感器之间接口规范目前有3种方案:(1)接收数字信号的合并单元,其接收发送都是数字信号的形式,满足数字化变电站过程层测控和采样的需求。(2)接收模拟信号的合并单元,其接收为模拟信号,是为兼容传统互感器信号而设计。(3)信号采集器与合并单元的组合,其首先将所有数据统一接收后再发送给合并单元。

本文依据合并单元设计要求,结合35 kV变电站互感器存在的情况。对合并单元前端数据进行预处理,设计模拟信号采集卡对来自互感器的模拟信号采集转换,给出一种具体的实现方案。

1 模拟信号采集卡方案

根据35 kV变电站的特点和国内智能变电站的发展现状,35 kV智能化变电站会长时间处于电子式互感器和传统电磁式互感器共存的阶段[6]。这就要求合并单元既能接收电子式互感器的电流电压信号,也能接收传统电磁式互感器的电流电压信号。以南瑞继保PCS-9250-LAV电子式电压互感器和PCS-9250-LAC-35L电子式电流互感器为例,其信号输出类型为模拟小信号,保护用电流输出为225 mV,测量用电流输出为4 V,电压二次输出为4 V。传统互感器信号输出类型为模拟信号,其测量用电流与电压二次侧输出分别为5 A和100 V。

对于低压电子式互感器,互感器的输出信号并不是直接的数字信号,所以对35 kV变电站互感器的数据采集,需要设置两个输入模块:一是接收传统互感器的大电流大电压的模拟信号;二是接收电子式互感器的模拟小信号。

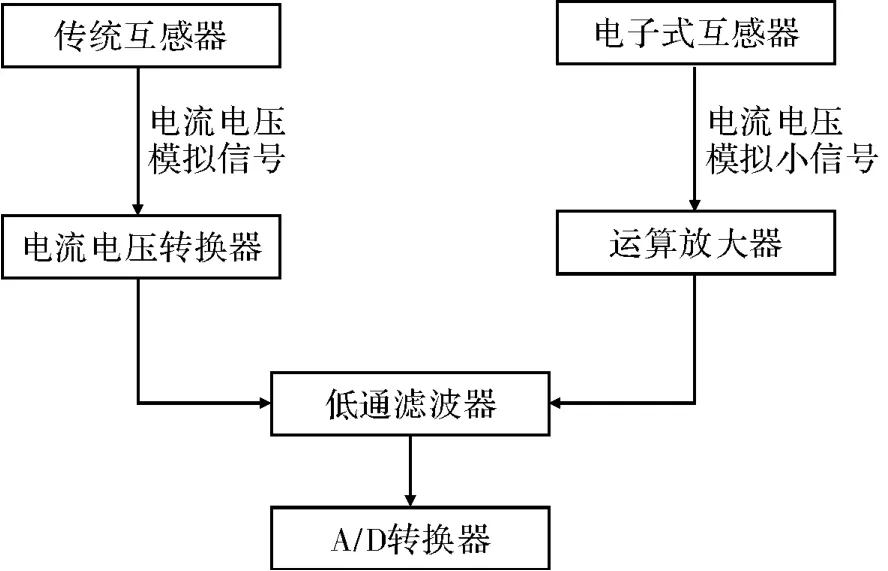

模拟信号采集卡原理上分为电压电流转换模块、低通滤波模块和A/D转换模块3个部分[7]。模拟信号采集卡的系统框图如图1所示。

图1 模拟信号采集卡的系统框图

2 模拟信号采集卡硬件设计

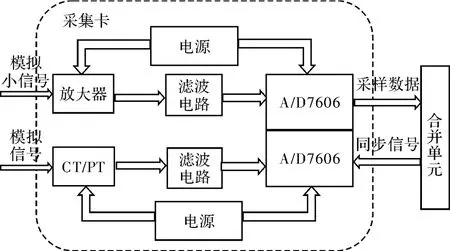

模拟信号采集卡可根据工程实际情况,既可作为合并单元的前置处理部分,也可作为合并单元的数据接收部分,其模块可分为电源模块、电流电压转换模块、低通滤波模块和A/D采样模块。模拟信号采集卡功能结构框图如图2所示。

图2 模拟信号采集卡功能结构框图

2.1 电流电压转换模块

电流电压转换模块的功能是将来自互感器的电流电压信号,接收转换成后续硬件平台A/D转换输入量程范围内的电压信号。如上文所述,传统电磁式互感器的二次额定输出信号为5 A和100 V,电子式电流互感器的二次额定输出200 mV。这些输入信号范围都不在A/D转换芯片输入量程,故需要先将信号转换成A/D芯片的量程范围。模拟信号采集卡的A/D转换采用6通道AD7606芯片,其内部基准电压源为2.5 V,输入量程范围可选择为-10~+10 V。

对于传统电磁式互感器,设计采用湖北天瑞电子有限公司生产的电流电压互感器。检测用电压输出型电流变换器选用 TR0176-6C,在额定输入电流为100 A时转换输出为7.07 V;保护用电压变换器选用TR1142-1B,在额定输入为 100 V时转换输出为7.07 V。两种型号的二次侧转换电压均在A/D采样芯片的输入量程范围。

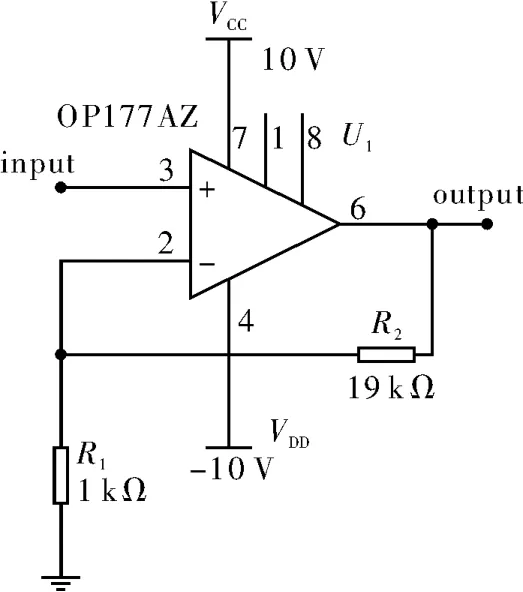

对于电子式互感器,设计采用ADI公司的超精密运算放大器OP177。该款芯片具有超低失调电压(TA=25℃:25μV(最大值))、出色的失调电压漂移(0.3μV/℃(最大值))、精度性能优越等特点,符合合并单元精度标准的数据接口采集卡的要求。由OP177芯片构成的放大电路如图3所示。

图3 OP177的放大电路

根据AD7606芯片的输入量程范围,结合式(1),在此,电阻R1和R2的取值分别为1 kΩ和19 kΩ。其电压输入输出放大倍数为20倍,将225 mV放大到4.5 V。

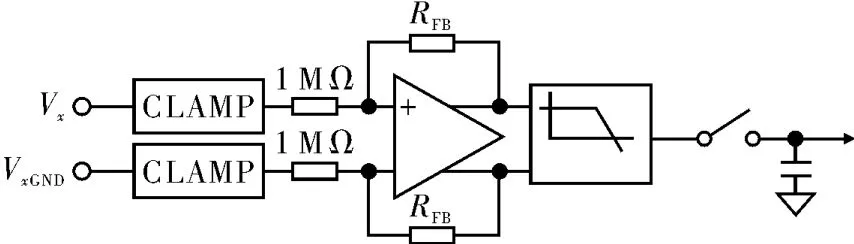

2.2 低通滤波电路

互感器所产生的电流电压模拟信号频率低、幅值小,在传输到合并单元时,易受外界因素的干扰,影响信号的精确性。故需要对信号进行滤波,避免干扰。本方案由于采用AD7606转换芯片,其内部提供了一个二阶抗混叠巴特沃斯滤波器,在±5 V范围内,-3 dB带宽值为15 kHz,图4为AD7606内部滤波器电路图。

图3中引脚3和6分别为输入输出端口,电阻R1和R2决定运算放大器的放大倍数,即

图4 AD7606内部滤波器

2.3 A/D采集电路

AD7606芯片是ADI公司的一款16位、8/6/4通道的同步采样的逐次逼近型模数转换器。内置模拟输入箝位保护、二阶混叠滤波器、跟踪放大器、灵活的数字滤波器、2.5 V基准电压源、基准电压缓冲以及高速串行和并行接口。所有通道均能以高达200 kSPS的吞吐速率采样。具有95.5 dB SNR。

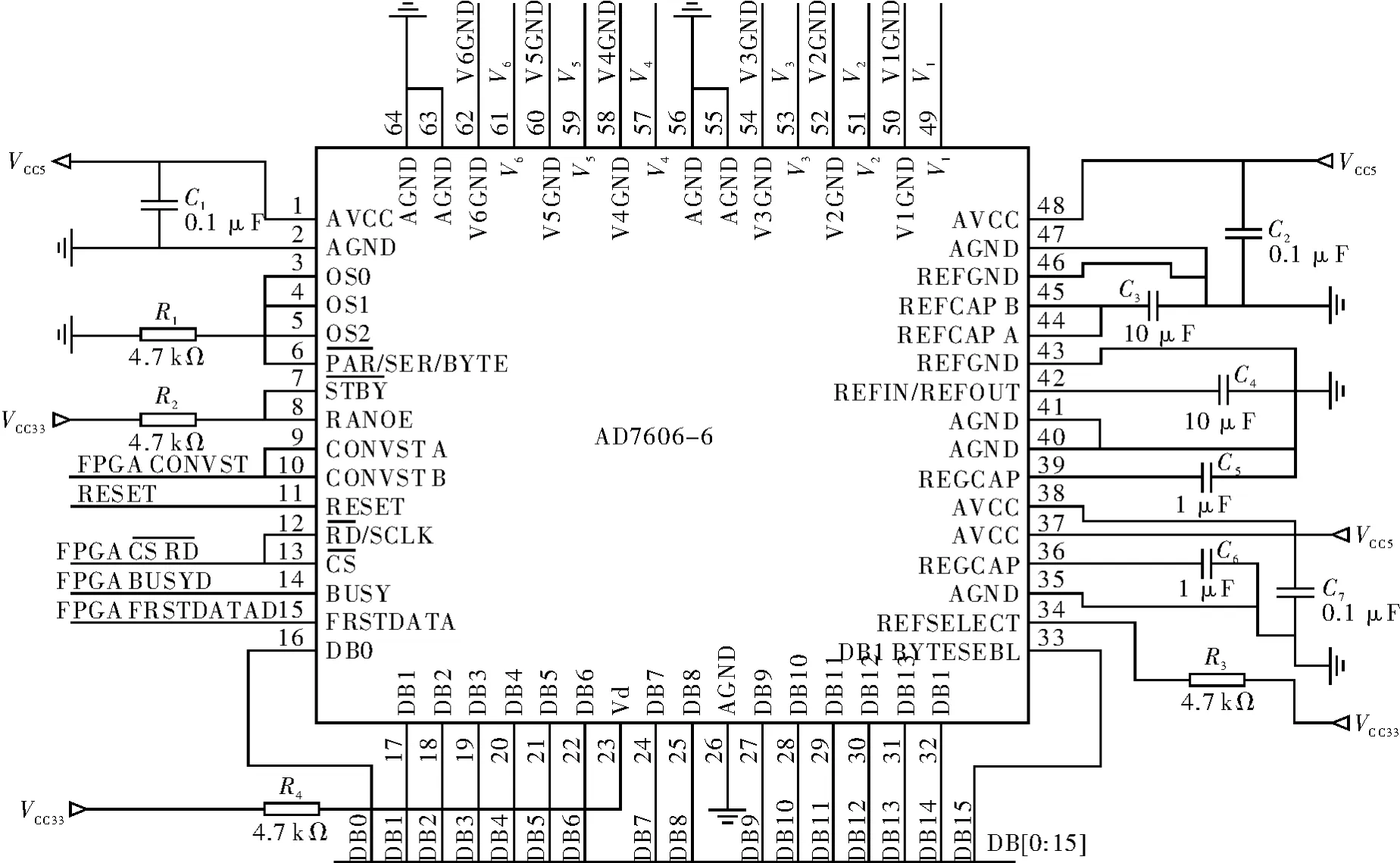

由于合并单元最多需要同步采集12路的电流电压信号,设计方案中选取两片6通道的AD7606-6芯片,能较好地满足智能合并单元所需要的分辨率和性能要求。AD7606的引脚配置如图5所示。

图5 AD7606-6引脚配置

以下是本方案中AD7606-6引脚设置几点说明:

(1)CONVST A、B引脚。AD7606-6的6个转换通道分为两组 V1、V2、V3和 V4、V5、V6,这两组通道由CONVST转换控制信号控制。当启动转换控制信号CONVST A时同步采样V1、V2和V3通道的模拟信号,当启动转换控制信号CONVST B时同步采样V4、V5和V6通道的模拟信号。当CONVST A或CONVST B引脚从低电平变为高电平时,相应模拟输入的前端采样保持电路被设置为保持。

(2)RANGE引脚。模拟输入通道的输入范围可由此引脚的极性决定。在前面的放大电路中,电流电压信号放大到±4.5 V或7.07 V,故此引脚需根据实际情况设置。与逻辑低电平相连,所有通道的模拟输入范围为±5 V。与逻辑高电平相连,所有通道的模拟输入范围为±10 V。

(3)PAR/SER/BYTE SEL引脚。此引脚为并行/串行/字节/接口选择输入。将此引脚与逻辑低电平相连,选择并行接口。互感器输出的数据DB[0∶15]将高速并行发送给合并单元。

(4)CS和RD/SCLK引脚。CS引脚为片选管脚;RD/SCLK引脚决定数据是并行或串行输入。此方案中,由合并单元数据接收器FPGA控制两个引脚逻辑低电平,选择并行输入模式下,使转换结果DB[0∶15]输出在并行数据总线上。

3 模拟信号采集卡结果

为验证方案的可行性,主要是对模拟信号数据采集卡的放大电路和A/D转换电路,验证是否满足合并单元的精度要求[8]。

3.1 放大电路验证

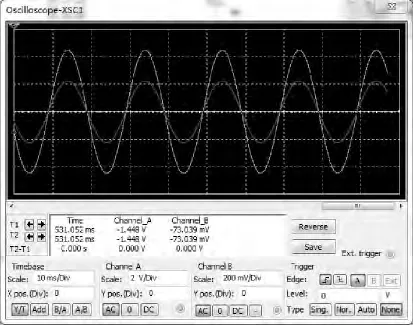

放大电路采用信号发生器产生一个50 Hz、峰值为225 mV的模拟电压初始信号。通过放大电路采用示波器观察期波形、用万用表测试其有效值。图6为放大器电路仿真的对比结果图。

Channel B通道为初始信号,Channel A通道为放大20倍的信号,万用表测试的有效值为3.182 V。由图可发现放大信号与初始信号波形保持一致未失真。

图6 放大器仿真对比图

3.2 A/D转换电路验证

A/D转换电路是在QuartusⅡ9.0环境下调试与验证的。由合并单元控制器FPGA同步接收A/D转换的数字信号。AD7606的读操作模式为相连的并行模式。图7为正电压并行模式时序波形图,图8为负电压并行模式时时序波形图。

图7 正电压并行模式时序波形图

图8 负电压并行模式时序波形图

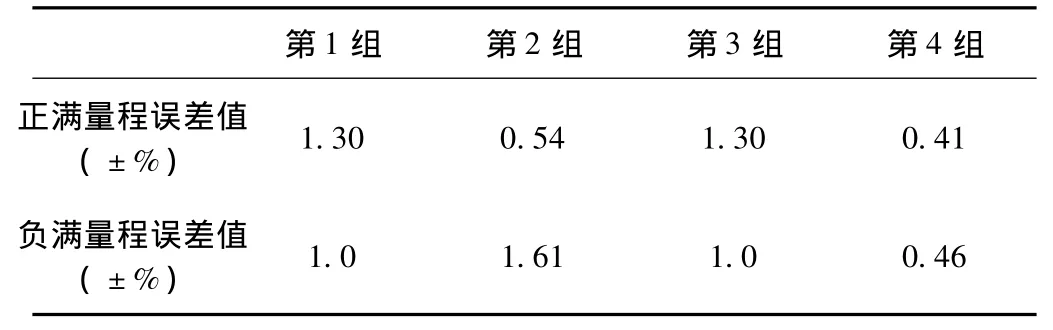

由图7和图8可知,在电子式互感器输出的电压信号放大到正负满量程4.5 V时,经过转换后,精度实验结果如表1所示。其误差均值分别为0.89%和1.02%,满足合并单元电压精度0.2等级。

表1 精度实验结果

4 结束语

本文对合并单元的前端数据处理部分,以模块化思路研究实现了模拟信号采集卡的设计。通过仿真验证,其工作稳定、转换速率快、输出精度高,满足合并单元数据采集的要求。同时,该采集卡既可作为合并单元的一部分,也可作为传统变电站就地数字化装置。模拟信号采集卡可以灵活应对35 kV变电站数字化的改造。

[1]张文静,朱能翰,郑佳.35 kV智能数字化技术变电站设计方案分析[J].科技创新与应用,2012(10):30.

[2]EVT.IEC6044 -7 Instrument transformers- part[S].USA:Electrical Voltage Transducers,2002.

[3]EVT.IEC6044 -8 Instrument transformers- part[S].USA:Electrical Voltage Transducers,2002.

[4]王伟明,段雄英.基于FPGA的电子式互感器智能合并单元研制[J].电力系统保护与控制,2012,40(2):131 -134.

[5]高翔.智能变电站技术[M].北京:中国电力出版社,2012.

[6]王振岳,陈伟,鹿海成,等.电子式与电磁式互感器的比较及在智能电网中的应用[J].华电技术,2012,34(2):1-5

[7]宋金浍,康怡,张旭,等.基于IEC61850标准中SCL的智能电子设备建模[J].电子科技,2012,25(9):21 -24.

[8]周春霞,李明,张维,等.针对500kV数字化变电站过程层采样的动模试验及若干问题探讨[J].电网建技术,2011,35(1):219-223.