基于FPGA的类曼彻斯特编码发送模块设计

2014-12-02顾涵

顾 涵

常熟理工学院物理与电子工程学院;江苏常熟 215500

0 引言

类曼彻斯特码是一种利用自同步法保持位同步的线路码型,它用上升沿来表示一个码元的开始,然后连续两个时钟信号的高电平表示“1”,对应编码数据“0100”,反之连续两个时钟的低电平表示“0”,对应编码数据“0111”。经类曼彻斯特编码后,无论是数据“1”还是数据“0”,在开始的时候都有一个上升沿,包含了时钟信息,正是具有这一特点,类曼彻斯特编码发送功能的设计实现解决了串行数据传输的同步时钟问题。

1 硬件设计

在硬件设计时采用LVDS 差分电路,LVDS 是一种低摆幅的差分信号技术,它使得信号能够在差分平衡电缆上以几百Mbps 的速率传输,其低压幅和低电流的驱动输出完全达到了低噪声和低功耗的要求。本设计中,FPGA 传出的串行数据通过差分电路的转换,形成差分形式的数据,向外传输,设计电路如图1 所示。

图1 发送模块

该电路临近输出端串接了10Ω 的电阻,可以防止差分线对短路,缺点在于420mV 的驱动电压已接近数据手册中给出的Vod 最大值454mV。同时设计中还需要考虑信号反射问题,这种现象的产生会导致噪声类型的转变,使其从原来的共模信号转变为差模信号,从而降低数据传输的准确性。为了避免这一问题,我们在设计中应做到在信号值不同时输出阻抗保持不变,同时,输出阻抗的下限只能稍小于传输线特性阻抗,而它的上限必须略大于传输线的特性阻抗。

2 软件设计

类曼彻斯特编码可以分为三步进行。第一步,检测编码周期是否开始并发送开始信号;第二步,对十五位数据进行类曼彻斯特编码;第三步,采用偶校验方式生成校验位,完成编码周期。具体编程时可以分为数据定义、数据转换及校验和数据编码及发送三大模块。

2.1 编码过程

当时钟的上升沿到来时,若复位信号有效则将数据位、校验位都清零,否则count_state1 加1。若count_state1 为011 则表示一个数据位传输的开始,传1 位数据,传送完该数据共经历四个时钟周期,在这四个时钟周期内count_state1共经历四个时钟周期的转换,其状态转换流程如图2 所示。

图2 count_state1 的状态转换图

2.2 数据定义模块

数据定义模块完成对输入输出信号的定义,具体程序为:

2.3 数据转换及校验模块

该模块采用状态机完成16 位并行数据到串行数据的转换,通过逐位异或运算来生成奇偶校验位,具体程序为:

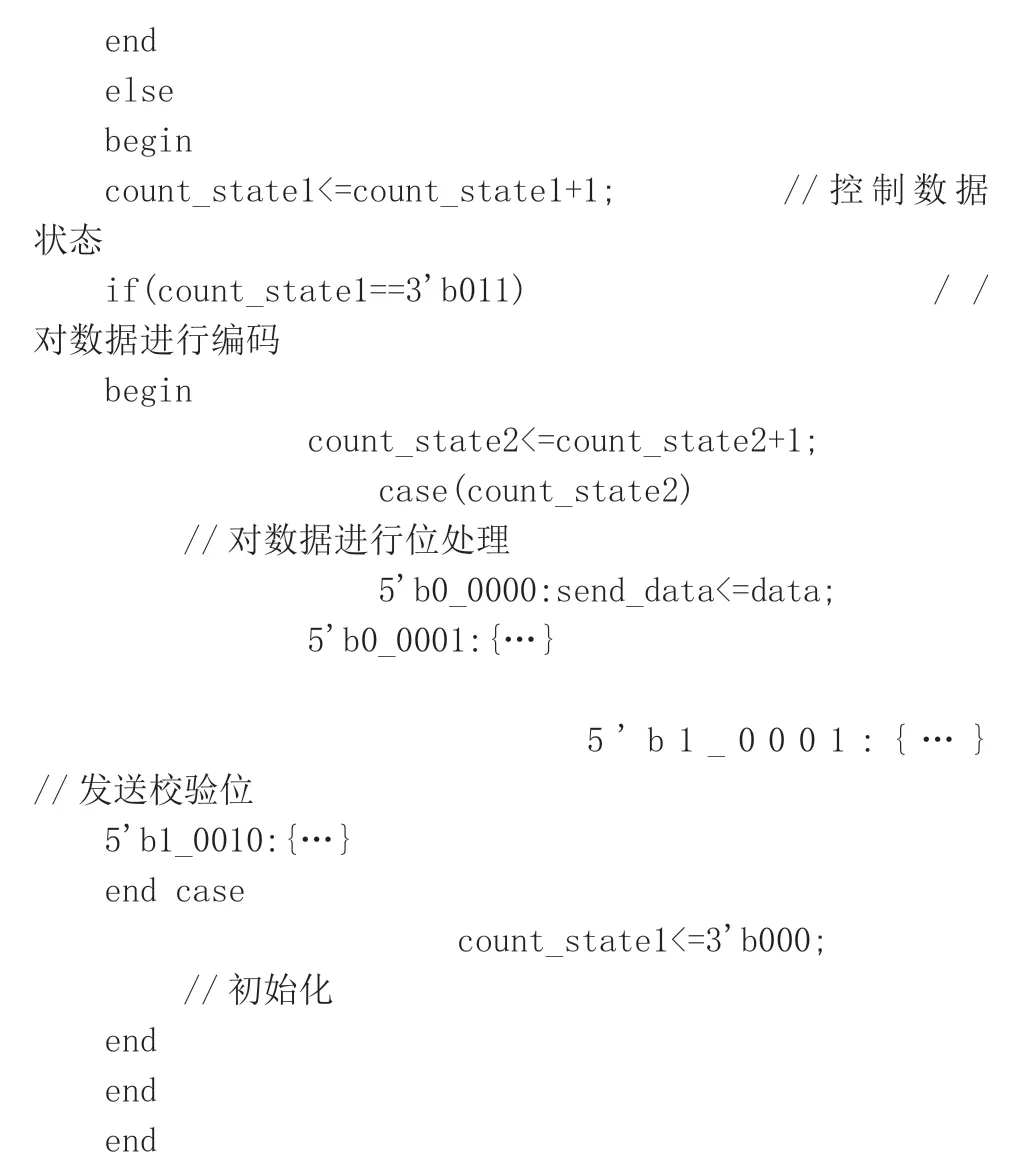

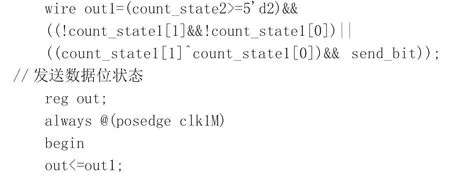

2.4 数据编码及发送模块

该模块对每一位数据进行编码并发送,具体程序为:

3 测试和仿真

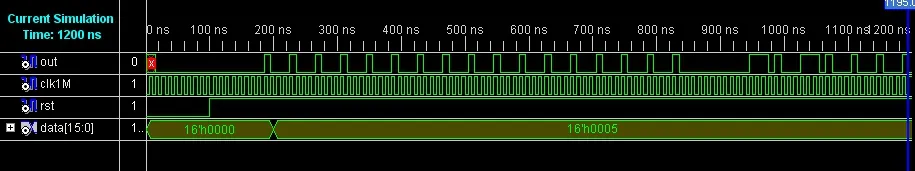

我们采用ISim 进行波形仿真来测试编码模块功能的准确性,以下给出了具体的ISim 测试程序,测试波形如图3 所示。从图中可以看出,当输入数据分别为0 和5 时,对应波形输出与类曼彻斯特编码规则相符,符合预期设计。

图3 编码仿真波形

[1]刘江海.EDA技术[M].华中科技大学出版社,2009.

[2]汉译西.EDA技术及其应用[M].北京航空航天大学出版社,2011.

[3]王晓聪.基于FPGA的HDB3码编码器优化设计与分析[J].现代电子技术,2011.

[4]黄仁欣.EDA技术实用教程.清华大学出版社,2010.

[5]肖娟.基于FPGA的移动通信中卷积码编码器设计[J].现代电子技术,2012.