用于激光告警的CAN总线通信技术

2014-11-30王志斌

李 芮,李 晓,王志斌

(中北大学山西省光电信息与仪器工程技术研究中心,山西太原030051)

0 引言

为研制用面阵探测器的具有高速峰值检测和实时判断功能的高性能激光告警接收机,需要设计一种新型激光实时探测原理实验系统:采用总线结构和通信协议,以面阵焦平面探测器为光电转换器,高速FPGA为信号处理单元,做到对激光信号的快速采集与并行处理,满足高速、实时的信号传输与处理技术的要求。

由于激光信号的特殊性,必须做到信号的实时采集,并且保证在采集数据的同时,可以对上一帧的数据进行处理。在处理数据的同时又要采集下一帧数据,并且实现激光告警。这就对电路的高速信号处理能力提出了要求,必须能够在很短的时间内完成上述操作,这些都是单片机无法做到的。而FPGA采用并行数据处理方法,能够达到系统的高速信号处理要求[1,2]。CAN总线是控制器局域网络,其节点数最多可达110个。目前CAN已经形成国际标准,并被公认为几种最有前途的现场总线之一[3,4]。因此,在本系统中采用FPGA处理输出结果通过CAN总线接口和计算机或者与其它微控制器相连,对其采集的数据进行监控。

本文将重点研究此系统中如何实现FPGA与单片机的CAN总线通信部分,将FPGA高速采集快速处理得到的激光信号的波长和方向等信息,经CAN总线传输给单片机,并且驱动单片机进行显示。

1 硬件电路设计

由于其工作时间相对较长,选用Altera公司的Cyclone II系列的低功耗处理器EP1C6Q240C8型芯片,提供185个IO接口。该芯片采用240脚的PQFP封装,拥有5980个Les。该芯片内部带有288K的ram和2个锁相环,可以保证高速运行时时钟信号的稳定性,有较强的数据处理能力。考虑到必须具有高抗干扰性、高信噪比、高可靠性,芯片采用贴片型240脚的PQFP封装形式。其晶振采用50Mhz,时钟周期为20ns,并引出15个I/O接口,分别用于控制CAN控制器控制信号d0-d7、reset、ale、cs、rd、wr以及电平转换芯片方向控制信号tr1、tr2。硬件电路如图1所示。

图1 FPGA节点硬件电路

1.1 CAN控制器电路设计

SJA1000是一款新型的CAN控制器,与PCA82C200 CAN控制器相比,它增加了一种新的操作模式——PeliCAN模式,能够自动完成CAN-bus协议的解析,常用于建立CAN设备的核心电路,被广泛应用在各种CAN电路设计中[5]。SJA1000内部具有8位并行地址/数据复用总线,有Intel和Motorola时序2种模式可供选择,在这里将SJA1000的MODE引脚拉高接到+5V,采用Intel时序。采用旁路CAN输入比较器,这主要用于SJA1000外接发送接收电路时,减少内部延时,使总线长度最大可能地增加。应将RX1引脚接到一个确定的电平,这里将RX1引脚接到CAN收发器的Vref引脚,将RX0、TX0引脚分别接到CAN收发器的RXD、TXD引脚,并将其TX1引脚悬空。由于FPGA不存在总线中断,故将其INT引脚悬空。具体电路图如图2所示。

1.2 CAN收发器电路设计

收发器是一种专用器件,用来完成CAN-bus物理层电信号的转换。在这里采用82C250作为CAN控制器与物理总线之间的接口。将其RS引脚 (斜率电阻输入端)接47K电阻后接地,用于降低射频干扰。在CANH和CANL之间需要接一个120Ω的总线阻抗匹配电阻[6]。具体电路图如图3所示。

图2 CAN控制器SJA1000电路

图3 CAN收发器82C250电路

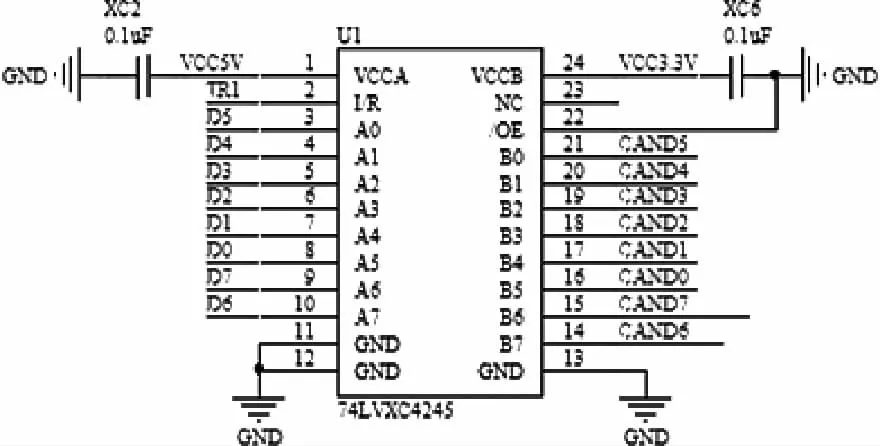

1.3 电平转换芯片电路设计

由于SJA1000的控制管脚都是5V的COMS逻辑,它的高电平的最小值为4.6V,FPGA的3.3V的TTL逻辑不能满足它的要求。因此在设计中,采用了TI公司的5V和3.3V双向电平转换芯片74LVC4245 2片,此芯片一片可以实现8个信号电平的转换,把SJA1000的5V COMS电平信号d0-d7、reset、ale、cs、rd、wr转换成3.3V TTL标准信号,连接到FPGA的引脚上。在使用电平转换芯片时,注意要将SJA1000的地址数据复用引脚d0-d7连接到其中一片74LVC4245上,其它控制信号引脚连接到另一片芯片上,便于读时序时对其电平转换方向进行控制。并将其OE引脚接地,使其始终处于片选使能状态。具体电路图如图4、图5所示。

图4 电平转换芯片74LVC4245电路

图5 电平转换芯片74LVC4245电路

1.4 单片机节点电路设计

由于后续数据显示只占用很少量的存储空间,而且对微处理器速度、功能等方面要求不高,所以选用低成本、低功耗的微控制芯片89C52,用来作为显示编码、驱动、控制等面向用户的工作。其晶振采用11.0592Mhz。其复位电路采用按键复位和上电自动复位2种,便于操作与控制。

在单片机节点中同样采用SJA1000作为CAN控制器,与FPGA电路中不同的是,将SJA1000的中断输出引脚INT与单片机的P3.3引脚相连,用于控制单片机进入中断处理程序。同样采用82C250作为CAN收发器。为了方便控制CAN报文的发送,在单片机节点电路设计中,增加了按键电路,按键电路与单片机的P3.2引脚INT0相连,按下按键时会进入外部中断0中断处理子程序,启动CAN报文的发送,并使发送数据递增 1[7,8]。

2 程序设计

FPGA节点中CAN总线接口采用verilog语言描述。在这里将FPGA程序设计分为3个部分:SJA1000初始化、发送操作和接收操作。具体流程图如图6所示。

SJA1000内部有多个寄存器,其内部寄存器对微控制器来说是以外部寄存器形式编址的片内存储器[9]。SJA1000的控制信号主要有复位控制信号reset、地址/数据复用总线ad0-ad7、地址锁存信号ale、片选信号cs、读信号rd和写信号wr。此外,还有2个控制电平转换芯片74LVC4245的电平转换方向的信号tr1、tr2,其中tr1对应ad0-ad7信号的电平转换,tr2对应其它信号的电平转换。上电后,先将SJA1000复位控制信号拉低,计数延时一段时间后将其拉高,完成SJA1000的复位。在SJA1000复位过程中将地址锁存信号ale拉低、读信号rd拉高、写信号wr拉高,电平转换方向控制信号tr1、tr2拉低,使其处于3.3V转向5V方向,并将片选信号cs拉低,使其一直处于片选使能状态,方便对其进行读写操作。

2.1 初始化过程程序设计

在对SJA1000初始化的过程中,先向模式寄存器0x00写入0x09,使其进入复位模式。然后对SJA1000内部寄存器进行配置,分别向时钟分频寄存器、总线时序0/1寄存器、中断使能寄存器、输出控制寄存器、命令寄存器写入0x88、0x03和0x1c、0x01、0xaa、0x04,向验收代码寄存器0-3、验收屏蔽寄存器0-3写入0x11、0x22、0x33、0x44和0xff、0xff、0xff、0xff。最后,再向模式寄存器写入 0x08,使其退出复位模式,进入操作模式。完成对SJA1000的初始化工作。

2.2 发送过程程序设计

在检测到发送标志位置1时,FPGA进入发送操作。在发送数据之前,先对SJA1000内部状态寄存器进行读操作,并判断其SR.3和SR.2位是否置位,只有当这2位同时置1,即最近一次发送已成功,并且发送缓冲器为空时,才可进行发送操作。进入发送操作后,分别对SJA1000发送缓冲器写入 TX帧信息 0x81、TX标识码 0x11、0x22、0x33、0x44、TX数据字节。其中TX帧信息0x81代表发送含有一个字节数据的扩展格式的数据帧,所以这里每次发送时,只向CAN地址21写入一个字节的数据,而其它TX数据字节寄存器未用。写完要发送的数据后,向SJA1000内部命令寄存器写入0x01,置位发送请求,完成发送操作。

2.3 接收过程程序设计

在检测到接收标志位置1时,FPGA进入接收操作。在接收数据之前,先对SJA1000内部中断寄存器进行读操作,并判断其IR.0位是否置位,当其置1,即接收缓冲器中有数据,且中断使能寄存器IER.0位被置1时,才可进行接收操作。进入接收操作后,分别从SJA1000接收缓冲器中读取一个字节的RX帧信息、4个字节的RX标识码和一个字节的数据。由于单片机发送的是含有一个字节数据的扩展格式的数据帧,所以这里只从CAN地址21读取一个字节的数据,而未对其它RX数据字节寄存器进行读取。读取完要接收的数据后,向SJA1000内部命令寄存器写入0x04,释放接收缓冲器,以便读取下一条报文。释放接收缓冲器后,分别对SJA1000内部仲裁丢失捕捉寄存器、错误代码捕捉寄存器进行读取,释放仲裁丢失捕捉寄存器和错误代码捕捉寄存器[10]。

2.4 读写时序设计

写时序如图7所示。

图7 SJA1000 intel模式写时序

这里根据SJA1000写时序将写操作分为4个状态:

(1)状态1:地址锁存信号ale置1有效,向地址/数据复用总线ad0-ad7写入地址。进入下一个状态。

(2)状态2:将地址锁存信号ale拉低,完成对地址的锁存。进入下一个状态。

(3)状态3:将写信号拉低,并向地址/数据复用总线ad0-ad7写入数据。进入下一个状态。

(4)状态4:将写信号拉高,完成写操作。

读时序如图8所示。

图8 SJA1000 intel模式读时序

这里根据SJA1000读时序,FPGA对于inout引脚ad0-ad7的三态门处理以及电平转换芯片74LVC4245的方向控制,将读操作分为9个状态。

(1)状态1:地址锁存信号ale置1有效,向地址/数据复用总线ad0-ad7写入地址。进入下一个状态。

(2)状态2:将地址锁存信号ale拉低,完成对地址的锁存。进入下一个状态。

(3)状态3:向地址/数据复用总线ad0-ad7写入高阻态,将电平转换方向控制信号tr1拉高,使其处于5V转向3.3V方向,准备从SJA1000中读取数据。进入下一个状态。

(4)状态4:此状态为空状态,用于等待74LVC4245改变电平转换方向。进入下一个状态。

(5)状态5:将读信号拉低,开始从SJA1000中读取数据。进入下一个状态。

(6)状态6:此状态为空状态,用于等待读取数据完成。进入下一个状态。

(7)状态7:对读取的数据进行采样,将ad中的值赋给ad_out,可进行存储或输出。进入下一个状态。

(8)状态8:将读信号拉高,完成读操作,将电平转换方向控制信号tr1拉低,使其处于3.3V转向5V方向。进入下一个状态。

(9)状态9:此状态为空状态,用于等待74LVC4245改变电平转换方向。进入下一个状态。

2.5 单片机节点程序设计

在使用单片机89C52对CAN控制器SJA1000内部寄存器进行访问时,将其内部寄存器当作以外部寄存器形式编址的片内存储器。与FPGA不同的是,需要在程序的最初对单片机进行中断初始化。发送时采用按键的方式使单片机进入外部中断0,在使被发送的数据自增1的同时,置位发送请求。接收时,通过SJA1000输出的int信号拉低,使单片机进入外部中断1,并将接收到的一个字节数据显示在数码管上。其它初始化过程、发送过程以及接收过程程序与FPGA节点程序类似[11]。

3 仿真与验证

在quartusII中分别对FPGA节点发送过程和FPGA节点接收过程进行了仿真,仿真图如图9、图10所示。

图9 FPGA节点发送操作过程仿真

图10 FPGA节点接收操作过程仿真

在实验过程中,由FPGA节点向单片机节点以2s的间隔依次发送 0x11、0x22、0x33、0x44、0x55、0x66、0x77、0x88,单片机节点接收到数据后,将16进制数据转换为10进制数据,并在数码管上显示出来。再通过按键的方式由单片机节点向 FPGA节点依次发送 0x01、0x02、0x03、0x04、0x05、0x06、0x07、0x08,FPGA节点接收到数据之后,将数据进行采样输出到相应的I/O引脚上,通过测量相应引脚电平值得以验证无误。

4 结束语

通过FPGA控制SJA1000实现与单片机的CAN总线通信,与传统的单片机CAN总线通信相比,降低了体积与重量,解决了传统的单片机与单片机进行CAN总线通信时,单片机处理数据速度较慢,以及应用面较窄等问题。使CAN总线通信拥有了一种新的实现方法,并在高性能激光告警接收机中得到了成功应用。

[1]YE Qing,YAO Longhai,CHEN Changjun.FPGA and DSP based digital laserwarning system design[J].Optic Technology Application,2006,21(3):5-8(in Chinese).[叶庆,姚龙海,陈长俊.基于FPGA和DSP的数字激光告警系统的设计[J].光电技术应用,2006,21(3):5-8.]

[2]GE Yaming,PENG Yongfeng,XUE Bing,et al.Zero-based learning FPGA Altera FPGA-based devices & verilog HDL language[M].Beijing:Mechanical Industry Press,2010(in Chinese).[葛亚明,彭永丰,薛冰,等.零基础学FPGA基于Altera FPGA器件 & Verilog HDL语言 [M].北京:机械工业出版社,2010.]

[3]YANGChunjie,WANG Shuguang,KANG Hongbo,etal.CAN bus technology[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2010(in Chinese).[杨春杰,王曙光,亢红波,等.CAN总线技术[M].北京:北京航空航天大学出版社,2010.]

[4]XU Mushui,LIU Jinguo.FPGA-based CAN bus communication interface design [J].Electronic Design Engineering,2010,18(10):96-99(in Chinese).[徐木水,刘金国.基于FPGA的CAN总线通信接口的设计 [J].电子设计工程,2010,18(10):96-99.]

[5]ZHOU Ligong.Project drive-CAN-bus field busbased tutorial[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2012(in Chinese).[周立功.项目驱动--CAN-bus现场总线基础教程[M].北京:北京航空航天大学出版社,2012.]

[6]ZHANG Peikun,GAO Wei,SONG Zongxi,et al.FPGA-based CAN bus communication node design[J].Instrument Technique and Sensor,2010(12):68-70(in Chinese).[张培坤,高伟,宋宗喜,等.基于FPGA的CAN总线通信节点设计[J].仪表技术与传感器,2010(12):68-70.]

[7]ZHANG Yingchun,JIMaosheng.Based MCU CAN bus system design[J].Computer and Network,2012(5):52-54(in Chinese).[张迎春,季茂胜.基于单片机的CAN总线系统设计[J].计算机与网络,2012(5):52-54.]

[8]LIU Tao,ZHANG Chunwei.Based on 89C51 and SJA1000 CAN communication method[J].Computer Programming Skills & Maintenance,2011(4):87-89(in Chinese).[刘涛,张纯伟.基于89C51和SJA1000的CAN通信方法研究[J].电脑编程技巧与维护,2011(4):87-89.]

[9]YUE Kui,LIU Shaojun,HUANG Daoping,et al.SJA1000 registers of the VHDL language literacy design and application [J].Computer and Digital Engineering,2009(1):175-178(in Chinese).[岳奎,刘少君,黄道平.SJA1000内寄存器的VHDL语言读写设计与应用[J].计算机与数字工程,2009(1):175-178.]

[10]LIHongtao,ZHOU Xiaohua,GU Chen.Verilog HDL and FPGA development,design and application[M].Beijing:National Defense Industry Press,2013(in Chinese).[李洪涛,朱晓华,顾陈.Verilog HDL与FPGA开发设计及应用 [M].北京:国防工业出版社,2013.]

[11]CHEN Yehai,RONGmengtian.89C51 microcontroller-based CAN bus system design[J].Electronic Component Applications,2008,10(9):42-44(in Chinese).[陈烨海,戎蒙恬.基于单片机89C51的 CAN总线系统设计 [J].电子元器件应用,2008,10(9):42-44.]