一种基于ADS62P49的高速宽带采集卡的设计*

2014-11-28校建锋熊碧霞刘林涛

校建锋 熊碧霞 刘林涛

(中国船舶重工集团公司第七二二研究所 武汉 430079)

1 引言

随着ADC、DSP和FPGA器件的发展,高速数字信号处理也在不断的发展。高速采集卡是高速数字信号处理的平台,高速采集卡的性能直接影响到数字信号处理单元的工作[1]。高速ADC芯片是高速数字信号处理技术的关键器件之一,ADC芯片的采样速率、采样精度、无杂散动态范围等参数都不同程度决定着模拟信号数字化以后信号的质量,采用具有高采样率、高精度的ADC芯片做模数转换,设计合理的模拟前端,并在布局布线时做精心设计,才有可能设计出高速、高性能的宽带采集卡。

2 电路设计及其功能

2.1 采集卡功能结构

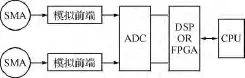

通用的采集卡主要由三部分构成:模拟前端、ADC、DSP,其功能结构如图1所示[3]。

图1 采集卡功能结构图

图1中SMA为模拟信号输入接口、模拟前端对输入的模拟信号进行调理、ADC芯片将模拟信号转换为数字信号、DSP/FPGA芯片对数字信号进行处理[2]。

2.2 高速ADC芯片

高速ADC一般为非缓冲ADC,非缓冲ADC或开关电容型ADC具有时变输入阻抗,在高中频情况下较难设计;使用非缓冲ADC,任何情况下都应以跟踪模式进行输入匹配,并利用制造商提供输入阻抗表进行设计[4]。

本设计中选用TI公司生产的ADS62P49模数转换芯片,最高采样率在LVDS模式下为250Mbps,在CMOS模式下为210Mbps。ADS62P49芯片具有DC偏置校正功能,在250Mbps采样率时功率为1.25W,外部输入的采样时钟幅度可低至400mVpp,同时支持内部或外部参考电平[6]。

理论上来讲,ADC能够采集到的信号为最高采样率的一半,即在LVDS模式下,ADC能够采集125MHz的模拟信号;在CMOS模式下能够采集最高105MHz的模拟信号。

2.3 模拟前端设计

ADC模拟前端是确定转换器接收并采样的信号或信息质量的关键部分,前端的设计可以选用变压器(巴伦)、运算放大器或者RC网络来进行。前端的设计有七个参数至关重要,它们是输入阻抗、电压驻波比(VSWR)、通带平坦度、带宽、信噪比(SNR)、无杂散动态范围(SFDR)和输入驱动电平。

输入阻抗是设计或负载的额定特征阻抗,大多数情况下为50Ω;电压驻波比是一个无量纲参数,反映的是在目标带宽内,有多少功率被反射到负载中,它还与输入驱动电平有关;通带平坦度通常指额定带宽内容许的波动/纹波量;带宽指系统所用的频率起点与终点之差,可窄可宽;信噪比要求由整个系统的噪声电平设计决定;无杂散动态范围要求由整个系统的动态范围决定;输入驱动电平与带宽、输入阻抗和VSWR特性有关。

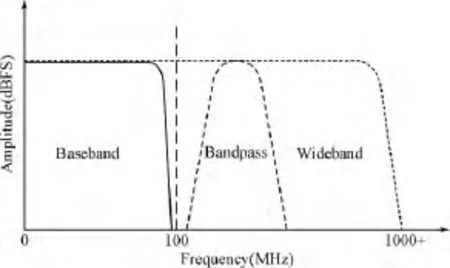

ADC前端本质上有三种类型:基带型、带通或超奈奎斯特(有时也称为窄带)型以及宽带型,如图2所示。

图2 基带、带通与宽带

基带设计要求的带宽是从DC(或低MHz区)到转换器的奈奎斯特频率,这类设计可以采用放大器或变压器(巴伦)。带通设计意味着只使用转换器带宽的一小部分,在高中频时,只需要20MHz~60MHz带宽,这种设计通常使用变压器或巴伦,若是较高频率下的SFDR性能足够,也可以使用放大器。宽带设计通常指需要全部带宽的设计,带宽范围为DC(或低MHz区)至+GHz区,通常采用宽带巴伦设计,但是,随着放大器设计技术的发展,使用宽带的低噪声放大器几乎可以实现所有类型的模拟前端。

ADC前端设计一般分为五个步骤:一是了解系统和设计要求,二是确定ADC的输入阻抗,三是确定ADC的基本性能,四是选择变压器及与负载匹配的无源元件,五是对设计进行基准测试。

本设计选用差分运算放大器AD8352来设计模拟前端,模拟前端带宽为DC至2.2GHz(10dB增益),单端输入差分输出,输入阻抗为50Ω。AD8352可以通过外部电阻调节放大器增益,增益可调范围为:3dB~25dB,也可以通过外部电阻和电容来调节通带增益平坦度。AD8352是单端或差分输入转差分输出,3V~5.5V单电源供电[11]。

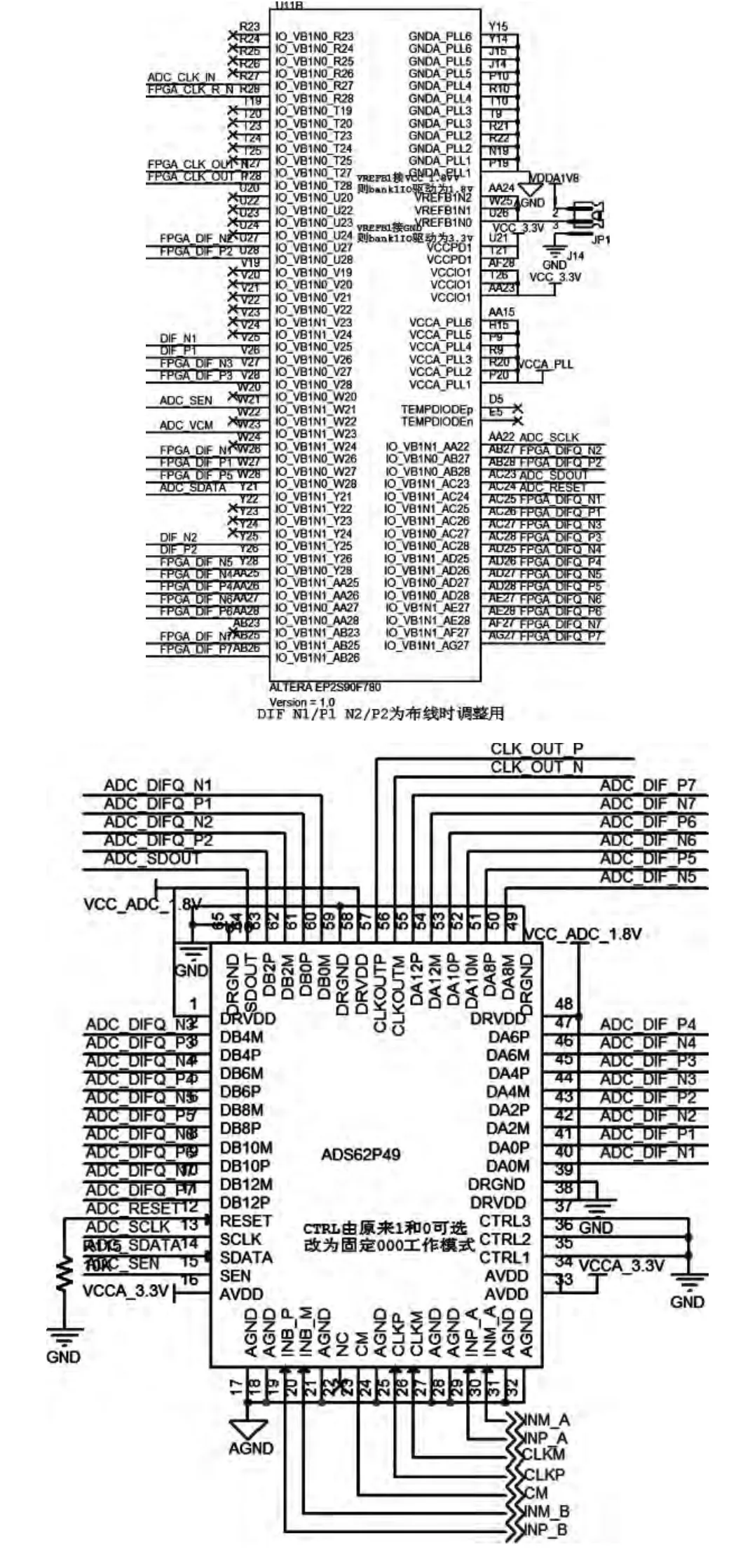

2.4 原理图设计

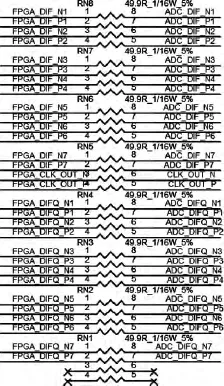

本设计中高速宽带采集卡上的ADC芯片为双通道独立工作模式,ADC芯片的工作模式配置引脚CTRL1-3应全部接GND。ADC的串行接口与FPGA的GPIO连接,可以通过FPGA对ADC进行配置。另外需要注意,ADC数字输出端为1.8V COMS或LVDS电平,在FPGA中应选择独立的bank,并配置为对应的接口电平来接收ADC的数字信号[6],本设计中选择FPGA芯片BANK1的I/O做为ADC的数字信号接口,其电平可以选择为1.8V也可以选择3.3V。在设计原理图时,完成ADC与FPGA及模拟前端各个信号的连接后应对特殊的信号进行属性设置,尤其是对模拟输入信号的差分属性设置,ADC芯片ADS62P49有两个通道,每个通道由一对差分线输入,每个通道的输出为七对差分线传送的差分数字信号,在选择FPGA与ADC数字信号连接的引脚时,要注意选择可以做为差分对的I/O引脚与ADC数字输出端的七对差分信号相连,并在每对引脚之间串联49.9Ω的精密电阻,以吸收尖峰脉冲防止信号的反射。ADC与FPGA设计原理图如图3所示[8]。

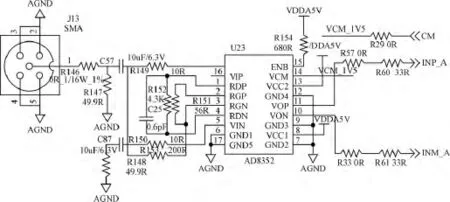

本设计中,ADC模拟前端为单端输入差分输出,输入阻抗为50Ω,要求模拟带宽为DC至150MHz,放大器的增益可根据输入信号的大小进行调整,RGP和RGN之间的电阻值越大,AD8352的增益越小,反之,增益越大。改变放大增益,需要同时调整通带平坦度,不同的增益平坦度通过调整RDP和RDN引脚之间并联的电阻和电容值来调整。AD8352由一个5V电源单独供电,参考电平VCM为1.5V,由ADC芯片的CM引脚提供。ADC前端设计采用33Ω串行电阻标准,如图4所示,串联33Ω的电阻可以优化ADC输入端的源阻抗,并最大程度地减少返回到模拟前端的“反冲”或电荷注入,它能够优化ADC内部采样网络的建立,提供更高的线性度,从而优化转换器的SFDR性能。这里要注意是,ADC前端设计串联的电阻值并不是固定的33Ω,每一种ADC都有略微的不同,可以根据实测的结果,选用一系列的电阻逐个试验,直到找到最合适的电阻值,试验的电阻值范围通常是10Ω~140Ω。本设计模拟前端设计原理图如图4所示[5]。

图3 ADC与FPGA设计原理图

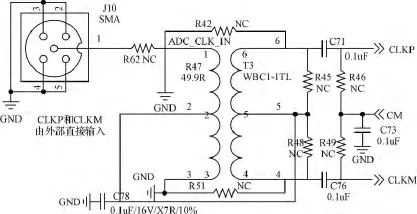

ADC的采样时钟可以由FPGA产生,也可以从外部输入,采样时钟电路是单端输入差分输出,输入阻抗为50Ω。本设计选用 WBC1-1TL或ADT1-1WT变压器来实现,变压器属于无源器件,不增加噪声,也不消耗功率,本设计中采样率为200MHz,使用变压器处理时钟,能够更好地保持SNR和SFDR性能。本设计中ADC采样时钟电路原理图如图5所示。

2.5 PCB设计

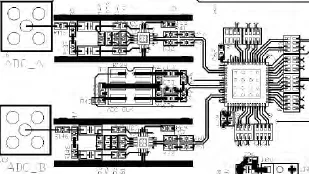

ADC芯片的PCB设计要求通常不出现在它的数据表中,但信号和功率布局可能会极大影响转换器性能,低劣的布局会导致性能下降。正确的去耦、接地和信号调节有助于提高系统性能。在设计中,如果电路未能包含足够的解耦电容,则电路会“看到”过多的电源噪声,由于ADC具有有限的PSRR特性,因此这些噪声将耦合进入模拟输入,并破坏ADC数据的数字输出“频谱”,另外,噪声可能会调制ADC的时钟信号,这会把噪声与模拟输入卷积起来,并导致额外寄生信号。本设计中对ADC及模拟前端的布局布线如图6和图7所示。

ADC及模拟前端PCB设计时,应优先保证模拟信号走线,走顶层,以GND层做参考,中间不能跨层,模拟信号两边用模拟地进行隔离(包括顶层和底层),如PCB顶层和底层视图中所示。差分线严格按照差分走线要求进行设计,尽可能不跨层,并以GND层为参考层进行走线。ADC为64QFN封装,底部是一个7.4mm*7.4mm的焊盘,需要在PCB上进行分割接地处理,如PCB顶层视图中所示,由16个过孔将焊盘划分为9个面积相同的正方形小块儿,在PCB的背面同样位置,放置一个同样大小的焊盘,并在制板时标识此焊盘上面喷锡,不能覆盖绿油。这样处理可以使芯片焊接牢固,在芯片正常工作时良好散热,从而发挥最佳的性能。ADC采样时钟可以从PCB外部输入,也可以由FPGA提供,在本设计中可以通过电阻来选配。

图4 模拟前端设计原理图

图5 采样时钟设计原理图

图6 PCB顶层视图

图7 PCB底层视图

3 Stp测试结果

ADS62P49为双通道ADC,为了便于说明,用通道1模数转换后的信号做参考信号,其模拟输入端输入1MHz的正弦波,通道2输入不同频率的信号,然后从FPGA仿真工具Stp中观察ADC转换后的数字信号的波形。测试时,ADC采样频率为200MHz,模拟前端输入信号的频率分别为10KHz、25MHz、50MHz、100MHz,为便于观察,10KHz设置为占空比为50%的方波,仅观察其正半周期,其它输入信号为正弦波[7,10]。

3.1 低频信号测试

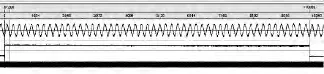

ADC通道1输入1MHz正弦波,通道2输入10KHz方波,在FPGA中用Stp仿真工具采集到的信号如图8所示。由测试结果可以看到,通道1一个周期有200个采样点,即 T1/Ts=200(Ts为ADC采样周期),即fs/f1=200,则f1频率为fs/200=200MHz/200=1MHz,通道2正半周期有10000个采样点,则整个周期有20000个采样点,即可算出其频率为200MHz/20000=10KHz[9]。

图8 Stp中10KHz信号测试结果

3.2 8倍采样结果

ADC通道1输入1MHz正弦波,通道2输入25MHz方波,在FPGA中用Stp仿真工具采集到的信号如图9所示。由测试结果可以看到,通道2一个周期有8个采样点,即可得出其频率为200MHz/8=25MHz。

图9 Stp中25MHz信号测试结果

3.3 4倍采样结果

ADC通道1输入1MHz正弦波,通道2输入50MHz方波,在FPGA中用Stp仿真工具采集到的信号如图10所示。由测试结果可以看到,通道2一个周期有4个采样点,即可得出其频率为200MHz/4=50MHz。

图10 Stp中50MHz信号测试结果

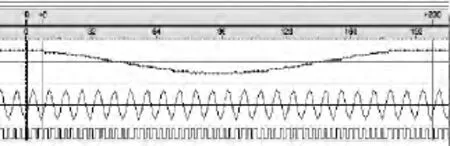

3.4 2倍采样结果

图11 Stp中100MHz信号测试结果

ADC通道1输入1MHz正弦波,通道2输入100MHz方波,在FPGA中用Stp仿真工具采集到的信号如图11所示。由测试结果可以看到,通道2一个周期有2个采样点,即可得出其频率为200MHz/2=100MHz。

4 结语

本文提出了一种基于ADS62P49的高速宽带采集卡的设计,给出了设计的原理图及PCB,并给出了设计原理图及PCB过程中应该注意的问题及相应的处理方法,最后给出了在FPGA的仿真工具Stp中测试出的ADC转换器采集到的各种频率的信号的波形,验证了高速宽带采集卡的性能。

[1]黄丽莲,李子绪.高性能中频采样系统的设计与实现[J].电子设计工程,2012,18(12):1-4.

[2]张乐,张新军,施聪,等.中频采样的原理及其应用[J].通信技术,2001(9):8-11.

[3]张俊杰,章凤麟,叶家骏.高速数据采集系统设计[J].计算机工程,2009,35(1):207-210.

[4]Stephen H.Lewis,Paul R.Gray.A Pipelined 5-M/s 9-bit Analog-to-Digital Convert[J].IEEE J.Solid-State Circuits,1987,22(12):954-961.

[5]Ahmed M.A.Ali,Andy Morgan,Chris Dillon,et al.A 16b250MS/s IF-Sampling Pipelined A/D Converter With Background Calibration[C]//ISSCC,2010,Dig.Tech.,2010:292-294.

[6]Texas Instruments.ads62p49Datasheet.Slas635B-A-pril 2009-Revised[Z].Janrary 2011.

[7]R.Kumar,D.Taggart,G.Goo.Performance Analysis of Analog-to-Digital Converters for Wideband Digitally Modulated Signals[C]//2004IEEE Aerospace Conference Proceedings,2004:1375-1382.

[8]董振龙,董惠,武锦.基于FPGA的高速ADC测试平台的设计[J].计算机测 量与控制,2012,20(9):2072-2374.

[9]IEEE Standards Board.IEEE Std 1241-2000IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters[S].2001-06.

[10]王卫江,陶然.高速ADC的性能测试[J].电子技术应用,2004(2):339-341.

[11]Analog Device Inc.AD8352Datasheet(EB/OL).(2008-07)[2010-05-10].http://www.analog.com/static/imported-files/data_sheets/AD8352.pdf.