应答器报文硬件和软件CRC校验对比分析

2014-11-27朱卫华

朱卫华 张 奇

朱卫华:西门子信号有限公司 工程师 710016 西安

张 奇:西门子信号有限公司 工程师 710016 西安

1 应答器

地-车信息传输系统是列车运行控制系统的核心构成部分之一。车载列控设备需要获取从列车控制中心发送的临时限速命令、前方线路的允许速度、线路坡度、区段长度等信息,从而对高速行驶列车进行自动控制。

应答器(Balise)作为地-车信息传输通道中的地面信息传输载体,广泛应用在我国高铁领域。主要用途是向列控车载设备提供可靠的地面固定信息和可变信息。应答器分为固定(无源)应答器和可变(有源)应答器。当应答器被车载天线激活后,将持续的发送存储在其内部的报文,从而将地面信息传递给车载设备。

2 报文CRC校验

CRC即循环冗余校验码(Cyclic Redundancy Check),是数据通信领域中最常用的一种差错校验码,为了保证地面到车载设备传输信息的正确,应答器报文系统采用75位的CRC校验。当车载设备接收到报文数据后,需要对报文CRC校验和解码,从而获得正确的报文。75位CRC校验是整个报文接收过程中最复杂和关键的环节,为此介绍CRC校验的编码策略、软件实现和硬件实现,以及各自特点,为开发报文CRC校验模块提供参考。

2.1 编码策略

FFFS编码策略(Form Fit Function Specification Coding Strategy)是由EUROSIG联盟为推进欧洲铁路信号标准化而制定的标准,它定义了应答器报文的格式。报文格式对随机位错误、突发错误、位滑动和位插入,以及它们的所有组合设计有完全的安全性证明。应答器长报文原始数据为830位,经过加扰和编码后,产生了1023位的数据。在该数据循环发送的过程中从任意字节开始取1023位可以被编码的多项式整除。利用报文的这个特点,可以采用多项式除法(模2除法)对报文进行CRC校验。取1023位长度的报文数据M(x),表示为:校验公式G(x)的最高次数为75,表示为:

以G(x)为模对M(x)作模运算,表示为:

其中Q(x)和R(x)分别是商和余项。

当CRC余数R(x)为零时,说明报文数据CRC校验正确,非零表示存在位错误,重新选1023位数据进行校验。

2.2 软件算法

随着微处理器的不断发展,及高速低功耗处理器的不断推出,使用软件进行CRC校验成为可能。软件算法主要有程序法、查表法和众多优化设计。限于篇幅这里只列出程序法和查表法2种方法。

2.2.1 程序法(比特型算法)

1.将1023位数据流高75位(先收到的为高)放入一个长度为75位的寄存器。

2.如果寄存器的首位为1,则与生成多项式G(x)做异或运算;否则仅将寄存器左移1位(寄存器的最低位从下一个字节获得)。

3.重复第2步,直到数据流(1023位)全部移入寄存器。

4.寄存器中的值为全0则报文CRC校验正确,否则报文存在错位,继续下一个1023位的检验。

该算法通过左移位和异或运算来完成模2除法运算。原理简单易懂,易于维护和更新。对1023位数据完成一次CRC校验,大概需要1023-75=948次移位运算,和948×75=71100次异或运算(最不利情况下)。

2.2.2 查表法(字节型算法)

1.75位的CRC寄存器组初始化为全“0”。注意:CRC寄存器组初始化全为1时,最后CRC应取反。

2.CRC寄存器组向左移8位,并保存到CRC寄存器组。

3.原CRC寄存器组高8位(右移8位)与数据字节进行异或运算,得出一个指向值表的索引。

4.索引所指的表值与CRC寄存器组做异或运算。

5.数据指针加1,如果数据没有全部处理完,则重复步骤2。

6.1023位全部处理完毕后,寄存器中的值为全0则报文CRC校验正确,否则报文存在错位,继续下一个1023位的检验。

字节型算法一次移出待测数据的8位,即一次进行一个字节的计算,则余数表格有28=256个表值,每个表值为75位。对1023位数据完成一次CRC校验大概需要1024/8=128次移位运算、128次查表运算和128×8+128×75=10624次异或运算。

2.3 硬件算法

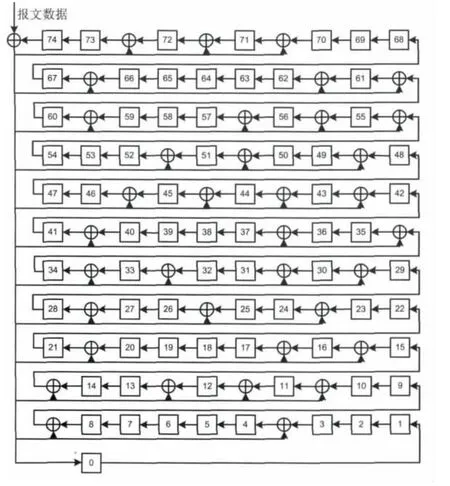

在硬件中实现该过程需要使用移位寄存器(CRC寄存器)。该移位寄存器长度为75位。图1为实现该算法的线性反馈移位寄存器(LFSR)的框图。

报文CRC校验过程如下。

1.初始化75位CRC寄存器。

2.每次获取报文位后,将输入数据和上一次异或运算的结果组成新的数据,进行循环异或运算。

3.数据未满1023则返回步骤2,收到1023位数据后,判断CRC寄存器内的值。如果余数为0,则表示收到的1023位报文可以被75位多项式整除,可以进一步判断1023位是否为正式报文;如果余数非0,则表示不能整除,该1023位存在错位。

以上即为单线程的CRC校验算法原理。为了能够及时收到正确的报文,达到接收1位报文数据就可以判断整个1023数据流是否满足CRC校验,可以采用如下2种方式进行实现。

方式1:并行设计。

在设计CRC校验时,将报文数据同时输入到1023路CRC校验电路中,每路信号开始校验的时间依次后移1位。该方法理论上对于数据可以做到1位数据就可以计算出整个数据段的CRC校验码,但是,由于每位CRC寄存器的值都是由有效数据位和CRC寄存器的前一个状态组成的异或电路运算所得,并且需要1023个相差1位的硬件电路,硬件单元使用较多。笔者以ACTEL公司的FPGA工作频率40 MHz为例,制作的单一线程CRC校验需要消耗大概500个硬件单元,1023路需要消耗大概511500个硬件单元。

方式2:并行优化设计。

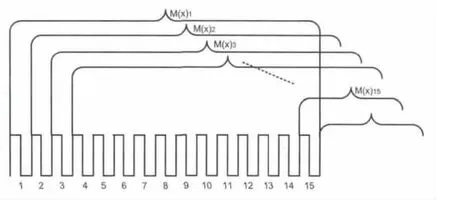

应答器报文以565 kb/s速率按位进行串行传输,因此一个数据周期为1.77 μs。而现有的FPGA等硬件设备的工作频率均远远高于报文传输速率。以频率为40 MHz的FPGA为例,其工作周期为0.025 μs,在等待接收1位报文数据的过程中,FPGA可以进行大概70次运算,由于1023次移位运算即可判断CRC校验的正确性,因此单线程计算一次CRC的过程内可以收到15位报文数据。为了实现1位数据即可判断CRC正确性,需要扩展到15线程,如图2所示。

图2 15线程循环校验

接收到1位数据与前1022位构成M(x)1,将该1023位数据输入一路CRC校验电路;再接收到1位数据与前1022位构成M(x)2,同样输入一路CRC校验电路,直到M(x)15,一共15个CRC校验线程。这样当第M(x)1数据CRC校验完毕后,可以继续接收数据重新构成新的M(x)1,周而复始,每收到一位数据都可以计算出CRC校验的结果。

一路CRC校验需要消耗500个硬件单元,15路则需要消耗7500个硬件单元。

3 软件校验和硬件校验对比分析

3.1 用时对比

以软件校验使用40 MHz主频的MCU为例,且2个时钟周期为一个指令周期,则一个指令周期大概为0.05 μs。在接收满1023位报文后,比特型算法大概需要(948+71100) ×0.05=3.602 ms可以计算出CRC余数;字节型算法大概需要(128+128×256/2+10624) ×0.05=1.356 ms可以计算出CRC余数。实际设计中由于软件为串行处理机制,因此用时会大于估算结果。

硬件校验以使用40 MHz主频的FPGA为例,则并行设计和优化的并行设计每隔1.77 μs即可以校验一个1023位数据。

由此可见软件校验的运算时间保持在毫秒的数量级,而硬件则保持在微秒的数量级。

3.2 占用资源对比

软件校验可以集成在MCU的程序内,查表法需要占用75×255=19125位的程序存储空间来放置余数表。软件设计的灵活性高,可移植性强,且修改方便。

硬件校验需要相应的硬件电路作为支持,设计复杂。1023线程的并行设计方案占用大量硬件资源,在不要求1位即可校验的情况下,可以通过减少线程的方式来降低硬件资源的消耗。优化的并行设计方案需要15路并行校验代码,消耗大概7500个硬件单元。

3.3 实时性对比

软件一次CRC校验时间远远大于1.77 μs的报文接收时间,因此不能达到同步校验。校验延时将随报文接收误码的增多而逐渐累积,例如报文内存在1000位误码,则校验时间将大于1 s。因此软件校验实时性差。硬件校验1.77 μs内即可判断数据的CRC是否正确,并且对报文接收误码没有时间积累,能够达到同步校验,因此实时性最好。

4 结束语

软件CRC校验占用资源较少,设计简单、灵活,代码可移植性强,修改方便。但由于校验用时较长,且存在延时积累,导致实时性差,因此可以应用在对实时性要求不高的场合,比如使用便携式手持设备对报文读取测试等场合。

硬件CRC校验需要相应的硬件电路,设备成本较高,设计复杂。通过减少并行设计的线程数可以在校验时间和资源占用之间进行适当平衡;优化并行设计方案,需要硬件时钟周期和报文传输时钟周期的配合,对硬件电路的设计精度和可靠性要求较高,但占用资源较少,可以做到同步校验,实时性好,可以应用在车载报文传输通道等设备上。

针对不同的使用场合,应该合理的选择报文CRC校验的方法,以达到速度、资源和成本的平衡,使设计达到最优化。

[1]肖甜,赵会兵.欧洲应答器编码策略的安全性研究[J].铁道学报,2008.

[2]朱荣华.一种CRC并行计算原理及实现方法[J].电子学报,1999.

[3]李剑峰.新的高性能CRC查表算法[J].计算机应用,2011(6).

[4]张树刚,张遂南,黄士坦.CRC校验码并行计算的FPGA实现[J].计算机技术与发展,2007.

[5]徐宁,杨志杰.欧洲应答器报文译码的研究以及FPGA实现[J].铁路通信信号,2008.