基于FPGA的加密算法改进及实现

2014-11-20郭婷婷

武 一,郭婷婷

(河北工业大学信息工程学院,天津300401)

随着专用虚拟网络的快速发展,人们对于通信加密的要求也随之增高。为解决这一问题,通常采用数据加密标准(Data Encryption Standard,DES)和高级加密标准(Advanced Encryption Standard,AES)来提高信息系统及数据的安全性和保密性。目前研究表明,一些ASIC(专用集成电路)和FPGA(现场可编程门阵列)器件可成功实现DES和AES的多种硬件加密。其中,一部分研究侧重于使用循环结构来减小芯片的资源占用,另一部分则侧重于使用流水线结构来提高吞吐率。对于DES和AES加密算法来说,要想达到一个高的吞吐率,在每一轮运算中嵌入流水线寄存器是必要的[1]。然而,没有相关的权衡,一味地嵌入流水线将增加逻辑运算复杂度和硬件占用面积。因此,硬件资源的共享和复用以及逻辑门的压缩是产生一个加密电路所不可缺少的条件。

1 数据加密

为了保护私有信息不被非法窃取,数据加密技术应运而生。数据加密技术采用相关的加密算法对数据进行屏蔽,使其成为不可读的代码,只有指定的用户或场合才能解除屏蔽而获得数据。在实际应用中,DES和AES加密算法被普遍用来实现敏感的金融数据、政府信息和私人交易的加密[2]。

数据加密的实现方式通常分为软件实现和硬件实现两种。软件实现方式在主机上运行加密软件,占用主机资源、处理速度慢、抗攻击能力差[3]。而硬件实现方式,基于FPGA或ASIC器件的加密设计很难被非法攻破。因此,从本质上说,硬件加密具有更高的物理安全性。另外,硬件加密独立于主机实现数据存储和运算,资源占用少,满足更高的实时性要求。

传统硬件实现主要采用ASIC,设计成本高、系统扩展性差。FPGA器件以其硬件的安全性和高速性以及软件的灵活性和易维护性,成为研究和实现加密算法的理想硬件平台。采用FPGA实现的加解密系统可在保证加解密性能的同时提供更好的可扩展性和通用性[4]。

文献[1-3]介绍了DES加密算法的FPGA实现。这些研究中所设计的结构能够达到Gbit/s级的吞吐率。其中最高的吞吐率可达到6 Gbit/s[2]。文献[4-6]描述了AES算法的FPGA实现。文献[4]中提出了提高吞吐率的可能性方案(不超过1 Gbit/s),文献[5]中已经能达到7 Gbit/s的吞吐率。但这些研究工作都集中在吞吐率方面,没有权衡相关的芯片资源占用。

因此,本文采用资源优先的设计方案,在一片FPGA芯片上设计实现了DES、AES加解密系统。通过分别对系统的轮函数及S盒进行优化设计,实现系统的高速率、低占用。

2 系统设计

2.1 DES加密系统设计

DES加密系统中,输入的64位明文经初始置换后,数据移位,明文块被分成左右两部分,各32位。其中左半部分依赖循环密钥进行逻辑运算,右半部分不变,然后交换左右两部分,并将此过程循环进行16次。这个过程既包含替代又包含移位,数据和密钥在这一阶段被结合在一起。DES加密流程如图1所示。

数据的安全性取决于密钥的安全性设置。每一轮运算的关键是初始密钥的字节变换和由内部密钥产生器执行的左移操作[5]。

内部子密钥产生器对输入的64位的外部密钥K进行奇偶校验,剔除奇偶校验位,再经置换得到56位有效密钥,将得到的密钥分成两部分,每部分28位,分别输入到28位的寄存器C0、D0中。

图1 加密系统流程图

在内部子密钥产生器中,除寄存器(C0,D0)外,还有16 对寄存器,即(C1,D1),(C2,D2),…,(C16,D16)。C 和 D中的内容分别向左移动1至2位便可得到加密时的内容,这种移位方式是按循环移位寄存器方式进行的。在16轮左移操作中,第1、2、9、16轮密钥位数只左移1位,其余轮密钥左移2位,共计向左移动了28位,这样就保证了C16=C0,D16=D0,即(C16,D16)的内容和(C0,D0)完全相同。

合并寄存器C1和D1中存储的28位数据,形成56位密钥,并依据压缩置换确定48位的内部子密钥K。如图2所示。

图2 子密钥产生框图

加密过程中要实现16轮的变换,才能得到最终密文。若轮函数采用硬件级联的实现方式,可得到较快的处理速度,但每个时钟周期都要将数据存入寄存器,要占用很大的资源空间[6]。

考虑到FPGA的硬件资源有限,本设计提出重复调用一份轮函数的硬件拷贝,即仅用硬件实现一套密钥变换和密钥加数据运算轮函数,通过反复16次调用这一硬件结构来实现1次DES加密运算。以时间换空间,达到硬件资源占用的最小化[7]。同时,为了兼顾芯片的处理速度,在轮函数内部设置一级流水线来提高整体处理的速度。

在硬件上实现密钥变换函数和密钥加数据轮函数的同步流水线架构,减少了相邻流水线级间的逻辑复杂度[8]。通过设置轮计数器对所进行的轮运算计数,控制数据选择器,从而实现轮函数复用。图3为轮函数硬件结构电路图。

2.2 AES加密系统设计

AES-128加密算法需要运行10轮,在每一轮运算中,字节变换是唯一的非线性变换。次变换使用S盒来独立操作状态矩阵中的每个字节。

设计一个合适的S盒能够很大程度上减少AES硬件电路的复杂度和运算量[9]。目前大多采用基于复合域变换的S盒实现方法。

具体操作是将域GF(28)上的元素取逆同构线性变换为在GF(24)的取逆。GF(24)上的乘法取逆所消耗的资源相对较少,可降低资源消耗。不足是增大了硬件设计的复杂性和实现的时延[10]。

为避免执行同构变换,本设计的S盒在GF(24)2上取乘法逆,原S盒的仿射函数不变。具体选择GF(2)[x]上不可约的三项式x4+x+1定义GF(24)上的乘法,选择子GF(24)上的二次不可约多项式x2+x+8定义GF(24)2上的乘法。然后对所定义的域GF(24)2乘法取逆,并且与AES算法S盒的仿射函数相复合生成新的S盒。

图3 轮函数硬件结构电路图

实现过程如下:

1)设AES算法S盒的仿射函数是z=A×t+0x63,则z=t⊕(t<<1)⊕(t<<2)⊕(t<<3)⊕(t<<4)⊕0x63。

2)输入:8 bit向量 y=(y7,y6,…,y0)。

输出:8 bit向量 z=(z7,z6,…,z0)。

令 b=(y7,…,y0),c=(y3,y2,…,y0),将 y=(b,c)看作是域GF(24)2的元素bx+c,取逆:(bx+c)-1=b(b28+bc+c2)-1x+(c+b)(b28+bc+c2)-1;(b28+bc+c2)-1可通过查表完成。

3)设乘法取逆的结果是dx+e,将之用向量表示为t=(t7,t6,…,t0),再计算:z=t⊕(t<<1)⊕(t<<2)⊕(t<<3)⊕(t<<4)⊕0x63,并输出结果z=(z7,z6,…,z0)。

经变形后的S盒仍满足AES加密算法提出的设计要求,且由于不执行同构变换,逻辑电路门数减少,更易设计和实现。

在加解密系统中,解密过程是加密过程的逆过程,每一轮包括逆字节变换ISB,逆行位移运算ISR,和逆列混合运算IMC。在首轮运算开始之前,包括一次轮密钥加运算ARK,而最后一轮不包括逆列混合运算IMC。加密和解密过程往往由两个电路分开实现,这导致硬件资源损耗过大,且不利于加密和解密的同步优化[11]。

为了弥补这两个不足,在设计中,解密模块将分别调用加密模块的电路结构,利用加密硬件资源的复用完成解密工作,减少硬件资源损耗[12]。另外,解密时先执行非线性字节变换,有利于加解密的同步优化。

实现过程如下:解密时,首先进行数组矩阵的逆仿射变换,然后调用加密电路的字节变换部分,得到逆字节变换的输出。输出结果执行逆行位移运算的右移操作。右移后的矩阵乘以系数矩阵(0E,0B,0D,09),并调用列混合模块的电路结构完成逆列混合运算。

加密过程中,轮密钥key0~key9由AES算法的密钥扩展基于原始密钥计算产生。解密过程中,轮密钥加运算依次取轮密钥key9~key0,除去首轮和最后一轮,从RAM中取出的轮密钥需要先经进行逆列混合运算[13]。加解密流程如图4所示。

3 FPGA电路仿真实验结果

本设计采用FPGA开发平台、Cyclone II系列芯片对加解密系统进行测试与验证。系统主要包括数据输入、密钥输入和状态控制信号线,具有统一的外部时钟控制[14]。

3.1 DES 加密的实现

在加密测试文件中:

desin:000000000000000

图4 AES加/解密系统

key:0000000000000000

expout:8ca64de9c1b123a7

加密后:

desout:8ca64de9c1b123a7

由仿真图(如图5)可知:经16个时钟周期后,加密得到的最终输出desout与理论值相同,证明加密成功。

图5 DES加密仿真波形图(截图)

3.2 AES 加密的实现

在加密测试文件中:

key:00000000000000000000000000000000

plain:f34481ec3cc627bacd5dc3fb08f273e6

ciph:0336763e966d92595a567cc9ce537f5e

加密后:

test_out:0336763e966d92595a567cc9ce537f5e

同步解密后:

test_out2:f34481ec3cc627bacd5dc3fb08f273e6

由仿真图(如图6)可知:最终得到的密文与理论值相同,证明加密成功。同步解密后,还原了最初的明文,解密成功。

图6 AES加密仿真波形图(截图)

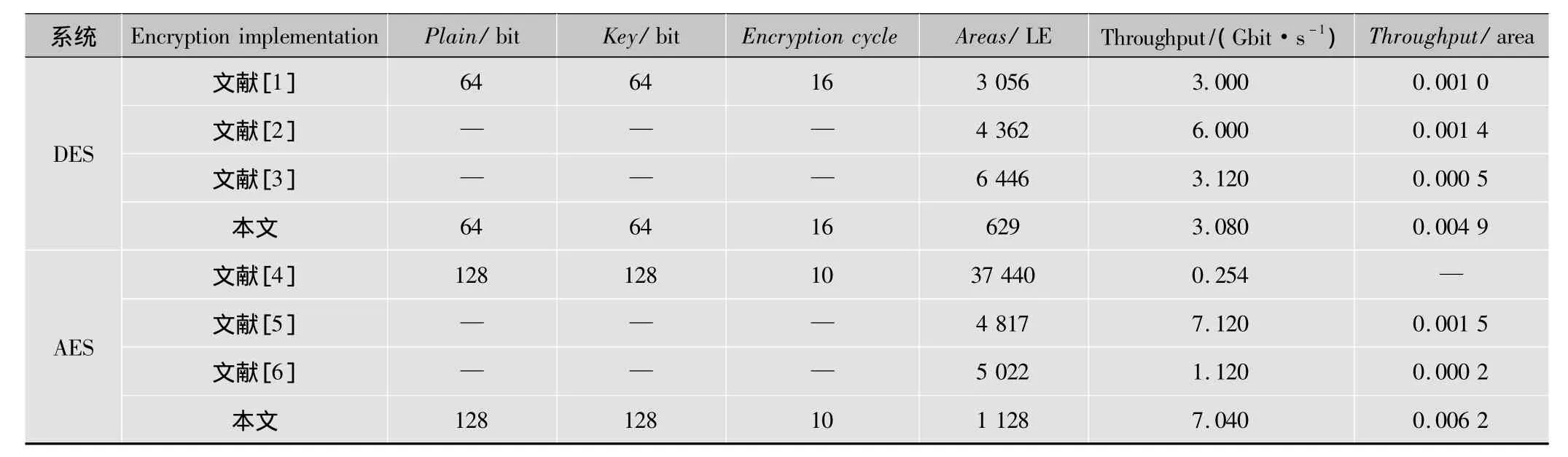

4 结果分析

结果表明:DES系统的实现仅占用了629个LE,不到整个硬件资源的6%,处理速度为3.08 Gbit/s。

AES系统的实现占用了1 128个LE,占整个硬件资源的8%,处理速度达到了7.04 Gbit/s。

表1给出了本设计的具体实验结果。

表1 实验结果

表2为本设计与一些同类设计的比较结果。

表2 本设计与一些同类设计的比较结果

由表1可知,在DES加密系统的设计中,对比文献[1-3],文献[2]中采用EP1S10芯片实现DES的硬件加密,占用了4 362个LE,加密速率为6 Gbit/s,是3个方案中相对最好的。而本设计选用EP2C35系列芯片,采用改进的方法后,硬件资源占用629个LE,约为文献[2]的0.144倍,且加密速度为3.08 Gbit/s,总体性能大大提高。

在 AES加密系统设计中,文献[5]采用 2块XC2V3000芯片实现AES的硬件加密,占用了4 817个LE,加密速度为7.12 Gbit/s,与文献[4]和文献[6]相比,文献[5]性能相对最佳。而本设计的实现设备采用EP2C35系列芯片,硬件资源占用了1 128个LE,约为文献[5]的0.234 倍,加密速度为7.04 Gbit/s,与文献[5]基本持平。

5 总结

本设计实现了一个高性能的DES和AES硬件加密系统。实验证明此系统能够节省90%的硬件存储资源,同时具有相同的抗攻击能力来保证新一代的IT安全。本设计与其他同类设计的比较结果显示,本设计可提供较高的吞吐率,并且在硬件资源方面具有明显的优势,资源占用率远低于其他的设计,实现了资源优先的设计目的。

本设计在整体性能方面(吞吐率/面积)具有明显的优越性,使用FPGA来实现加密算法将具有良好的发展前景。

[1]姚霁,刘建华,范九伦.一种密钥可配置的DES加密算法的FPGA实现[J].电子技术应用,2009,35(7):145-148.

[2]张峰,郑春来,耶晓东.DES加密算法的FPGA实现[J].现代电子技术,2008,31(7):80-82.

[3] MCLOONEM,MCCANNY JV.High-performance FPGA implementation of DESusing a novel method for implementing the key schedule[J].IEEE Proc.Circuits Devices Syst.,2003,150(5):373-378.

[4]徐柏权,王昭顺.基于AES算法的FPGA高速实现[J].信息与电脑,2009(7):98-99.

[5]周微微.DES算法的跨平台研究与实现[J].中国高新技术企业,2010(21):30-31.

[6]周建钦,何凌云.DES加密算法的密钥扩展[J].科技通报,2011(2):263-267.

[7]刘明珍.密码技术DES和RSA的比较与应用[J].煤炭技术,2011(6):176-177.

[8] YANGXianwen,LIZheng,WANGAn,etal.Design research of the DES against power analysis attacks based on FPGA[J].Microprocessors and Microsystems,2011(35):18-22.

[9]冯妮,张会新,卢一男,等.嵌入式AES加密存储器的硬件实现[J].电视技术,2013,37(3):59-61.

[10]胡春燕,易波.基于AES加密算法的S盒优化设计[J].微计算机信息,2012,10(28):358-360.

[11] JOSM,GRANADO C,MIGUEL A.A new methodology to implement the AES algorithm using partial and dynamic reconfiguration[J].the VLSI journal of Integration,2010(43):72-80.

[12]刘维杰.基于FPGA的AES加密设计[D].太原:中北大学,2012.

[13]杨晓非,赵婷.基于AES算法改进的蓝牙安全机制研究[J].电视技术,2013,37(5):106-109.

[14]唐明,张焕国,刘树波,等.AES的高性能硬件设计与研究[J].计算机工程,2006,32(8):257-259.