相位式激光测距系统关键技术探究

2014-11-15刘继勇

刘继勇,赵 磊

(西安工业大学电子信息与工程学院,陕西西安,710032)

0 引言

随着科学技术的发展进步,对激光测距系统要求的不断提高,使得用传统激光仪器设计方式方法无法满足要求。脉冲-相位式激光测距方法的推出使研究激光系统设计具有现实和长远意义。基于此种原因,为提高相位式激光测距系统的可靠性和控制精度,本文采用EP2C8Q208C8:这款FPGA芯片,完成脉冲-相位式激光测距系统测相技术的选择及硬件电路的研究任务。

1 改进的时域数字鉴相器

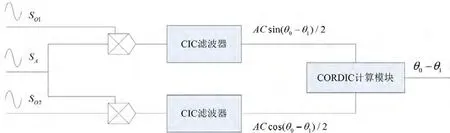

改进的时域数字鉴相器主要分为CIC滤波器模块、CORDIC相角计算模块、本振正交信号模块与乘法器模块这四个模块。

两路信号相位的测量的原理相同,图1展示的是其中一路信号相位测量原理图

图1 一路相角计算原理

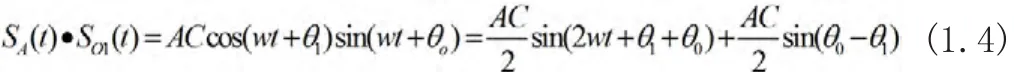

乘积的结果包括直流信号部分和二倍频部分这两部分。经过CIC滤波器将二倍频部分滤除掉,剩余的直流部分为。同时进行的操作,经过滤波器后的直流分量为两部分直流分量有相同的幅值,使用CORDIC相角计算模块就可以计算出相位差:令激光接收信号的相位为,接收信号可以表示为SB(t)=Acos(wt+θ2),同样可以测出即为发射和接收信号的相位差图中展示的两路本振正交信号是数字信号,它所对应的数字芯片有两种,一个是FPGA芯片,一个是DSP芯片,而FPGA芯片更适用于本课题进行对数字信号的处理。原因主要有三个方面:一是在数字器件内部需要选用能够同步完成数据处理的数字芯片,以便对两路数字信号进行相位测量,而FPGA芯片符合这些要求,因为该芯片是基于可编程门阵列的;二是FPGA芯片符合流水线结构实现算法,同时CIC滤波器和CORDIC算法比较适合流水线结构实现,因此大量时间可被节省;三是鉴相器的设计中需要四个高位的乘法器,大部分FPGA内部都有丰富的乘法器资源嵌入,而低型号的DSP内部一般是达不到这个要求的,并且可以自己配置FPGA内部的乘法器位数。

2 基于FPGA的鉴相器硬件电路的实现

实现鉴相器的硬件电路是本课题研究的重要内容,鉴相器硬件电路框架主要分为四个模块,分别是显示模块、FPGA最小系统模块、正弦信号发生器模块以及A/D采样模块。图2所展示的就是鉴相器硬件电路实现的整体框图:

图2 鉴相器硬件电路整体框图

A/D通道1 与A/D通道2分别负责对发射信号、接收信号进行A/D采样。采用LCD12864(由128*64个内部点阵组成)完成显示输出,能够将图形、字符、汉字等显示出来。正弦信号发生器使用的是DDS芯片AD9850,该款芯片能够进行输出信号频率与控制相位。

2.1 FPGA系统硬件设计

FPGA系统由多部分组成,其中主要包括电源模块、晶振模块、FPGA芯片、SDRAM、AS模块以及JTAG模块。为FPGA提供在线调试由JTAG口负责,SDRAM为外置的数据模块,AS将程序固化到EPCS中,上电后加载到FPGA上,稳定的3.3V和1.2V电压由电源模块负责提供。图3所展示的是JTAG模块和AS模块的硬件电路图,如下:

2.2 A/D转换模块硬件电路设计

为了满足滤波的需要,AD芯片的最低抽样频率为20MHz,经过筛选课题中选用A将AD芯片的最低抽样频率设为20MHz,以此来满足滤波的需求。经过筛选、分析,最终在课题中选用芯片AD9225来完成采样工作,该款芯片是由ADI公司生产的。图4(a)展示的是信号的管脚图,图4(b)展示的是内部结构图,如下:

图4 AD9225芯片管脚图和内部结构图

AD芯片单电源供电便于电路设计,它所具备的特点较为明显且实用,不仅高精度而且低功耗,适合用来实现数字便携式设备。

2.2.1 时序图

图5所展示的是AD9225的时序图,经观察发现AD9225在每一个时钟的上升沿完成A/D采样,控制非常简单。在高频的转换速率下采样时钟的占空比占空比为45%~55%。

图5 AD9225时序图

2.2.2 模拟信号输入范围

AD9225分别有VINA、VINB两个模拟输入引脚,电源电压决定模拟输入的范围,最大值为AVDD+0.3V,最小值为AVSS-0.3V。

2.2.3 AD9225参考电压和量程的选取

参考电压VREF决定AD9225的量程,为参考电压的二倍。SENCE引脚决定VREF的值,若SENCE与REFCOM相连,VREF是2.0V,量程是0~4V;若SENCE与VREF直接相连,VREF是1.0V,量程是0~2V;若SENCE通过电阻网络与VREF相连,量程仍为0~2VREF,而 VREF 可以是 1.0~2.0V之间的任意值 ;若 SENCE 与AVDD相连,则 VREF由外部参考电压源驱动。设计中将SENCE与REFCOM相连,即量程选择0~4V。

2.2.4 AD9255数据的提取

硬件电路设计中FPGA芯片和AD9225芯片公用一个20MHz时钟源,从而实现数据转换和数据提取的同步。

图6所展示的是A/D转换部分硬件设计的电路图,经观察得知为方便单电源A/D芯片的数据采集,经过R37和R38对输入信号进行直流偏置,将负值信号偏置到正值。

2.3 显示模块电路设计

LCD12864是一款液晶显示器,显示屏实质是128*64的点阵,内部有汉字和字符的译码器。供电电压为3.3V~5V,具有实现画面移动、光标显示、睡眠模式设定等功能。

LCD12864硬件电路,其中VR4为一电阻器,用来调节显示器的亮度。

3 结语

本文研究了相位式激光测距采用EP2C8Q208C8芯片在接收端对接收的信号同时进行相位和飞行时间的测量。这种方法实现起来比较方便,将复杂的操作转移到数字芯片内部。此外,相位测量模块使用高速A/D芯片完成4MHz的信号采样,完成脉冲-相位式激光测距系统测相技术的选择及硬件电路设计的研究任务。

[1]孔东.相位法激光测距仪的研究[D].西安电子科技大学,2007:44.

[2]王丽,许安涛,王瑛.激光器的发展及激光测距的方法[J].焦作大学学报,2007,10(4): 55-56.

[3]吴应明.便携式脉冲激光测距仪的研制[D].西安电子科技大学,2009:18.

[4]杨建.基于DDS的激光测距仪硬件研究与设计[D].国防科技大学,2008:48.

[5]黄勇.基于Pspice的仿真分析与设计[J].湖北教育学院学报,2007,10(2):13.

[6]张慧,提高相位激光测距精确度的研究[J].精密制造与自动化,2007,1(3):24-26.

[7]叶林等.相位差的几种测量方法和测量精度分析[J].电测与仪表,2006,12(4):34-37.