基于ARM-Linux的数据采集和网络传输系统设计

2014-09-25王腾飞马志峰韩福海

王腾飞,马志峰,王 昊,韩福海

(北京理工大学 信息与电子学院,北京 100081)

基于ARM-Linux的数据采集和网络传输系统设计

王腾飞,马志峰,王 昊,韩福海

(北京理工大学 信息与电子学院,北京 100081)

文中设计了一个基于ARM9处理器和嵌入式Linux OS的多路数据采集和网络传输系统。该系统以三星公司的S3C2440处理器为核心,配以DM9000百兆自适应网络控制芯片,通过互联网将由FPGA控制的多达64路AD采集通道采集的数据发送到网络终端上,实现了远程数据采集的功能。软件平台移植了最新的Linux 2.6.30.4内核,并基于Linux OS之上实现了Socket网络应用程序。随着互联网技术的不断发展,本系统在网络时代有着广阔的应用前景。

ARM9;Linux;数据采集;网络传输;Socket

数据采集是实现工业现场控制的首要环节,实现远程数据传输是目前大多数工业控制系统的普遍要求。传统的数据采集方式是把各类基于ISA总线、PCI总线或USB总线的数据采集卡与计算机相连接,将传感器输出的信号经过信号调理电路的处理后,通过数据采集卡输入到计算机中[1]。这种采集方式在不能安放计算机的场所进行将会非常困难,因此开发一套便携式的现场数据采集和网络传输系统具有十分重要的现实意义。本文基于ARM9嵌入式硬件平台和ARMLinux OS,设计了这套数据采集和网络传输系统,可以对多达64路的模拟信号进行采集和处理,并将处理后的数据传送到远程网络终端上,同时满足多客户端请求的需要。

1 系统总体设计

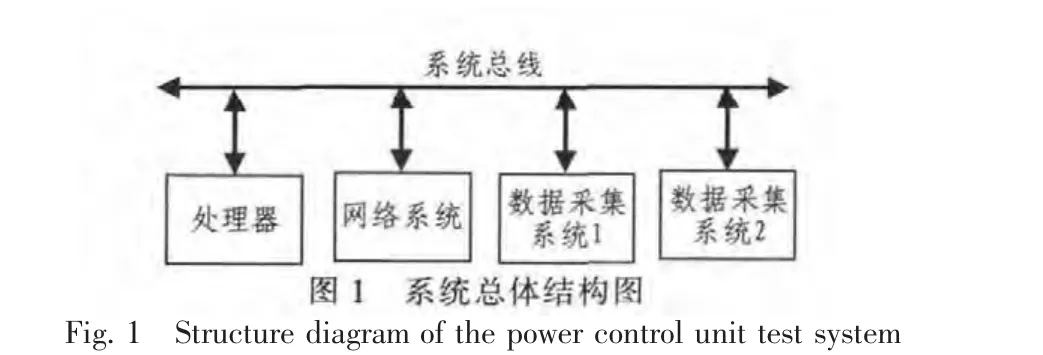

本系统从功能上可分为两大子系统:数据采集子系统和网络传输子系统。其中数据采集系统有两个完全相同的模块,它们都连接在ARM处理器的系统总线上,如下图1所示。

1.1 数据采集子系统

该系统包含两个完全相同的采集板,板上的控制核心为Altera公司的cyclone II系列FPGA。每个采集板上有4片AD芯片MAX1308,由FPGA统一控制,而MAX1308是一款8通道AD芯片,所以该系统最多可同时实现64路独立通道的数据采集功能。单通道的数据吞吐率最高可达1075ksps/通道,八通道的数据吞吐率最高可达456ksps/通道。两个采集板都挂在ARM的数据总线上,FPGA以异步FIFO存储机制与ARM数据总线进行交互。

1.2 网络传输子系统

该系统以ARM为控制核心,移植嵌入式Linux OS,网络芯片选用百兆自适应网卡DM9000EP,通过RJ-45接口接入互联网实现了数据的远程传输。基于TCP/IP协议实现了面向连接的数据流通信Socket网络应用程序,采用Linux服务器常用的C/S架构,完成了下位机的服务器程序和上位机的数据接收程序,并采用多进程编程思想解决了服务器多客户端问题。远程客户端通过配置服务器的IP地址和端口号,建立与服务器的连接后,即可请求数据,届时服务器启动数据采集系统并将采集的数据实时传送给远程客户端。

2 硬件设计

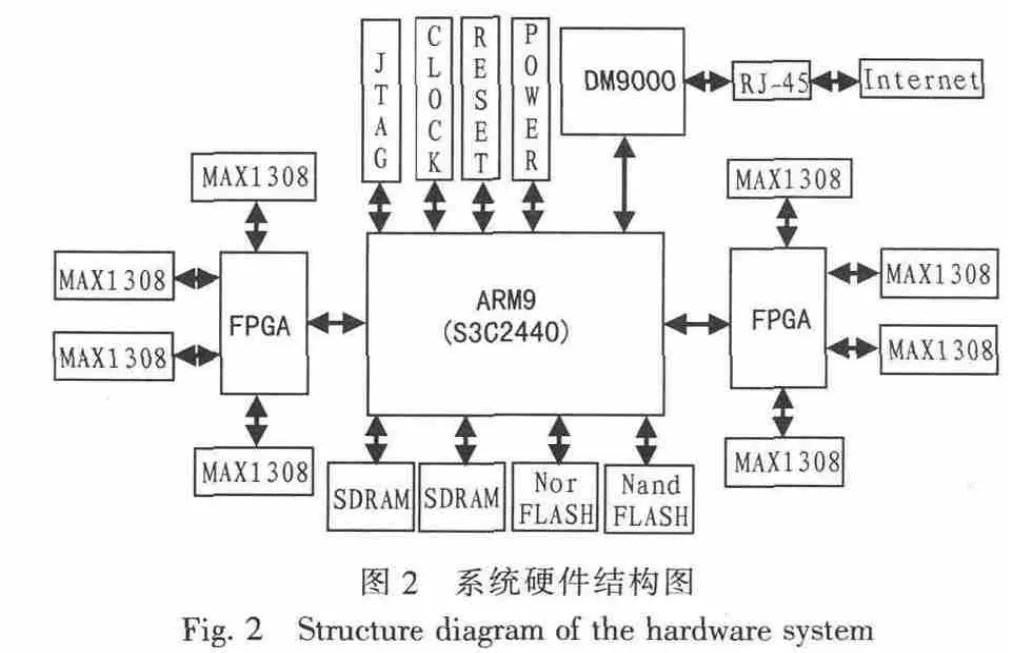

系统的硬件结构如下图2所示。以S3C2440芯片为核心,64 MB的SDRAM为系统内存,2 MB的Nor Flash和512 MB的Nand Flash为系统存储设备。两片FPGA分别连接四片MAX1308芯片作为采集设备挂在S3C2440的系统总线上;DM9000网络芯片也挂在S3C2440的系统总线上,另一端通过隔离变压器H1102与RJ-45端口与互联网相连。

此外,系统时钟源直接采用外部晶振,内部PLL电路可以调整系统时钟,使系统运行速度更快。为了提供高效的电源监控作用,选取了专门的系统监视复位芯片MAX811S,实现对电源电压的监控和手动复位操作。该芯片优良,一旦系统电源低于系统复位的阈值(2.93V),复位芯片MAX811S将会对系统进行复位。S3C2440芯片内部有JTAG核,因此可以通过外部JTAG调试电缆与系统连接进行烧写u-boot。

2.1 AD采集电路

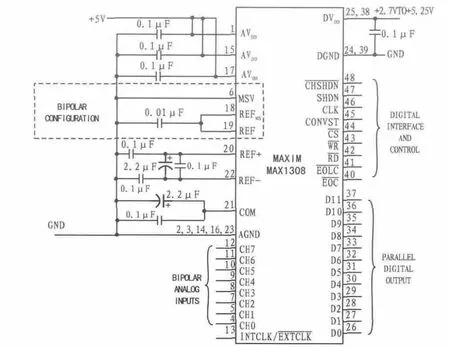

MAX1308是美信公司的一款12位8通道模数转换器,8个通道同时转换时,每个通道数据吞吐率为456ksps。独立的采样保持(T/H)电路为每个通道提供同时采样,提供输入范围,输入故障容限为,其他特性包括20 MHz T/H输入带宽、内部时钟、内部(+2.5 V)或外部(+2.0 V至+3.0 V)基准以及低功耗省电模式。20 MHz、12位双向并行数据总线用来提供转换结果,并可接受数字输入分别激活每一路通道。该器件工作在+4.75 V至+5.25 V模拟电源与+2.7 V至+5.25 V数字电源下,全速运行时,总电源电流为57 mA。

AD芯片MAX1308的电路图如图3所示。

2.2 CPU及FPGA硬件电路

图3 MAX1308电路图Fig.3 MAX1308 circuit diagram

该系统CPU为三星公司的S3C2440芯片,基于ARM920T内核,工作频率可达400 MHz,采用新的AMBA总线架构,是一款低电压、高性能的处理器芯片,片上集成众多的功能模块。S3C2440的存储器控制器共8个存储器banks,具有可编程的访问位宽,bank0(16/32 位),其他 bank(8/16/32 位),所有存储器bank的访问周期可编程。

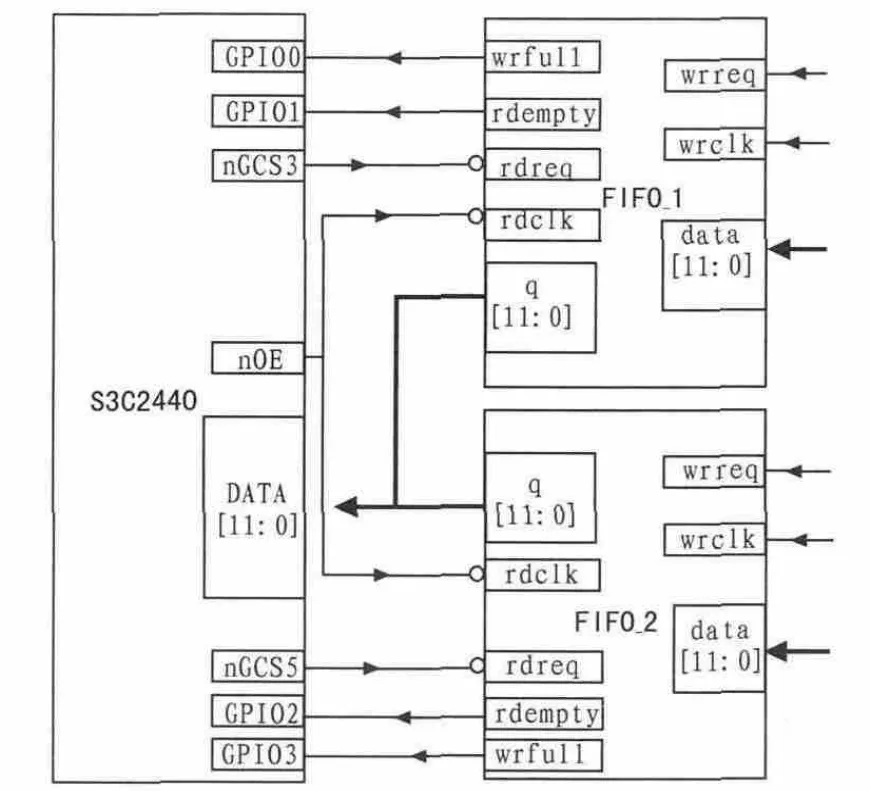

8片MAX1308由两片Altera公司的Cyclone II系列FPGA芯片控制,每片FPGA内部分为两个模块,一个为AD转换控制模块,另一个为FIFO存储模块[1]。最终两个FIFO存储器分别挂在S3C2440芯片的BANK3和BANK5上,通过数据总线,ARM处理器可以读取FIFO内的数据。ARM与FPGA(FIFO)接口电路如图4所示。

图4 ARM与FPGA(FIFO)连接方式Fig.4 Connection of ARM and FPGA (FIFO)

其中的FIFO由Quartus II提供的IP核手动配置,自动生成。FIFO的输出通过一组三态门与ARM的数据总线相连,三态门的EN端分别由nGCS3和nGCS5控制,同时nGCS3和nGCS5通过反相器分别与两个FIFO的rdreq端相连,这样ARM通过这两个片选信号可同时打开FIFO的输出通道以及读使能信号rdreq。nOE信号通过反相器分别与两个FIFO的rdclk端相连,来提供FIFO的读时钟信号。

3 软件设计

3.1 AD控制部分

MAX1308采用内部时钟的采样时序图如下图5所示。其中双向并行接口D0-D7用来设置8位配置寄存器,以激活和禁止相应的采样通道。内部时钟模式下,启动一次转换,需在采样时间(tACQ)内将 CONVST置为低电平,此时 T/H捕获信号,在CONVST上升沿转换开始。一旦能够读取转换结果,转换结束信号(EOC)将给出一个低电平脉冲。当最后一个通道的转换结果可以被读取时,最后转换结束信号(EOLC)跳变到低电平。

图5 转换过程中的读操作,内部时钟Fig.5 A read operation in the conversion process,the internal clock

FPGA内部按照上述时序逻辑实现采集模块后,再连接到FIFO模块上,然后通过一组三态门挂接到ARM数据总线上。

3.2 Linux设备驱动

设备驱动程序在Linux内核中扮演着特殊的角色,它使某个特定硬件响应一个定义良好的内部编程接口,这些接口完全隐藏了设备的工作细节。用户的操作通过一组标准化的调用执行,而这些调用独立于特定的驱动程序。将这些调用映射到作用于实际硬件的设备特有操作上,则是设备驱动程序的任务[2]。

3.2.1 FIFO设备驱动

用户空间驱动程序具有很多优点,比如可以和整个C库连接,可以使用通常的调试器调试驱动程序代码,而不用费力地调试正在运行的内核等[3]。

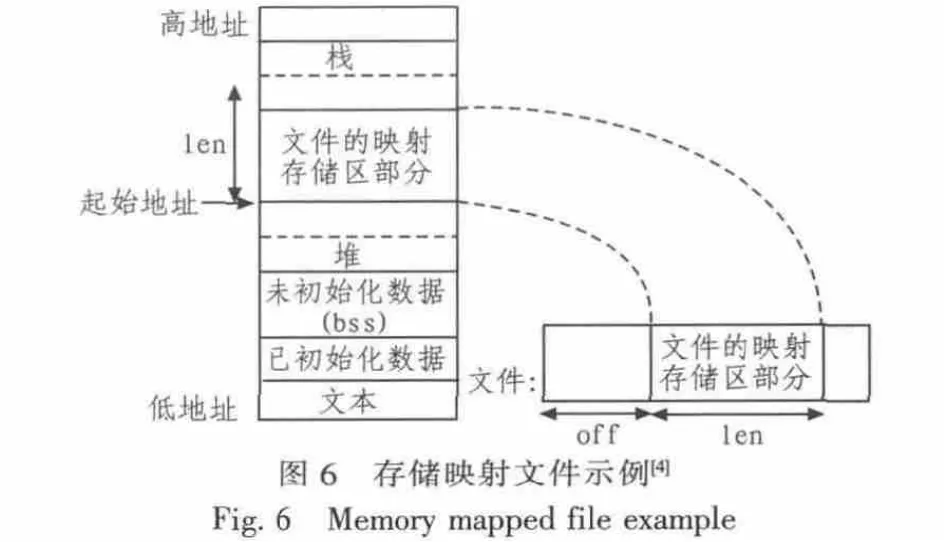

该驱动程序是通过mmap函数将外设FIFO存储器映射到用户空间的一段内存中,进而对其进行操作。映射一个设备意味着将用户空间的一段内存与设备内存关联起来[2]。mmap函数定义如下:

此函数将在进程的虚拟地址空间 (地址起始为addr,长度为len字节)和与文件描述符fd关联的文件(偏移量为off,长度为len字节)之间建立映射。映射后系统对设备的读写操作就等同于对用户内存的读写。

程序中需要对S3C2440的存储器控制寄存器进行配置,主要是BANKCON3、BANKCON5和BWSCON 3个寄存器,使BANK3和BANK5数据总线宽度为16位,WAIT等待信号无效,合理配置读写信号周期。这些同样是通过存储映射的方式实现。

3.2.2 DM9000网络设备驱动

Linux 2.6.30.4内核中的网卡驱动相当完善,其中包含DM9000的驱动,所以随着内核的移植,该驱动就可以直接使用了。

3.3 Socket网络应用程序

Linux OS之所以得到广泛应用的一个主要原因是其卓越的网络应用[5]。Socket是一种实现网络不同主机进程间通信的一种机制。

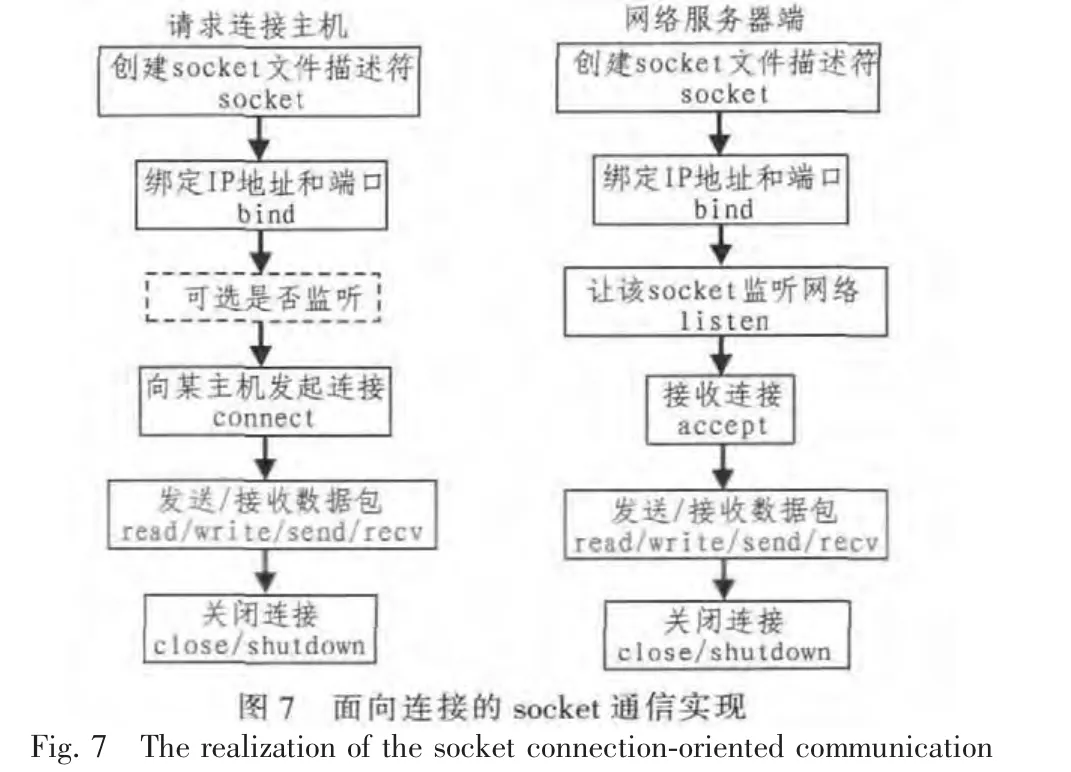

为了数据的可靠传输,我们选择基于面向连接的TCP通信协议进行应用层的开发,面向连接的Socket通信流程如图7所示。

众所周知,使用多进程的服务器模型有利于程序的健壮性[6]。下位机作为服务器端,设置listen()侦听客户端的连接请求,针对每个Socket连接请求,利用fork()函数产生一个子进程处理到来的连接,在子进程中完成客户指令的接收与判断、数据的处理与发送等[7],并关闭服务器侦听,在父进程中关闭客户端的连接,采用多进程思想,解决多客户端问题。上位机应用程序为字符界面,将接收到的数据以文件的形式保持起来。

4 系统测试实验

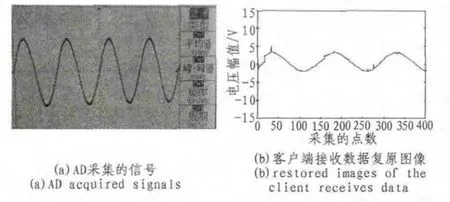

用SG1110数字合成信号发生器给采集板输入一个频率为4 kHz,峰峰值为 8.6 V的正弦波信号,如图 8(a)所示,在单通道采集的模式下将采集的一段数据传送给网络上的客户端,并将此数据用MATLAB程序画图如图8(b)所示。

图8 实验数据Fig.8 Experimental data

由上图可以看出,还原后的图像为一正弦波,每个周期的采样点数约为160个,采样频率接近640 kHz,符合预期结果。

5 结 论

嵌入式远程数据采集系统是一种新的将分散信息集中处理的有效方法,对工业控制的数据集中处理、环境监控等有非常重要的应用价值。该系统的创新点是在用户空间实现了FIFO设备驱动,最大的特点是实现了多达64通道的模拟数据采集,实现了多数据源采集的要求。系统的便携化程度高,实用性和智能性强,潜在的经济效益巨大。

[1]刘韬,楼兴华.FPGA数据电子系统设计与开发实例导航[M].北京:人民邮电出版社,2005.

[2]张顶飞,谭或,等.基于ARM的数据采集和无线传输系统[C]//第八届全国设备与维修工程学术会议暨第十三届全国设备监测与诊断学术会议论文集,2008.

[3]Corbet J,Rubini A,Hartman G K.LINUX设备驱动程序[M].3版.魏永明,耿岳,钟书毅,译.北京:中国电力出版社,2006.

[4]Stevens W R,Rago S A.UNIX坏境高级编程[M].2版.尤晋元,张亚英,戚正伟,译.北京:人民邮电出版社,2011.

[5]杨宗德,邓玉春.Linux高级程序设计[M].2版.北京:人民邮电出版社,2009.

[6]付海艳,韩山,郭云.ARM微处理器应用开发技术详解与实例分析[M].北京:清华大学出版社,2007.

[7]赵瑞国,马杰,何志勇,等.液体火箭发动机高速采集数据工程数据库设计及应用[J].火箭推进,2011(3):60-64,72.

ZHAO Rui-guo,MA Jie,HE Zhi-yong,et al.Design and application of high-speed acquisition database for liquid rocket engine[J].Journal of Rocket Propulsion,2011(3):60-64,72.

Design of data acquisition and network transmission system based on ARM-Linux

WANG Teng-fei, MA Zhi-feng, WANG Hao, HAN Fu-hai

(School of Information and Electronics, Beijing Institute of Technology, Beijing 100081, China)

This paper designs a multi-channel data acquisition and network transmission system based on ARM9 processor and embedded Linux OS.Adopting Samsung S3C2440 processor as core together with DM9000 fast adaptive network control chip,the system sends data collected from 64-channel AD acquisition channels controlled by FPGA to network terminals through Internet to achieve remote data acquisition function.The software platform ported the latest Linux kernel 2.6.30.4,and Socket web application is realized based on Linux OS.With continued development of Internet technology,the system will have broad application prospects in the Internet age.

ARM9;Linux;data acquisition; network transmission; Socket

10.14022/j.cnki.dzsjgc.2014.16.007

TN702

A

1674-6236(2014)16-0021-04

2013-10-24 稿件编号:201310175

国家“863”计划项目(2012AA041506)

王腾飞(1990—),男,安徽宿州人,硕士研究生。研究方向:电路与系统、FPGA设计。