基于众核处理器的AVS并行解码器的设计与实现

2014-09-18张文军高志勇张小云

吴 杰,张文军,高志勇,张小云

(上海交通大学 图像通信与网络工程研究所,上海 200240)

1 AVS并行解码器

AVS是我国具备自主知识产权的第二代信源编码标准,其第二部分为视频部分,在2006年经信息产业部批准正式成为国家标准[1]。AVS目前正处于大规模产业化的推广期,因此研究AVS在众核平台下的并行解码有着重要的意义。

AVS标准的视频部分与MPEG-2以及H.264类似,也采用了基于块匹配的编码框架[2]。相对于MPEG-2标准,AVS同H.264都采用了更加复杂的运动估计等技术,使得复杂度大幅增加,经过优化在主频有限的单核处理器上也难以实现高清视频(1 080p)的实时(25 f/s或更高)解码[3]。

多核以及众核处理器的发展以及并行计算为高清视频码流的实时解码提供了一种可行的解决方案,设计良好的并行解码器能达到接近线性的并行加速比。本文提出并实现了一种采用功能与数据混合并行的高清实时AVS并行解码器,并在Tilera公司的Tile-Gx36平台[4]上开发实现,可用6个核实现1路高清AVS码流的解码。

2 AVS解码器结构

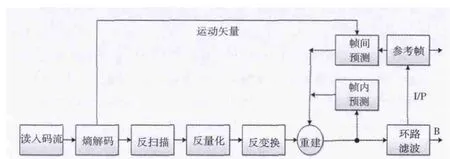

AVS的视频标准也采用了基于块匹配的混合编码框架,AVS解码器的实现流程如图1所示。

图1 AVS解码器流程图

解码器先对读入的AVS码流进行码流解析和熵解码,得到残差系数等信息,再经过一系列运算可以到残差值,然后再根据编码模式的不同选择不同的预测方式进行预测运算,再经过重建即可得到重建图像。解码得到的I帧、P帧可以作为参考帧。

3 AVS并行解码器设计方案

3.1 并行策略

利用多核处理器实现任务的并行,一般有两种常见的方法,一种是功能并行,一种是数据并行[5]。功能并行的基础是流水线模型,可以将要实现的功能拆分成多个功能模块,通过流水线并行就可以实现功能上的并行。功能并行本质上是利用时间上的并行性来实现并行加速的作用。AVS解码器可以分为VLD和IQ/IDCT,帧内预测、MV预测以及滤波等。可以对这些功能模块进行划分,然后再利用多核处理器的并行性来并行处理这些功能模块。

数据并行是将要处理的数据进行划分,将划分的数据交给不同的核处理,由此实现数据处理上的并行。对于AVS码流,每一帧的数据可以划分为多个Slice,每一个Slice可以由多个宏块行组成,本文AVS并行解码器的设计采用基于宏块行的并行。

功能并行时,多个核之间需要进行数据通信,因此会引入通信负载。而且功能并行时只有各个功能模块耗时接近时才能有更好的并行加速比。数据并行时数据之间存在依赖性关系,如果数据依赖性差,则CPU将会有很多的时间处于空闲等待状态,并行效率就会下降,所以进行数据并行时必须考虑划分数据模块的依赖性。

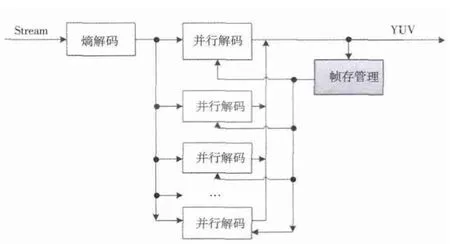

本文提出的是一种数据并行和功能并行相结合的混合模型来实现AVS并行解码器的设计。AVS解码器中熵解码与其他功能模块是串行执行的,按照这个思路可以将AVS解码器划分为两大模块,即VLD模块以及并行解码模块。VLD模块和功能解码模块之间符合流水线并行的方式,通过这种机制可以实现功能上的并行。在并行解码模块中多个核处理划分后的数据,由此实现数据上的并行。

AVS并行解码器框图如图2所示,主线程负责熵解码创建解码任务,多个线程进行并行解码。

图2 AVS并行解码混合模型框图

3.2 调度策略

本文采用任务池模型实现子任务的调度,任务池模型通常都是由主线程和工作线程组组成。主线程负责创建任务添加到任务池中,工作线程组从任务池中获取任务并执行,当工作线程执行完当前任务后,立即去任务池中获取任务再执行,直到任务池为空。采用任务池模型的动态分配方案能够减少核处于等待的时间,提高并行处理的效率。

3.3 AVS并行解码器设计

本文采用任务池模型的调度机制实现AVS并行解码器。在任务池模型中,为了高效率地实现并行,需要满足以下两个条件:1)任务池中有足够多的任务;2)任务池中的任务具备弱依赖性[6]。如果任务池中没有足够的任务,工作线程组中将会有线程处于等待状态;如果任务池中的任务依赖性过强,则这些任务只能按顺序执行。所以进行任务划分时颗粒度必须合理。在AVS并行解码器的实现过程中,采用了帧间并行和帧内宏块行并行,以保证并行解码器的效率。

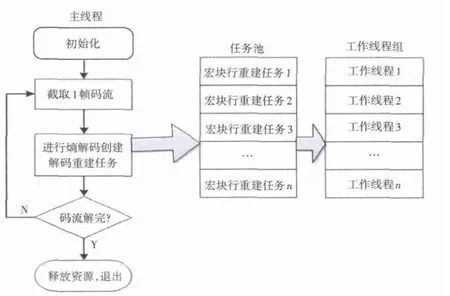

3.3.1 AVS并行解码器实现架构

整个AVS并行解码器的实现架构由主线程和工作线程组两个部分组成。并行AVS解码器的实现架构如图3所示,主线程负责解析输入码流,熵解码,创建宏块行为单位的解码重建任务并添加到任务池中。工作线程从任务池中取出一个任务做解码重建,工作流程如下:1)帧间预测亮度宏块重建;2)帧内预测亮度宏块重建;3)亮度宏块BS值计算及环路滤波;4)帧间预测色度宏块重建;5)帧内预测色度宏块重建;6)色度宏块环路滤波。

图3 并行AVS解码器实现架构

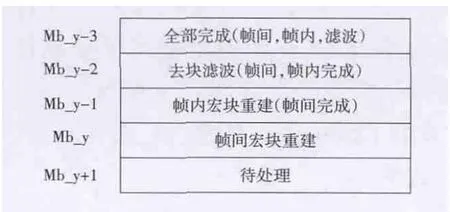

3.3.2 帧间并行和宏块行并行

如图2所示,本文设计的AVS并行解码器采用了功能并行和数据并行混合的模型,如果只用1个主线程进行熵解码,随着工作线程的增加,解码任务不足,处于休闲等待的线程数增加,并行加速比就会降低。为了解决上述问题,引入帧间并行机制来创建更多的解码任务提供给工作线程组执行。在并行解码模块的设计中,如果一个线程完成一帧所有后续数据的解码,任务颗粒度仍然较大,随着工作线程的增加,容易出现线程等待任务的情况,为此需要进行更小的颗粒度划分,本文设计的AVS解码器采用了宏块行并行的机制。根据解码的工作流程,采用了3行宏块并行的任务划分机制,考虑亮度和色度宏块,则一共可以同时处理6行宏块,如图4所示。Mb_y行宏块进行帧间宏块的重建时,其上一行Mb_y-1行宏块已经完成帧间宏块的重建,正在进行帧内宏块的重建,而Mb_y-2行则已经完成帧间宏块重建和帧内宏块重建,正在进行去块滤波。

图4 宏块行并行框图

4 解码器优化

对于AVS-P2视频解码器而言,反量化、反变换以及插值模块消耗的大多数时间,为了实现高清实时解码,除了充分利用多核的并行性外,还需要利用处理器提供的单指令多数据(SIMD)指令集进行计算的优化。

4.1 开发平台介绍

Tile-Gx36是美国Tilera公司2012年发布的众核处理器,它是由36个核组成的,每个核的频率是1.2 GHz。核间的通信主要是通过核间互联网络imesh完成。Tilera提供的SIMD指令集能完成16位和8位的SIMD操作。Tilera的寄存器宽度为64位,所以可以同时处理4个16位的运算或者8个8位的运算。

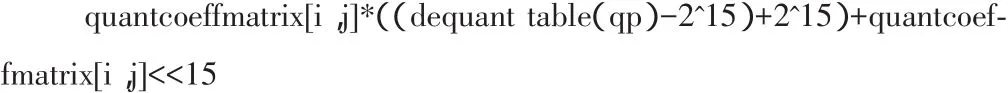

4.2 反量化/反变换SIMD优化

AVS反量化表64个整数均大于32 768,只可用无符号16位表达,最高位均为1。而Tilera公司提供的SIMD指令集仅支持有符号16位的乘法运算,为了使用Tilera公司提供的乘法指令,将反量化表中的每个数减去32 768,用有符号位表示。对反量化公式做如下修正

1个像素块的残差一般是用8位表示的,AVS变换矩阵的系数值较大,如果用8位来表示,变换计算的中间结果可能会发生溢出,所以在进行中间运算的时候需要进行数据扩展,第一次运算将数据由8位扩展到16位,第二次运算将数据由16位扩展到32位,最后将输出结果压缩为16位的整型数据。Tilera提供的SIMD指令集提供了相应的数据位扩展和压缩指令。

4.3 插值SIMD优化

AVS解码器与H.264的样本插值不同,采用的是4抽头滤波器进行样本插值。从AVS的插值流程能够看出,对于类似同位置的像素点,进行的运算相同,因此可以利用SIMD指令并行处理。考虑到并行处理过程中会发生数据位溢出,需要将8位扩展为16位整型数据进行计算。AVS参考软件采用了大量的循环来计算每个分像素的值,执行这些循环会引来额外的负载。利用SIMD指令除了可以并行处理数据提高速度外,还很大程度地减少了循环次数,极大地提高了运行速度。

5 实验结果和分析

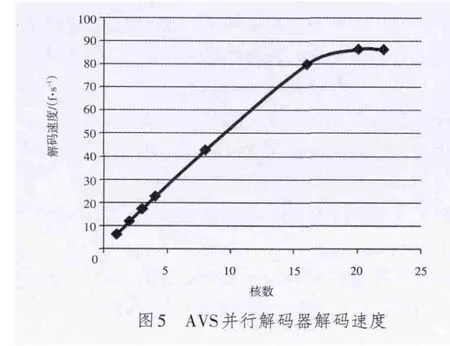

实验采用的测试码流为用AVS参考软件rm52j编码的1 080p码流,编码方式为IBBP,码率为10 Mbit/s。未做任何优化前,单核解码速度为2.9 f/s,经过优化后单核解码速度为6.1 f/s。采用5帧并行以及宏块行并行,解码速度与核数之间的关系如图5所示。采用帧级并行和宏块行并行的情况下6个核可以实现30 f/s的解码速度,达到高清实时的解码。

从图5中可以看出,当核数小于15时,有着接近线性的并行加速比,核数再增加,解码速度不会继续增加。这是由于主线程创建的解码任务有限,随着核数的增加,核间通信的负载增加,处理器实际解码的时间减少。

6 总结

本文设计并在Tile-Gx36平台上实现了AVS高清实时并行解码器,并行机制采用了帧级并行和宏块行并行的二级混合并行机制,调度方式采用了基于任务池的调度策略。实验表明,本设计有着良好的并行加速比,对于10 Mbit/s的1 080p的AVS码流,6个核可以实现实时解码。因此,1片Tile-Gx36可以实现6路AVS高清码流的实时解码。

:

[1]GB/T20090.2—2006,信息技术先进音视频编码第2部分:视频[S].2006.

[2]黄铁军,高文.AVS标准制定背景与知识产权状况[J].电视技术,2005,29(14):4-7.

[3]牛旭宁,张远,马思伟,等.AVS解码器复杂度分析[J].计算机应用与软件,2010,27(5):67-70.

[4]Tilera[EB/OL].[2013-10-20].http://www.tilera.com.

[5]叶朝敏,陈颖琪,高志勇.基于多核处理器的高清实时MPEG-2—H.264转码器设计[J].电视技术,2012,36(21):15-19.

[6]田韬,李鹏,张悠慧.H.264并行解码的设计与实现[J].微计算机信息,2008(14):114-115.

作者简介:吴 杰(1990—),硕士生,主研视频编解码;

张文军(1963—),博士生导师,主要研究方向为图象通信与多媒体技术、高清晰度电视等;

高志勇(1957—),博士生导师,主要研究方向为高速视频图像处理、数字电视等;

张小云(1977—),硕士生导师,主要研究方向为视频编解码、高速视频处理等。

责任编辑:时 雯 收稿日期:2013-11-14