基于FPGA的实时视频图像几何校正系统设计

2014-09-17陈文艺

陈文艺,田 科,周 娟

(西安邮电大学通信与信息工程学院,陕西西安 710061)

基于FPGA的实时视频图像几何校正系统设计

陈文艺,田 科,周 娟

(西安邮电大学通信与信息工程学院,陕西西安 710061)

基于后向映射查找表结构的几何校正算法的研究,针对双线性插值算法的特殊性,提出了四邻域像素的图像存储和插值方法,实现了图像插值时对静态存储器SRAM的快速随机读写。根据该方法设计的基于FPGA的实时视频图像几何校正系统的视频延时小于一帧,只需要改变视频图像的后向映射查找表,就可实现不同映射的视频图像几何校正。

FPGA;SRAM;几何校正;图像处理

【本文献信息】陈文艺,田科,周娟.基于FPGA的实时视频图像几何校正系统设计[J].电视技术,2014,38(3).

在军事侦察、大视场、航天和航空摄影、医疗视景等众多领域中,经常会对存在几何畸变的视频图像进行必要的畸变校正,同时还需要对采集的视频图像进行实时的处理[1]。由于图像几何校正的算法复杂灵活,视频图像处理涉及的数据量庞大,因此在视频图像处理时对硬件设计系统在运行复杂算法、处理大量数据方面有很高的要求,以便满足系统的实时性、高效性和稳定性。随着FPGA的制造工艺和集成技术的迅速发展,采用FPGA的数字硬件系统越来越体现出其在图像处理中的优越性[2]。本文提出的基于FPGA的实时视频图像几何校正系统,使用VGA视频采集卡作为图像采集设备,利用Altera的Stratix II系列FPGA芯片将输入的视频图像进行存储、几何校正处理和显示。从硬件系统设计的角度出发,采用四邻域存储图像技术结合后向映射查找表和双线性插值方法,以FPGA+NIOS II处理器组成的结构实现了对实时视频图像的输入、几何畸变校正处理和输出。

1 系统原理与基本结构

系统的基本结构如图1所示,根据设计要求,将系统划分为5个组成模块:视频图像输入模块、图像数据存储模块、预畸变系数存储模块、FPGA图像处理模块、视频图像输出模块。FPGA作为系统的核心控制芯片,SRAM A、SRAM B作为视频图像数据存储器,SRAM C用于存储后向映射查找表。

图1 几何校正系统的功能框图

外部设备(如CMOS传感器)以60 f/s(帧/秒)的速度输入视频图像数据,图像输入模块将采集的视频图像转换为Avalon-ST视频流信号,通过FPGA的控制按照四邻域的格式缓存至片外的SRAM A、SRAM B帧存储器中。预畸变系数以后向映射坐标的方式存储在片外SRAM C存储器中,FPGA通过查表SRAM C获取后向映射坐标,根据坐标计算出访问SRAM A、SRAM B的读地址,按乒乓方式轮流读出SRAM A、SRAM B中视频图像的像素数据。FPGA图像处理模块根据图像的像素数据值和插值权值完成双线性插值运算,得到预畸变图像的像素值。视频图像输出模块将插值结果后的图像数据转换数字视频图像,并同步产生VGA输出显示的控制时序。

2 系统结构设计

2.1 视频图像输入

在数字图像处理中图像的输入是关键的一步,直接影响图像处理的性能。本系统接收的数字视频图像格式为VGA(Video Graphic Array)格式。依据VGA视频格式时序标准,800×600分辨率的视频图像显示一行像素包含1 056点,其中800点为有效显示区,256点为消隐区;同理显示一帧图像有628行,其中有效行显示为600行,消隐行显示为284行。行、场扫描时序图如表1所示。

表1 行、场扫描时序

视频图像输入模块将接收的数字视频图像VGA格式转换为满足Avalon-ST视频处理协议的视频流,以方便后续以视频流的形式存储和传输数据。在系统设计时需要将外部50 MHz的时钟经过FPGA内部锁相环PLL得到所需要的40 MHz像素时钟,并利用Avalon-ST接口进行视频处理,输出标准的串行数据流。采用Avalon-ST接口处理图像和视频数据极大地提高了系统的处理速度[3]。

2.2 图像数据的存储

2.2.1 预畸变系数存储器SRAM

基于后向映射查找表的几何校正方法区别于传统的提取控制点得到函数关系式的校正方法,具体区别为:1)将标准图像与畸变图像空间坐标的映射关系以查找表的形式存储;2)按照逐行逐像素的顺序查找映射表获取理想图像在畸变图像空间中的几何位置[4-6];3)通过MATLAB软件完成算法功能,仿真得到预畸变图像系数(具体算法实现见文献[6]。

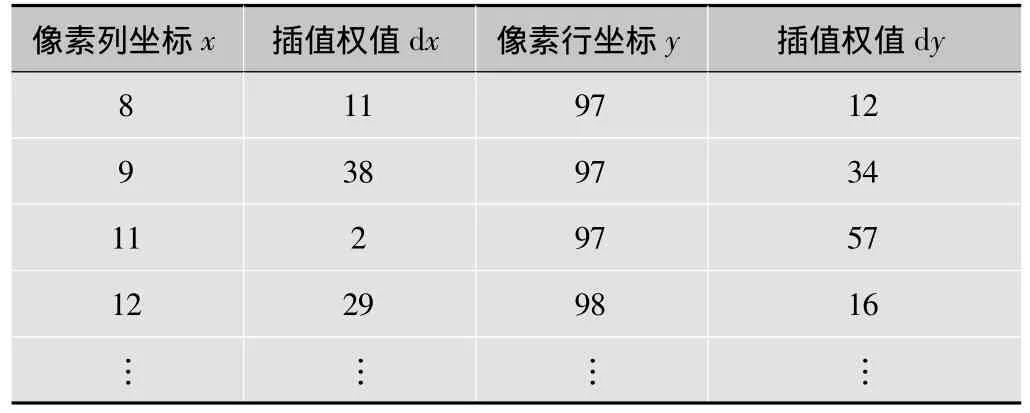

如表2所示,预畸变图像系数由x,dx,y,dy四部分组成,其中x,y分别代表该像素的列坐标和行坐标,dx,dy代表的是量化后的双线性插值的权值。坐标(x+dx,y+dy)表示当前输出的目标图像像素点映射回原图像空间中的像素坐标[7],如图2 所示。

表2 后向映射坐标的存储结构

2.2.2 图像存储器SRAM

视频图像数据的存储方式是该系统最重要的设计思想之一,由于视频图像数据量大,实时性要求高,需要大量的存储空间及较高的运算速度。SRAM控制简单,只要给出读写地址就可以进行数据的读写操作,适合随机数据的读写,因此,为了加快外部存储器的访问速度、减少帧缓存的延迟时间,最终选用SRAM作为外部存储器[8-9]来缓存视频图像数据,同时提出了以存储空间换取存储时间的设计思想。

图2 4邻域像素的位置示意图

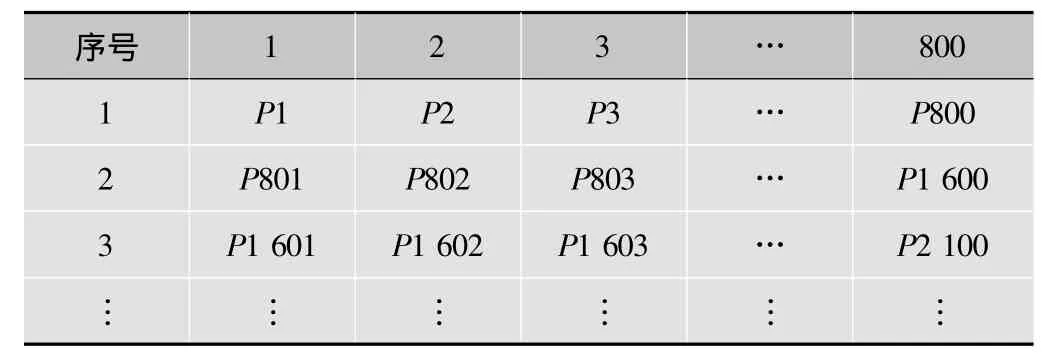

图像像素的排列格式如表3、表4所示,由于双线性插值运算是利用周围4个相邻点的灰度值,在2个方向上作线性内插以得到采样点的灰度值,因此,图像存储器SRAM将输入图像双线性插值运算所需的4个像素数据存储在同一个地址单元,每一次读取插值的4个像素仅需要一个时钟周期信号。四邻域像素存储格式就是以4倍的存储空间使像素的寻址效率提升了4倍,最大限度地提高了FPGA的运算速度,降低帧存储的延迟时间,降低系统总体功耗。

表3 图像像素的原始排列格式

表4 图像像素的4邻域存储格式

1)SRAM存储器按照图像像素的原始排列格式,如表3。如果要计算P1、P2、P801、P802四个像素点的双线性插值运算,这4个像素点分布在相邻的两行和两列,因此要给出2个不同的行地址和列地址,即地址(1,1)、(1,2)、(2,1)、(2,2),才能得到需要插值的 4 个像素点值。这样每次FPGA需要向SRAM发出4次地址信号才能得到一组双线性插值所需的数据,这将增加系统的访问开销,降低系统的性能。

2)SRAM存储器采用四邻域存储格式,如表4。将每次图像插值所需的4个像素数据存储在相同的地址单元,只要给出相应的地址便可一次读取出4个像素数据,完成相应位置的双线性插值操作。计算P1、P2、P801、P802四个像素点的双线性插值运算,FPGA只需要向SRAM发出一次地址(0),可以忽略图像的行列而一次从SRAM中读取P1、P2、P801、P802四个像素点数据进行双线性插值运算。因此,图像存储器采用四邻域的存储方案,极大地提高了像素数据的读取效率,保证系统的实时性要求。

2.3 FPGA视频图像处理系统

实时视频图像几何校正系统既需要运行复杂灵活的算法又需要大量的预处理操作,因此采用NIOS II处理器加FPGA控制及处理单元的架构,如图3所示。输入的视频图像信号源是单色数字视频图像,通过VGA接口直接送入FPGA。视频图像的输出采用ADV7125作为D/A转换器,并控制图像经VGA接口输出至图像显示设备。

图3 几何校正系统的FPGA实现框图

FPGA硬件系统分为两部分,一部分是利用SOPC技术配置的NIOS II系统,另一部分是几何预畸变电路。其中NIOS II系统主要负责系统的调度以及读入和写入后向映射表数据的工作。几何预畸变电路则是整个视频图像几何校正系统的核心处理单元,主要完成单色数字视频图像的接收和缓存,插值运算以及VGA输出显示控制[3-4]等工作。工作原理如下:

1)NIOS II处理器通过JTAG-UART接口将后向映射表数据读入系统,然后系统再将其写入到Flash中;

2)系统再次上电后将Flash中的后向映射表读至SRAM C中存储;

3)切换SRAM C到处理电路,NIOS II系统通过PIO端口启动几何预畸变处理电路,对输入视频图像进行实时的几何预畸变处理,并将处理结果送入ADV7125进行数模转换;

4)将数模转换完成后的数字视频图像和行、场同步信号一起输出至VGA接口显示。

3 仿真实现及分析

本设计是基于Quartus II 9.1和ModelSim6.5进行仿真验证的,采用的芯片是 StratixII系列 EP2S30F484I4[10]。为了确保设计的正确性和可行性,对整个系统的Verilog HDL设计进行综合仿真调试[11],仿真结果如下文所示。

3.1 Avalon-ST接口模块仿真

Avanlon-ST接口在Modelsim仿真器中的仿真结果,如图4所示。输入VGA视频信号有:vid_data视频数据、vid_valid视频数据有效信号、vid_hsync行同步信号、vid_vsync帧同步信号;输出为Avalon-ST视频流信号,video_data数据信号,video_start、video_end和 video_valid分别是帧开始、帧结束和帧有效3个控制信号。

图4 Avalon-ST接口仿真结果(截图)

3.2 几何预畸变电路仿真

如图5所示,预畸变电路的整体仿真结果中可以看出视频图像数据被按帧分别缓存至A、B两组SRAM帧存储器,再通过查表操作获取后向映射坐标以完成图像插值运算,最后将灰度结果以VGA信号输出。

图5 预畸变电路仿真结果(截图)

3.3 几何预畸变结果

800×600分辨率的视频图像通过VGA接口输入到FPGA,进行实际测试。通过显示器观察,输出结果与预期结果基本吻合,其可靠性和正确性得到验证。图6为几何校正系统输出的预畸变图像,上图为标准的800×600分辨率图像,下图为系统输出的预畸变图像。

图6 几何校正系统输出的预畸变图像

通过数字投影仪,将几何校正系统输出的几何预畸变图像投影至对应形状的非平面屏幕,即可将其显示为无畸变的投影图像,从而最终实现了对投影至非平面屏幕的数字视频图像的实时几何校正。

4 结论

目前,该系统已经实现了对数字视频图像的实时几何校正且已投入到实际的工程应用中,工作时钟频率为40 MHz,处理800×600分辨率、帧速率为60 f/s(帧/秒)的单色数字视频图像。

与传统的基于PC机平台的视频图像处理系统相比,本系统具有以下特点:

1)实时性强。由于传统的PC机平台采用的算法是串行的,每个运算过程需要等待当前运算完成后才可以开始;而FPGA内部的处理均是并行的,可以在算法设计的过程中加入流水线或采用乒乓操作等给算法加速,在操作互不依赖的时候可同时进行运算。

2)设计灵活、实用性强。本系统的设计集成度高,运行算法时间短,处理图像延时小于一帧,只需要改变视频图像的后向映射查找表,就可实现不同映射的视频图像几何校正。

3)结构简单、可灵活定制。FPGA内部资源丰富,可进行诸如防抖动、滤波等图像的前期处理,此外FPGA具有丰富的IP核可供使用,可在此设计基础上完成更高分辨率的几何校正算法实现。

:

[1]王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-35.

[2]张杰.基于FPGA的数字图象处理[D].武汉:武汉科技大学,2009.

[3]宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):45-47.

[4]周秉锋.一个基于线性变换的数字图像自由拉伸算法[J].北京大学学报:自然科学版,1997,33(6):770-775.

[5]张森.数字图像几何畸变自动校正算法的研究与实现[D].上海:上海交通大学,2007.

[6]王健,陈文艺,王波,等.投影图像畸变的一种校正方法[J].西安邮电学院学报,2011,16(1):65-69.

[7]EADIE D,SHEVLIN F,NISBET A.Correction of geometric image distortion using FPGAs[EB/OL].[2013-05-06].http://wenku.baidu.com/link?url=xfFzJetNn5RVFBUyd562wyWFbSE23AtPUttQI-04vPsiTX2eYFa8u-NhRKGQ4e2vn5XBsMWL-LhuTrs1znUMlkrYAh04gVam3dPFMBM-nLW.

[8]CY7C1061AV33 Datasheet[EB/OL].[2013-04-30].http://www.alldatasheet.com/view.jsp?Searchword=CY7C1061AV33-10ZXI.

[9]向厚振,张志杰,王鹏.基于FPGA视频和图像处理系统的FIFO缓存技术[J].电视技术,2012,36(9):41-43.

[10]Stratix II Device Handbook[EB/OL].[2013-04-28].http://wenku.baidu.com/linkurl=14RVBCI0BiYCNV_z9eBVn6yeKKjeDjqltr7tQ7C4v-6LIuH9pLd603eJlsNbJFcnhYElGL94gCxETfnIm9uILlUvYgaTVvv1L80 a8Qrgrxa.

[11]夏雨闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

Real-time Video Images Geometric Correction System Based on FPGA

CHEN Wenyi,TIAN Ke,ZHOU Juan

(Department of Communication and Information Engineering,Xi'an University of Posts and Telecommunications,Xi'an 710061,China)

Based on research of backward mapping lookup table architecture for geometric correction and the particularity of bilinear interpolation,the image storage and interpolation method of four neighborhood pixels is put forward.And it realizes how to make use of the frame buffer technology of four neighborhood images to achieve fast random access to SRAM.According to this method,the video delay of real-time image geometric correction system based on FPGA is one frame less than before.Only modification on video image backward mapping lookup table architecture is required to realize different video image projections geometric correction.

FPGA;SRAM;geometric correction;image processing

TN492

B

陈文艺(1964— ),教授,主要从事通信集成电路设计、视频图像实时处理及传输的研究;

田 科(1984— ),硕士生,主研物联网技术与应用;

周 娟(1989— ),女,硕士生,主研物联网技术与应用。

责任编辑:魏雨博

2013-06-01