基于FPGA及MCU的AVS编码器设计

2014-09-17王悦,陈涛,张刚

王 悦,陈 涛,张 刚

(太原理工大学通信与嵌入式系统实验室,山西太原 030024)

基于FPGA及MCU的AVS编码器设计

王 悦,陈 涛,张 刚

(太原理工大学通信与嵌入式系统实验室,山西太原 030024)

实现了对视频图像数据的采集﹑调度﹑实时编码及传输等功能。以FPGA实现的MCU为主控制器,对采集来的视频信号进行数据调度,将编码后的数据经I2C总线发送至上位机软件,同时对读取的码流解码,最终在PC终端上显示。根据硬件平台的结构特性,设计采用流水线结构对系统进行优化,保证了系统运行的高效性,实现了资源的最优化利用。在Xilinx Virtex-5的FPGA上实现并验证,系统可达的最高工作频率为170 MHz,且满足I帧的实时编码要求,实现高精度﹑高可靠性的AVS采编传输系统。

AVS;MCU;编码;流水线;FPGA

在实际生产和科学研究等多方领域,大数据处理需求日益凸显,MCU作为一般数据处理系统的主控单元,以其灵活性、实时性及智能化得到普遍青睐。但受到MCU处理速度的限制,其只能用于数据量小、工作频率较低的数据处理系统。而FPGA的高时钟频率﹑灵活的编程配置、较小的延迟等特性,有效地弥补了MCU的不足。

本设计在FPGA上实现MCU,并将数据采集控制﹑数据缓存﹑数据编码及数据传输集成在同一个FPGA上,完成了由MCU控制处理的片上视频编码系统。同时利用流水线技术对MCU进行优化,进一步提升了控制器的运算处理速度。在FPGA上用VHDL语言描述实现了整个系统的操作流程,并在Xilinx Virtex-5 FPGA上验证了该系统的高效性与稳定性。

1 系统总体设计

本设计以FPGA为系统平台,将MCU作为主控制器完成图像的实时采集﹑编码及传输,系统主要分为4个模块:视频采集模块﹑数据调度模块﹑编码模块和I2C总线模块,系统原理框图如图1所示。

图1 系统原理框图

具体工作流程:复合视频信号经前端视频采集模块输入整个系统,在前端视频采集模块内完成数字信号格式的转换,转换后的数字信号由MCU控制器调度实现与编码模块的通信,编码模块收到原始数据后按编码算法对数据编码,并将编好的码流重新交由MCU控制器处理,MCU收到码流时将激活I2C总线模块,由其将结果返回至AVS播放模块,完成显示操作。

2 功能模块设计及实现

2.1 前端视频采集模块

用TVP5150PBS型号的视频解码器作为前端视频采集模块,它将输入的PAL视频信号转换成YUV格式的数字信号[1]。

系统启动后,由MCU控制器对视频解码器初始化,输入复合视频信号后,视频解码器即可向MCU控制器正确输出8位的YUV数字信号。MCU收到8位的视频信号后,再对其进行信息提取等操作。

2.2MCU控制器模块

MCU是整个视频系统数据处理的核心,MCU控制器负责将8位视频信号中的行场同步信息提取出来,将相邻的亮度和色差信号转换成16位的视频信号。同时MCU还控制数据的调度,完成编码模块原始数据的输入,以及编码后返回码流的处理。

图2 数据转发电路

用FPGA上实现的MCU控制器进行大数据量的处理有着明显的优势,既有MCU的智能性﹑实时性﹑灵活性,又有FPGA的延迟小﹑配置灵活﹑速度快等特性。并且在本设计中,考虑到对大数据量处理系统的进一步优化,在MCU控制器中加入流水结构,加快解析速度,提升数据处理频率[2]。

对于无流水结构来说,输出延迟不会影响整个系统操作,但流水结构电路,若输出结果需要反馈,则延迟将会导致系统“数据相关”的出现,成为系统不稳定甚至错误的主要原因。因此流水结构设计中,“数据相关”冲突是最关键的问题[3]。设计中实现了一种数据转发电路,用以解决“数据相关”问题的出现,并在验证时得到了较好的效果。数据转发电路如图2所示。

将产生数据相关的输出结果提前转发给相关模块,然后再按流水顺序输出,完成该级流水操作。

2.3 I帧编码模块

编码模块包括帧内预测、变换量化、熵编码、残差、重构及CBP[4]。其结构如图3所示。

图3 I帧编码模块结构框图

1)帧内预测

以宏块为基本单元进行预测,主要完成参考值的选定和预测。预测时要先通过MCU控制器获得原始数据,再从上面相邻宏块获得预测时用到的25个上边界数据和左边宏块的16个右边界数据。对于预测模式的选择,采用多种模式并行的方式,每个时钟对一个像素点进行预测,同时计算SAD值[5]。当所有预测模式的SAD值计算完后,将SAD值最小的预测模式作为最佳预测模式,并将其输出给CBP。预测后的数据与原始数据相减再经量化得到残差量化数据,反量化后与原始数据相加得到重构数据,将重构数据中的边界数据提取,作为下一块预测的边界输入。该部分采用流水技术[6],处理速度快、工作效率高。

2)变换量化

主要实现DCT变换、量化、反量化、反 DCT变换[7]。DCT的实现采用蝶形算法,将运算中涉及的乘法操作以移位和加法实现,提高了运算效率。由于该部分运算量巨大,最耗费时间资源,因此采用并行操作提高执行速度。

对于色度来说,其算法与亮度相同,因此该部分不需做重复设计,只需将色度数据直接输入计算,降低了资源的耗费,提高资源利用率。

3)熵编码

该部分用于实现zig-zag扫描、游程编码、码表查询、码表切换、哥伦布编码和码流拼接[8]。对量化后的数据进行zig-zag扫描,当扫描后的结果全为0时,不对该块采用熵编码,不作处理等待下一次的扫描结果;当扫描结果不全为0时,对该块进行熵编码操作。

码流拼接部分要将编码结果以8位数据形式输出。由于(level,run)编码的码字长度不定,因此需要根据前面码字长度信息对当前码流拼接然后输出。图4给出实现码流拼接的状态转移图。code_num为已编码字,numbits为码字长度。

图4 码流拼接状态转移图

2.4 I2C总线及AVS播放器

I2C总线实现编码后码流上传到PC终端,总线上只挂载MCU控制器(作为发送器)和PC终端(作为接收器),由MCU控制器激活I2C总线进行数据的上传。在本设计的基础上设计了一种AVS解码器,根据该解码器同时基于DirectShow架构,实现了一种PC终端上的AVS播放器,用来验证本设计的编码器编码效果。

3 仿真验证与分析

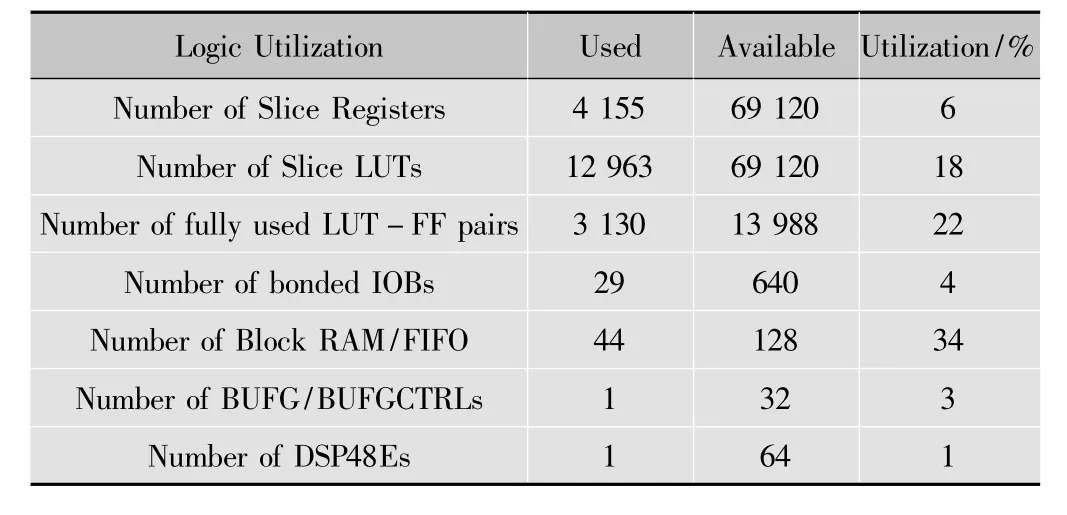

本设计采用ISE开发环境,运用VHDL硬件描述语言实现编程,并在XST和ModelSim中进行了逻辑综合和功能仿真。选择目标器件为xc5vlx110t-1ff1136,顶层模块综合结果见表1。

表1 顶层模块综合资源表

综合结果显示,系统最高工作频率可达170 MHz,对图像实时编码要求25 f/s(帧/秒),当工作时钟频率为100 MHz时,对一个宏块处理的周期数应在10 101个周期之内,本设计的编码系统工作在100 MHz时钟频率时,完成一个宏块的编码需要5 300个时钟周期,达到了实时编码的标准,验证了系统的实时性与可靠性。

图5给出VS编解码软件在qp=36时,I帧编码后输出的码流,图6为本设计在相同情况下,编码后输出的码流。从图中结果可以看出,2种实现方式的输出结果相同,从而证明了本设计的正确性。

图5 VS编解码软件输出码流结果(截图)

图6 AVS编码器输出码流结果(截图)

图7给出了本设计完成一帧图像编码上传至AVS播放器后的显示图像。

图7 编码图像的显示验证

4 总结

设计实现了FPGA上AVS全I帧的实时编码。以FPGA上实现的MCU为主控制器,完成视频数据的调度与编码,并将编码后的数据发送至PC终端的AVS解码播放器中完成显示。系统加入流水线技术实现进一步优化,并在适当的功能实现部分采用并行技术,实现了系统的高效运行,资源的最优化利用。经实验验证,系统可达到实时编码要求,运算速度快、编码正确稳定、可靠性高。同时系统的灵活性为设计的实际应用提供了可行性。

:

[1]赵慧荣,张刚.AVS全I帧视频编码器的FPGA实时实现[J].电子技术应用,2012,38(9):39-41.

[2]张刚,张博,常青.SoC系统设计[M].北京:国防工业出版社,2013.

[3]张杰.基于FPGA的八位RISC CPU的设计[J].微计算机信息,2006,12(2):155-157.

[4]杜娟,丁丹丹,虞露.基于FPGA的可重构视频编码器设计[J].浙江大学学报:工学版,2012,46(5):905-911.

[5]刘畅,熊付荣.AVS解码器帧内预测并行自适应硬件实现[J].电视技术,2009,33(S2):51-53.

[6]邹涛,杨秀芝,陈建.基于FPGA的AVS视频解码帧内预测的设计和实现[J].电视技术,2012,36(20):41-44.

[7]黄友文,陈咏恩.AVS反扫描、反量化和反变换模块的一种优化设计[J].计算机工程与应用,2008,44(19):93-95.

[8]刘群鑫.AVS中可变长解码器的硬件设计[J].现代电子技术,2007,30(23):185-187.

Design of AVS Encoder Based on FPGA and MCU

WANG Yue,CHEN Tao,ZHANG Gang

(Laboratory of Communication and Embedded System,Taiyuan University of Technology,Taiyuan 030024,China)

The functions of video image data acquisition,scheduling,real-time coding,transmission and so forth are achieved in this design.With the MCU implemented on FPGA as the master controller,the video signals acquired are scheduled and the encoded data are sent to upper computer software through I2C bus,at the same time the readed code stream are decoded,and finally it is displayed on PC terminal.According to the structure characteristics of hardware platform,pipeline architecture is utilized in this design to optimize the system,which ensures the high efficiency of the system operation and the optimal utilization of resources.Implemented and verified on Xilinx Virtex-5 platform,the maximum frequency of the system can be up to 170 MHz,meeting the real-time encoding demand of I frame and achieving the AVS acquisition and encoding transmission system of high accuracy and high reliability.

AVS;MCU;encoding;pipeline;FPGA

TN919.8

B

【本文献信息】王悦,陈涛,张刚.基于FPGA及MCU的AVS编码器设计[J].电视技术,2014,38(3).

国家自然科学基金项目(60372058;60772101)

王 悦(1988— ),女,硕士生,主研音视频编码算法AVS、嵌入式系统;

陈 涛(1987— ),硕士生,主研嵌入式系统研究;

张 刚(1953— ),教授,博士生导师,主研音视频编码算法AVS、SoC集成电路设计、应用系统快速开发方法。

责任编辑:魏雨博

2013-04-27