基于LVDS的高速图像数据存储器的设计与实现

2014-09-17张会新刘文怡

李 斌,张会新,刘文怡

(中北大学a.电子测试技术国家重点实验室;b.仪器科学与动态测试教育部重点实验室,山西太原 030051)

基于LVDS的高速图像数据存储器的设计与实现

李 斌a,b,张会新a,b,刘文怡a,b

(中北大学a.电子测试技术国家重点实验室;b.仪器科学与动态测试教育部重点实验室,山西太原 030051)

为实现高速图像数据的实时接收存储和有效转发,设计了一种基于Flash的高速大容量固态数据存储器。该存储器以LVDS作为数据传输接口来接收两路高速数字图像数据;用外部FIFO作为图像数据缓存以确保数据接收和存储的并行性;通过FPGA控制整个系统的运行。经实际应用,该系统可成功地完成图像数据的接收、存储和转发功能。

高速;实时存储;LVDS;Flash;FPGA

采集数据的有效传输和存储转发技术的发展保证了数字图像在现实中广泛应用。如今,从多媒体通信领域的远程教育、图像监视到医学上的远程会诊,都和数据的有效传输及存储转发技术息息相关。在国防工业领域,图像数据的采集存储和连续有效转发也起着巨大的作用,航空遥感图像和卫星遥感图像的处理加工,电视制导中数据视频图像的传输,都离不开图像传输存储技术[1]。本文设计的基于Flash的高速大容量固态数据存储器,采用了基于LVDS的数据传输方式传输两路高速图像数据,实现图像数据的高速实时存储。不仅具有处理速度快、设计灵活性高等特点,还具有可配置性和可重构性的特点。

1 系统总体设计

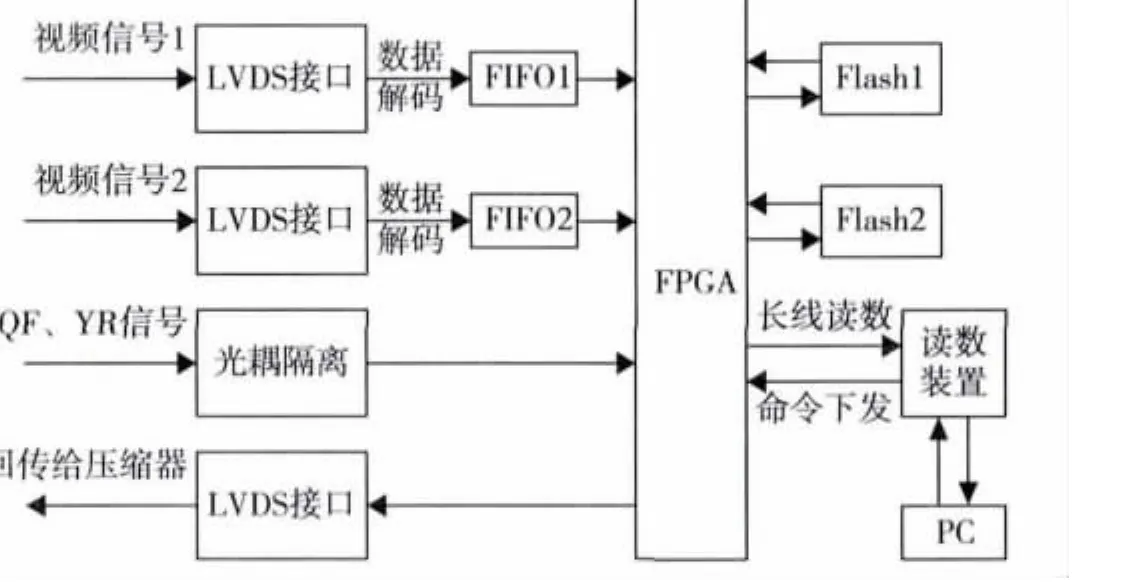

本文介绍的图像存储器在飞行任务中负责完成两路独立视频信号的采集存储任务。视频图像存储的总体结构框图如图1所示,当光耦接收到起飞和诱饵两个控制点火信号后,FPGA就控制视频信号1、视频信号2经2路独立的LVDS接口传输,并分别解码后缓存到2个外部FIFO中,最后写入到2个各自的存储模块Flash当中。在系统工作时,读书装置可以实时监测记录器关键状态参数;系统存储工作完成后,读数装置通过LVDS接口以20 Mbyte/s的速度远程高速读取图像记录器的数据,将数据回传至上位机进行存盘判读。

图1 存储器功能框图

本设计存储器负责接收的2路图像尺寸均为640×480 byte,在飞行器内部传感器下发起飞和诱饵两个关键信号的控制下,图像数据存储器分别对这2路视频图像信号进行采集,采样位数:8 byte/像素,输入数据码率:30.72 Mbyte/s,帧率:100 f/s(帧/秒),然后将解码后的数据分别存储到2个Flash中,最后准确地完成数据的转发任务,使图像数据顺利进入下一模块。存储器视频信号处理硬件电路框图如图2所示。

图2 存储器视频信号处理硬件电路框图

2 硬件电路设计

2.1 LVDS长线传输电路设计

本设计系统中摄像头发出的视频图像信号属于高速变化的信号[2],容易受到噪声影响。低压差分(Low Voltage Differential Signaling,LVDS)数据传输技术是一种新型的、具有很低的差分电压摆动幅度的信号传输方式。LVDS传输过程中以差分的方式传送数据,从而具有很低的串扰和噪声以及只消耗很少的功率[3]。此外它通过一对并行PCB走线或平衡电缆传输数据,可以达到100 Mbit/s甚至高于1 Gbit/s的高速率数据传输。解决了高速数据的有效传输,同时也将有助于降低系统设计复杂度,提高系统可靠性。基于LVDS技术的传输特点及应用优势,本设计中图像输入接口采用LVDS进行图像数据接收。设计中为满足信号实时高准确性的传输,在LVDS发送端采用串化器和驱动器相结合的方式增强信号;在LVDS接收端采用均衡器和解串器相结合的方式,来补偿信号长线传输过程中的损耗。这样高速图像信号可以稳定地传输上百米[4]。如图3为LVDS接口端硬件电路设计图。

图3 LVDS接口端硬件电路设计图

2.2 FIFO的电路设计

本设计中进入FIFO前经解码得到的图像数据传输速率为30.72 Mbit/s,因此在FIFO的选型中,必须选择一款读写速度快而且容量大的外部FIFO来缓存图像数据[5]。经过计算并对比分析后,本设计选用了CYPRESS公司生产的64 kbit×18 bit的CY7C4285V:

1)CY7C4285V拥有66.7 MHz的最大工作频率,10 ns的最小读写周期,完全可以稳定、可靠地接收码率为30.72 Mbit/s的图像数据,也满足25 ns读写周期的要求。

2)从FIFO接收图像数据的时序图中(如图4)可以看出,一个水平同步时间内,写入 FIFO的图像数据有640 byte,而读出 FIFO 的数据量为33 Mbyte/s×18.75 μs=618.75 byte。这样每一个水平同步时间内FIFO中就会剩余640 byte-618.75 byte=21.25 byte的图像数据。当垂直同步信号拉低时,FIFO中剩余的图像数据量达到最大,本设计FPGA控制FIFO半满即读,那么FIFO的容量至少应为:2×21.25×480=20 400 byte。显然容量为64 kbyte的CY7C4285V可以满足设计要求[6]。

3)操作简单。首先,单片64 kbyte CY7C4285V就可以满足设计要求,而不需串联多个FIFO,这样操作起来方便了很多。其次,该FIFO有读使能、写使能作为状态保障,且均采用边沿触发方式,使得时序控制简捷高效,便于FPGA的逻辑实现。

3 关键技术研究

3.1 高速写入方式

图4 单路图像数据接收接口时序定义图

本设计选用三星公司的K9WBG08U1M作为存储介质。该芯片容量大小为4 Gbyte,内部分为2片,每片2 Gbyte,可通过片选信号和切换两片存储空间,每片由8 192块组成,每块中有64页,每一页都可以存储4 kbyte的图像数据和128 byte的状态信息。本设计要完成对高速图像数据的存储任务,普通的Flash写入方式无法满足30.72 Mbyte/s数据存储速度的要求。因此,大幅提高Flash数据接口的写入速度,成为系统设计的关键。K9WBG08U1M内部平面结构图如图5所示,Flash内部的两片分别为chip1和chip2,4个平面Plane0~Plane3组成1个chip,原始的写入方式为依次写满Plane0、Plane1、Plane2、Plane3,为大幅度提高数据存储速度,系统采用交错双平面页编程(interleave two-plane page program)的操作方式[7],并行对chip1、chip2的8个平面进行操作,如图6所示Interleave two-plane编程时序图:从chip1的Plane0开始依次写入每一个平面第1块的第1页,即写入chip1的Plane0的block0的page0后,再横向连续写入7页,那么当循环回chip1的Plane0的block0的page1时,用时25 ns×4 096×7=716.8 μs大于页编程时间tPROG的最大值700 μs,从而可以不间断地继续对chip1的Plane0的block0的page1进行操作,这样充分利用了页编程的时间,使Flash的写入速度提高到40 Mbyte/s,完全可以完成对30.72 Mbyte/s图像数据的存储任务。

图5 K9WBG08U1M内部平面结构图

3.2 图像数据分析

图6 Interleave two-plane编程时序图(截图)

在飞行中该图像存储器需要在过载、噪声等恶劣环境下工作,由于这些干扰很可能丢失一帧或者若干帧数据,为此本文经分析接收图像时序,为图像数据编帧如图7。这样将图像数据设定成固定的帧格式,不仅可以稳定地循环采集,便于数据处理;而且即使由于干扰丢掉了一帧或若干帧,也不会影响帧结构的完整性,对于整体数据分析没有影响。这样就保证了后续存储转发数据的正确性。接收一帧图像数据的流程图如图8所示。

图7 图像存储数据帧结构

图8 接收一帧图像数据流程图

3.3 图像信息存储设计

如图9所示待存储数据的数据流结构,1带信息帧由1图像帧和时标及其他信息组成,存入Flash的为带信息帧,但后续转发给图像压缩单元的数据只能含有图像帧。为此本文将FIFO设计成9位缓存模式,低8位用来存储图像数据图像帧或时标及其他信息,最高位通过“1”或“0”来区分是图像数据还是帧标志。即将低8位是图像数据的最高位置高,低8位是时标及其他辅助信息的最高位置低,转发时只将最高位为1的数据流发送给图像压缩单元。

图9 待存储数据的数据流结构

一片K9WBG08U1M的Flash内部有1 048 576页,本文所接收的图像数据:1图像帧=307 200 byte,1页容量为4 kbyte,需用75页,所以1片Flash最多可存储13 981帧视频图像。接收图像帧频为100 f/s,25 s接收2 500帧视频图像,仅占Flash总容量的18%。采用上述interleave two-plane page program的页编程方式,每75页代表一帧视频图像数据,第76页用来写入每一帧的状态信息。写入的顺序如图10中箭头所示。

图10 存储区和图像帧之间的映射关系

图10显示每一行有8个block,共有512页,经计算每一行可以完整地存储6帧图像数据。当图像数据完整地写入75页,第76页也写入状态信息时,一帧视频图像信息就存储完毕了。然后Plane加1,继续将图像数据写满前75页,第76页写入时标及附加信息,依次往下写,当第6帧图像数据完全写入Flash后,直接将Flash的块地址加2,跳到下一行,按照上述操作方式,继续写入图像数据,其流程图如图11所示。

图11 图像存储一帧数据流程图

4 实验结果分析

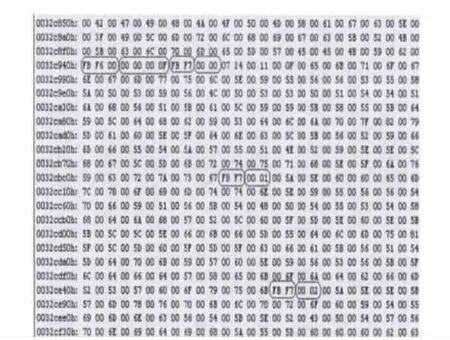

如图12为计算机终端显示的部分图像数据,把数据解密后用上位机还原图像如图13所示,显示的是视频图像中第2 194帧图像。测试结果显示,接收数据正确无误,还原图像清晰完整。

5 结论

本文所设计的数据存储器能够实现高速图像数据的实时存储及转发,码率可达40 Mbyte/s,具有高写入带宽和工作稳定、可靠的特点。本设计已在相关项目中得到应用,工作性能良好,具有一定的参考价值。

图12 部分图像数据(截图)

图13 视频图像还原后得到的第2 194帧图像(截图)

:

[1]吴萌.一种高速、大容量图像存储系统设计[D].西安:中国科学院西安光学精密机械研究所,2009.

[2]王小艳,张会新,杨永生.Camera Link协议和FPGA的数字图像信号源设计[J].国外电子元器件,2008(7):59-61.

[3]ZHANG Wendong,ZU Jing.The intelligent missile black-box[J].IEEE Trans.Instrumentation and Measurement,1995,44(3):824-826.

[4]彭晴晴,孟令军.基于NiosⅡ的PCI Express接口卡的设计[J].计算机测量与控制,2012(2):523-525.

[5]任伟,张彦军,白先民.基于LVDS的高速数据传输装置的设计[J].科学技术与工程,2012(29):663-665.

[6]孟令军,彭晴晴.阵列存储在遥测图像采集系统中的应用[J].电视技术,2011,35(8):65-67.

[7]郭铮,刘文怡,冯妮.基于FPGA多通道高速数据采集存储器设计[J].电视技术,2012,36(17):55-57.

Design and Implementation of High-speed Image Data Recorder Based on LVDS Interface

LI Bina,b,ZHANG Huixina,b,LIU Wenyia,b

(a.National Key Laboratory For Electronic Measurement Technology;b.Ministry of Education Key Laboratory of Instrumentation Science& Dynamic Measurement,North University of China,Taiyuan 030051)

In order to receiving the image data in real time and retransmitting it effectively,a high-speed large-capacity solid-state data recorder based on Flash is designed in this paper.Data LVDS interface is taken as data transmission to receive two high-speed digital image data.External FIFO is used as the image data buffer in order to ensure the parallelism of the received data and the stored data.FPGA is used to control the operation of the system as a whole.Through the practical application ,this system can achieve receiving,storing and retransmiting the image data.

high-speed;real-time storage;LVDS;Flash;FPGA

TN91

A

【本文献信息】李斌,张会新,刘文怡.基于LVDS的高速图像数据存储器的设计与实现[J].电视技术,2014,38(3).

国家自然科学基金项目(51275491)

李 斌(1988— ),硕士生,主研微纳传感与执行器件;

张会新(1980— ),讲师,主研动态测试技术及智能仪表;

刘文怡(1970— ),博士生导师,主研微系统集成技术、集成测量系统及仪器、无线传感网络。

责任编辑:魏雨博

2013-06-21