FPGA片间万兆可靠通信的设计与实现

2014-09-17袁文燕宋宇飞田进进张俊杰

袁文燕,郑 玥,宋宇飞,王 凯,田进进,张俊杰

(上海大学通信与信息工程学院,上海 200072)

FPGA片间万兆可靠通信的设计与实现

袁文燕,郑 玥,宋宇飞,王 凯,田进进,张俊杰

(上海大学通信与信息工程学院,上海 200072)

随着云计算技术的发展,采用FPGA作为协同加速成为其发展的一个趋势,如何设计与实现FPGA片间的高速通信是该研究方向的一个热点。研究了FPGA万兆通信的物理层、MAC层的实现机制,在通信协议可靠传输方面实现了MAC层的流控以及错误包检测功能。仿真以及实际平台测试表明,该通信协议能够实现FPGA片间万兆的线速通信。

云计算;FPGA;10 G MAC层;流控

云计算服务目前在互联网上急速增长,其通过互联网来提供动态易扩展的资源。随着云计算的发展,对以太网的数据通信以及高性能计算也提出了更高的要求[1],而基于大规模的FPGA协同加速成为云计算服务的一种发展趋势[2-3]。因此如何设计与实现多片FPGA之间的可靠通信成为云计算研究的一个热点。文献[4-5]对物理层和MAC层的接口进行了设计,实现了吞吐率达Gbit/s级的通信速率。文献[6-7]设计了千兆以太网全双工模式下的物理通信,包括Pause帧的收发,还实现了数据包的校验出错重传机制,但限于上层应用,对Pause帧的实现机制没有具体阐述。

文献[8-9]基于Xilinx公司FPGA平台,在分析如何实现万兆以太网的CRC32纠错以及接收控制策略、CRC编码/校验及与千兆以太网兼容等关键问题的基础上,实现了万兆以太网MAC层控制但缺乏具体的实现方案。文献[10]采用自定义的的10 G MAC,设计与实现了以太包的调度策略。

上述研究没有涉及万兆MAC层的流控以及可靠传输。基于此本文提出一种通过利用Xilinx FPGA集成的万兆MAC IP核以及XAUI IP核实现FPGA片间可靠通信的方法。

1 互联系统结构

本文提出的互联系统结构如图1所示,系统由4片Xilinx公司的Virtex6系列的FPGA xc6vlx550t-2ff1759构成。每2片FPGA之间都有4路高速双向传输通道,每路运行速度均为3.125 Gbit/s,对外都有1路10 G/20 G的QSFP光通信接口,线路采用8B/10B编码,因此FPGA之间的互联通信速率为10 Gbit/s。可以通过该硬件实现多级FPGA的级联通信。

图1 互联系统结构

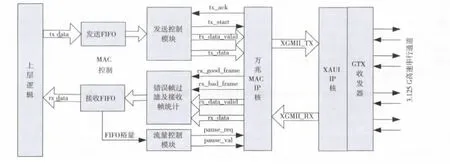

2 万兆互联的物理层以及MAC层接口的设计实现

为了支持FPGA之间的万兆通信,物理层采用Xilinx公司提供的XAUI IP,MAC层采用Xilinx公司的万兆以太MAC IP实现传输协议的CRC32校验码的填充与检测,如图2所示。在MAC层之上增加了MAC控制模块,该模块通过FIFO接口简化了应用层的设计,并采用流量控制以及错误检测功能实现数据的10 G线速可靠传输。

图2 高速互联接口结构图

XAUI IP核配合Xilinx的Rocket IO GTX实现XGMII总线与10 G物理通道的转换[11]。GTX收发器实现高速串行收发器的数据缓冲、通道绑定、接收端时钟恢复以及发送预加重等功能[12]。XAUI IP核的XGMII总线包括32位的双速率和64位的单速率接口,由于本文的XGMII总线在FPGA内部,因此采用单速率的XGMII总线接口,系统工作时钟频率为156.25 MHz。

2.1 万兆MAC 层协议

万兆MAC核是一个单速,全双工10 Gbit/s的以太网媒体控制器,实现IEEE802.3ae万兆以太网数据的前导码过滤与增加、数据4 byte CRC32校验码的填充与验证。支持的以太数据帧长最小为64 byte,最大为1 518 byte(可以支持Jumbo frame)。其内部结构包括发送、接收引擎,流量控制模块,管理接口和XGMII接口,通过XGMII接口能够很方便地连接到XAUI IP核[13]。

发送端在传输数据之前,MAC层会先发送7 byte的同步码和1 byte的帧首定界符,并在1帧传送结束时填充4 byte的CRC32校验码,如果数据长度小于46 byte,则会自动在数据字段填充PAD字符,即补0。在接收端,MAC层去掉前导码和帧首定界符,并对帧进行CRC32校验。如果校验正确则向上层发送收到正确帧(rx_good_frame)信号,否则发送收到错误帧(rx_bad_frame)信号。MAC层还具有流控的功能,实现收发双方的通信速率匹配。

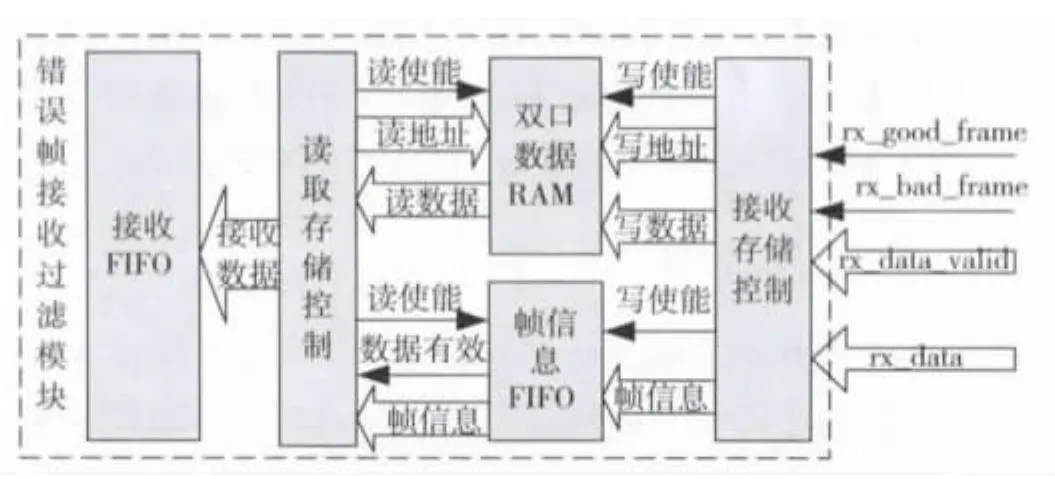

2.2 错误检测及过滤功能

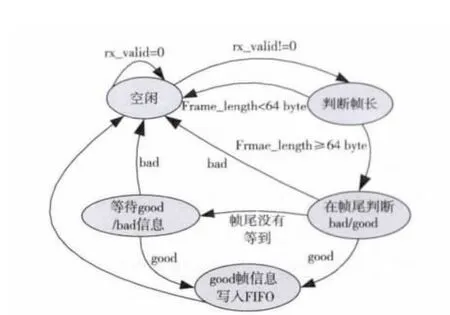

Xilinx提供的万兆MAC控制器对接收到的错误数据并不进行处理,仅仅给出数据CRC32校验是否正确。为了提供物理层的可靠传输,需要在此基础上增加接收错误帧过滤模块,如果接收到的是校验错误帧,则需过滤掉该帧。本文采用基于双端口数据RAM以及帧信息FIFO的存储机制实现错误包的过滤,如图3所示。接收存储控制模块若检测到万兆MAC IP接收端口收到的数据rx_valid(rx_data_valid_o!=8’h0)有效,则把该数据缓存到双口数据RAM中去。然后检测rx_valid是否小于8个时钟节拍,如果小于8个时钟节拍,则不用判断rx_good_frame以及rx_bad_frame,因为此时接收到的帧肯定错误(小于万兆以太协议的最小64 byte),回到IDLE状态。如果rx_valid持续有效时钟大于8个时钟节拍,则在帧尾检测是否有rx_good_frame或者rx_bad_frame;如果是bad帧,不作处理回到IDLE状态,如果是good帧,则将该帧存放RAM的起始地址和帧长信息写入帧信息FIFO,并返回IDLE状态。如果在帧尾没有检测到good或者bad信息,则等待;若等到good信息则把该帧长以及起始地址写入帧信息FIFO,并返回IDLE状态,若等到bad信息则直接回到IDLE状态,其状态机如图4所示。

图3 接收错误帧过滤图

图4 过滤模块状态机

读取控制模块若检测到帧信息FIFO有数据,则表示双口数据RAM中已经存储了正确的以太帧,从帧信息FIFO中获取接收到帧的地址与长度,并把接收到的数据存储到用户控制端口的接收FIFO中。由于采用存储校验机制,因此接收端相对发送端有一定的延迟,最大延迟为最长以太帧的存储时间。

2.3 流量控制模块以及接收FIFO缓冲区深度设计

图5 Pause帧传输链路延时

为了解决发送FPGA与接收FPGA通信速率的不匹配,需要在MAC层增加流控功能,即当接收FIFO裕量小于预设的安全值,向发送方发送暂停(Pause)帧,告知发送方停止发送数据一段时间。发送方接收到暂停帧以后,停止数据的发送,若暂停期间没有接收到新的Pause帧,则继续本次数据通信,若暂停期间接收到新的暂停帧,则从当前时刻增加新的暂停时间。Xilinx的万兆MAC提供了流控功能,如图2所示。当万兆MAC IP核检测到暂停请求(Pause_req)为1时,等待当前发送的以太帧传输完毕,然后把暂停时间Pause_val(16位宽)值封装成标准IEEE802.3av Pause帧,并通过XAUI IP核把Pause帧发送出去。暂停时间为Pause_val×51.2 ns,最长为3.35 ms。根据本文的实现方案,从 Pause帧发出到接收方收到该帧并对其响应,需要经历多级链路延时,如图5所示。其中当前帧发送等待时间表示当系统产生Pause_req时,如果万兆MAC当前正在发送以太帧,则需要等待该帧发送完毕的时间,因此Tsnd_current_delay等于最大以太帧长传输的时间也即 1.2 μs。Tsnd_create_pau,Tsnd_xaui,Trcv_xaui与万兆MAC IP以及XAUI IP核的特性相关,其中Tsnd_create_pau表示从万兆MAC接收到Pause_req有效到把Pause帧传输到XAUI IP核的延迟时间,Tsnd_xaui与Trcv_xaui表示从XGMII总线到高速串行链路之间的延时,Trcv_pau表示万兆MAC接收到Pause帧到内部逻辑处理该帧的时间。Tsnd_create_pau,Tsnd_xaui与Trcv_xaui以及Trcv_pau通过万兆MAC以及XAUI IP的仿真即可得到。图6是万兆以太网点对点的Modelsim仿真,从该图可以看出Tsnd_create_pau的延时为19 个时钟节拍,即0.12 μs,Tsnd_xaui与Trcv_xaui延时为27个时钟也即0.17 μs,Trcv_pau的延时为14个时钟节拍也即0.09 μs。接收响应延时Trcv_paus_res为当万兆MAC IP核接收到Pause帧以后,需要等待当前以太帧发送完毕的延时,因此Trcv_paus_res为以太帧最长帧传输的时间即1.2 μs。

图6 Pause帧从发送到接收延迟仿真(截图)

因此Pause帧从发送到接收响应的Tpause_response延时为通道延时Tchannel+2.8 μs。在本文的硬件平台中,FPGA之间的物理通道为直接连接,因此Tchannel为0。在Tpause_response期间,数据发送端仍有可能在10 G线速发送数据,因此若要保证接收FIFO缓冲区不溢出,接收FIFO必须在裕量大于Tpause_response×8/6.4=3 500 byte的时候发送Pause帧。故接收缓冲区FIFO的深度必须大于512(宽度为8 byte)。

3 系统性能测试

图7 流量控制测试(截图)

在Xilinx公司的ISE开发环境中进行代码综合、映射及布局布线,综合结果测试表明,本设计的工作频率可以达到156.25 MHz。通过快写慢读操作来验证流控模块,如图7所示。最终实验结果表明能正常过滤错误以太包,并确保通信速率达到了10 Gbit/s。用复位来模拟掉电操作,最终测试结果表明该系统在正常传输过程中若发送端或接收端突然掉电,上电后双方仍能重新正常通信。

4 结论

本文实现了万兆MAC层发送、接收、流控以及错误帧过滤的设计。并且使用Xilinx的Virtex-6系列FPGA器件进行布局布线后进行板级测试验证。结果表明,系统可以在156.25 MHz时钟频率正常工作,接收和发送带宽均可接近10 Gbit/s。但随着社会的发展,人们对通信速率的要求越来越高,在不久的将来,10 Gbit/s的通信速率将不能满足人们的需求,所以对高速互联的研究将永无止境,下一步可以提高互联通信速率,进一步研究20 Gbit/s、40 Gbit/s或更高速率的互联结构。

:

[1]王文彬,肖玉杰,龙明.基于云移动技术的应急视频指挥系统[J].电视技术,2013,37(1):161-164.

[2]YU J B,ZHU Y X,XIA L,et al.Grounding high efficiency cloud computing architecture:HW-SW co-design and implementation of a standalone web server on FPGA[C]//Proc.Applications of Digital Information and Web Technologies(ICADIWT).[S.l.]:IEEE Press,2011:124-129.

[3]NIVEDITA N,DAKHOLE P K,ZODE P P.Embedded web server on Nios II embedded FPGA platform[C]//Proc.Second International Conference on Emerging Trends in Engineering and Technology.[S.l.]:IEEE Press,2009:372-377.

[4]ZHANG Q ,KANG G X.MAC-PHY interface design and implementation based on PLB for Gbps transmission system[C]//Proc.The 8th Annual IEEE Consumer Communications and Networking Conference-Wireless Consumer Communication and Networking,Conference Publication.[S.l.]:IEEE Press,2011:674-678.

[5]WANG Guixin,KANG Guixia,WANG Hao.Design and FPGA implementation of MAC-PHY interface based on PCI express for next-generation WLANs[C]//Proc.8th International Conference on Wireless Communications,Networking and Mobile Computing(WiCOM).[S.l.]:IEEE Press,2012:1-4.

[6]丁世勇,谭文文,李桂英.基于FPGA的以太网MAC控制器的设计与实现[J].电子设计工程,2011,19(21):163-165.

[7]张克功,李和平,高鑫.基于千兆以太网的雷达数据可靠传输系统设计[J].自动化与仪表,2012(6):26-31.

[8]曹政,李磊,陈明宇.万兆以太网MAC层控制器设计与实现[J].小型微型计算机系统,2007,28(6):974-978.

[9]张友亮,刘志军,马成海,等.万兆以太网MAC层控制器的FPGA设计与实现[J].计算机工程与应用,2012,48(6):77-79.

[10]ARENAS R A,FINOCHIETTO J M,ROCHA L M.Design and implementation of packet switching capabilities on 10GbE MAC core[C]//Proc.Programmable Logic Conference(SPL).[S.l.]:IEEE Press,2010:141-146.

[11]马腾飞,吴志勇,李增.基于XAUI协议的10Gb/s光纤通信系统[J].计算机工程,2010,36(17):264-265.

[12]LogicCORE IP 10-Gigabit Ethernet MAC v10.2 User Guide[EB/OL].[2013-05-10].http://www.xilinx.com.

[13]韩盛杰,张俊杰,林如俭.10G EPON的ONU硬件设计与实现[J].光通信技术,2009(5):5-7.

Design and Implementation of 10-Gbit/s Reliable Intra-FPGA Communication

YUAN Wenyan,ZHENG Yue ,SONG Yufei,WANG Kai,TIAN Jinjin,ZHANG Junjie

(School of Communication and Information Engineering,Shanghai University,Shanghai 200072)

FPGA have already been successfully employed since the rapid growth of cloud computing,so that many researches focus on the reliable intra-FPGA communication .This paper adopts the bad frame filter technique and flow control technique to realize the reliable multi-FPGA communication after introducing the PHY and MAC layer design of 10 G Ethernet.The simulation and experimental results show that communication speed can reach 10 Gbit/s.

cloud computing;FPGA;10 G MAC;flow control

TN919.3

A

【本文献信息】袁文燕,郑玥,宋宇飞,等.FPGA片间万兆可靠通信的设计与实现[J].电视技术,2014,38(1).

国家高技术研究发展计划863项目(2009AA012201)

袁文燕(1981— ),女,硕士,教师,主研数据高速传输。

责任编辑:魏雨博

2013-05-11