基于滚动输出模式的高速雷达视频显示处理方法

2014-09-08邢永昌朱向云薛宜童

邢永昌,朱向云,薛宜童

(中国船舶重工集团公司第七二四研究所,南京211153)

基于滚动输出模式的高速雷达视频显示处理方法

邢永昌,朱向云,薛宜童

(中国船舶重工集团公司第七二四研究所,南京211153)

随着雷达重频和显示器显示分辨率的提高,当前VRAM的速度已经不能满足雷达视频的实时刷新要求。针对该问题,本文提出一种采用滚动输出模式的视频输出处理方法。通过实验验证,该方法在保证高数据率和高分辨率的前提下实现了雷达视频画面流畅刷新。

雷达重频;VRAM;FIFO存储器;SRAM

0 引 言

随着雷达重频的提高和高分辨率显示器普及应用,对雷达视频显示处理速度提出了更高的要求,尤其是高速雷达视频的存取方面。在雷达重频小于2 kHz、显示分辨率小于1000×1000时可以采用VRAM(视频处理RAM)完成雷达视频的处理[1],但当雷达重频超过2 kHz甚至达到10 kHz以上时VRAM的存取速度就无法满足需求。

最新的一篇相关论文[2]中提出采用视频分割及写FIFO缓存控制模块实现降低输出频率的方法。该方法是通过分割视频方式和双FIFO方法降低电视视频数据输出的频率,分割后每个显示区域均需要一个显示器显示。如果雷达重频提高或单个显示器显示分辨率提高,则雷达视频画面会出现断行现象。本文通过每个视口采用两个FIFO,针对不同显示的需要在显示区域内任意位置开辟任意大小(不大于1200×1200)的多个视口,最终把多个视口的雷达视频对接融合并与二次视频叠加,通过一个显示器或两个显示器输出。

本文提出以SRAM和FIFO存储器为硬件平台,采用滚动输出模式的高速雷达视频显示处理方法,实现高数据率、大分辨率雷达视频稳定显示效果。该技术使高重频率雷达的大分辨率流畅显示成为现实。

1 基本原理

由于SRAM与视频输出流的FIFO处于不同的时序,且显示器需要以行为单位定时输入视频数据[2],而SRAM中的视频数据是由FPGA实时处理的结果,需要按照本模块的处理时钟确定读取时间片[3]。高重频雷达高分辨率显示雷达视频时,在SRAM中可用于数据输出的时间片很少,且数据率高,无法与显示器的行输出速率同步。如果采用现有的技术,会出现雷达视频断行显示,不能实现视频画面流畅显示。为了保证既能满足以根据FPGA处理周期控制SRAM的读写周期,又能满足显示器以行扫描频率为节奏的串行数据输入的要求,本文采用滚动输出法处理雷达视频。该方法不仅能满足雷达视频画面的流畅、清晰,而且可以保证画面变化的实时显示。

实现本技术的原理为:针对每个雷达视频显示窗口设计两个FIFO存储器,每个存储器容量至少可以存储1行视频数据的容量;输入时按照重频脉冲和扫描转换处理的时序选择空闲时间片,把雷达视频以字段为单位从SRAM中读出,滚动输入到两个FIFO存储器中;输出时按照行扫速率从两个FIFO存储器中读出(如果同一行视频与多个雷达视频显示窗口相关,需要读取多对FIFO存储器并按行对接),然后与二次视频叠加,最后以行为单位串行输出到显示器。

2 实现方法

下面通过VRAM直接输出法和滚动输出法比较解释本文算法。

2.1 VRAM直接输出法

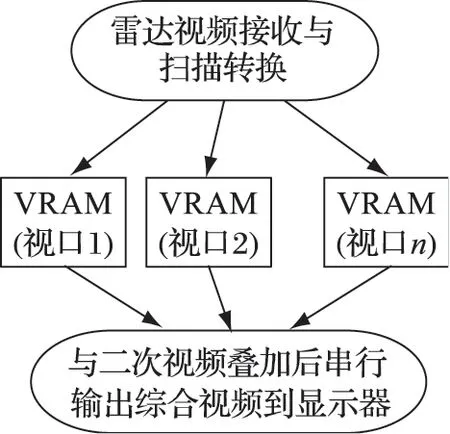

当前的雷达视频输出方法是采用VRAM而不是SRAM作为雷达视频处理存储器。雷达视频处理完成后由VRAM自带的雷达输出功能按照行扫描速率输出雷达视频。采用VRAM的雷达视频显示区刷新工作原理图如图1所示。

图1 基于VRAM的雷达视频显示区刷新工作原理图

由于该方法是通过雷达视频处理与行视频输出同步的方法直接输出,所以采用这种方法雷达视频处理的速度受显示器数据输入率的限制,当雷达重频大于2 kHz时雷达视频的输入与输出就无法同步,会出现断行显示现象。

2.2 滚动输出算法的实现

本文通过采用滚动输出的方法实现雷达视频的输出。在雷达视频读取频率和时刻与向显示器输入视频数据频率不一致的情况下,该方法可以保证雷达视频的流畅实时显示。在其实现步骤中,写入FIFO存储器是根据雷达的重频脉冲、扫描转换和多通道雷达视频叠加处理的时序,选择空余时间片从SRAM中读取雷达视频数据并滚动输出到对应的FIFO存储器中。SRAM中处理后的雷达视频数据是针对不同的雷达视频显示窗口(PPI显示、AR显示和B显且,每种显示都可以有多个窗口)分别存储于不同的存储空间,通过每个雷达视频窗口设计一对FIFO存储器实现数据的流畅输出[4]。

从FIFO存储器串行输出视频数据是按照行扫描速率输出。根据每个雷达视频窗口的屏幕坐标,从相关雷达视频窗口的FIFO存储器中读取雷达视频数据组合成一个雷达视频行,然后把该行视频数据与二次视频对应的视频数据叠加后输出到显示器。由于根据雷达视频窗口坐标寻找FIFO存储器任务和一次视频与二次视频叠加处理任务占用的时间资源少且稳定,故按照行扫描速率读取FIFO存储器后与二次视频叠加输出可以保证雷达视频的流畅显示。

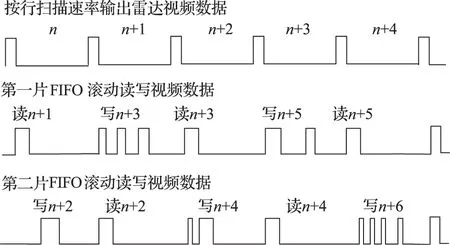

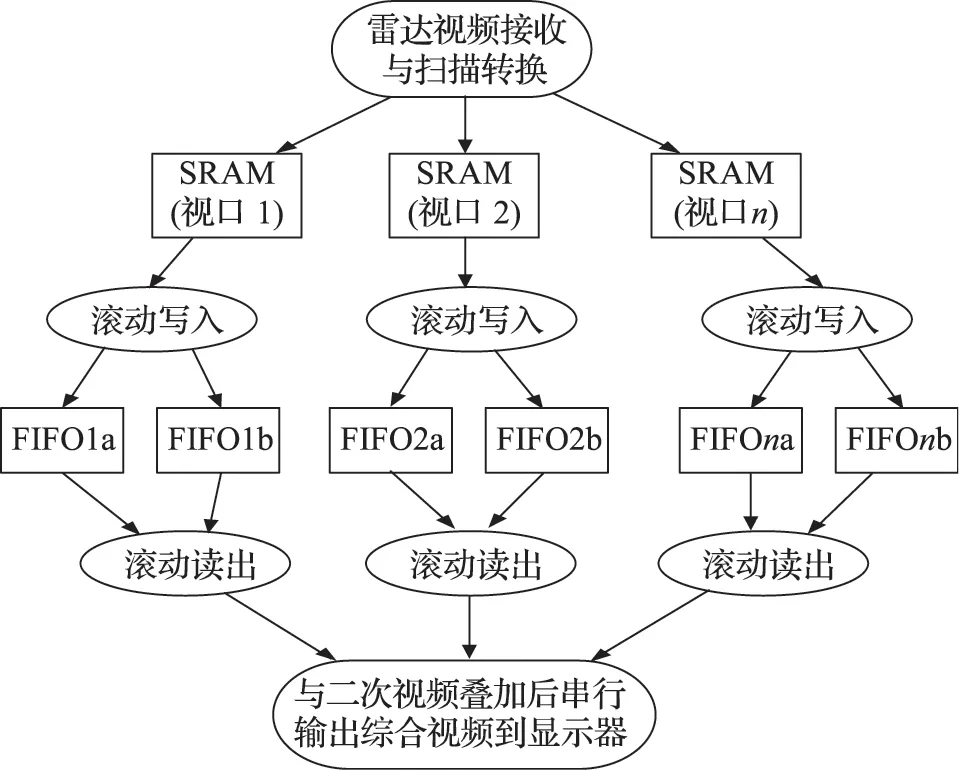

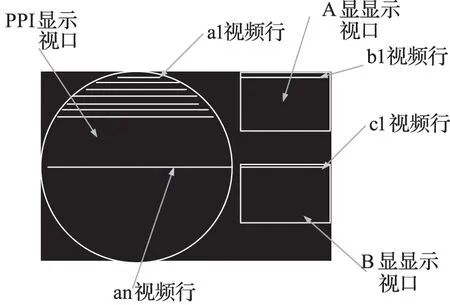

FIFO存储器输入输出时序示意图如图2所示。滚动输出法工作原理图如图3所示,图中“滚动输入”是以重频和视频处理时序滚动写入对应的FIFO,“滚动输出”是以显示器行扫描速率滚动读出雷达视频数据,组成以显示器扫描行为单位的雷达视频行。雷达视口视频行在显示器中显示位置示意图如图4所示。

图2 FIFO存储器输入输出时序示意图

图3 滚动输出法工作原理图

图4 雷达视口视频行在显示器中显示位置示意图(一个显示器)

3 试验结果与分析

3.1 试验环境与结果

该技术已经在某型装备的显控分机中实现。试验环境为:雷达重频为15 kHz;2个PPI显示区,分辨率均为1200×1200;2个A显显示区,分辨率均为390×380;4个B显显示区,分辨率均为390×380。由4个通道的雷达视频组成原始的雷达视频数据;叠加方式分别采用1个通道、2个通道、3个通道和4个通道叠加显示。

通过试验验证,该方法可以实现高重频、多通道、双屏和高分辨率雷达视频与二次视频稳定叠加显示,显示画面清晰流畅。经过长时间拷机验证系统运行稳定可靠。

3.2 试验分析

从现象上看,采用VRAM直接输出法时,雷达重频提高或雷达显示分辨率提高均会引起雷达视频断行,且不能实时更新画面。其原因是雷达视频需要处理的任务增加,引起VRAM没有足够的时间实现雷达视频的输出。

采用滚动输出法后,针对每个雷达视频显示窗口设计两个FIFO存储器;按照重频脉冲和扫描转换处理的时序选择空闲时间片,把雷达视频以字段为单位从SRAM中读出,滚动输出到两个FIFO存储器;然后按照行扫速率从两个FIFO存储器中读出(如果同一行视频与多个雷达视频显示窗口相关需要读取多对FIFO存储器,并按行对接),然后与二次视频叠加,最后以行为单位串行输出到显示器显示。这样不仅能保证FPGA处理芯片根据雷达重频等特征的实时处理视频和输出视频,而且可以保证显示器以行扫描频率为节奏的串行数据输入数据的要求,从而实现了雷达视频与二次视频叠加后流畅清晰显示的效果。

4 结束语

采用滚动输出模式的高速雷达视频显示处理方法可以实现高重频雷达视频的流畅显示与实时刷新。它不仅可以按照FPGA处理周期控制SRAM的读写周期流畅读出处理后的雷达视频数据,而且可以满足以行为单位、以行扫描频率为节奏的显示器串行输入数据的要求。该方法具有实时性好、成本低廉、效果明显的特点,它的提出及其工程实现在雷达、声纳视频显示技术方面具有很高的推广应用价值。

[1] Merrill I.Skolnik Levoy.雷达手册[M].3版.南京电子技术研究所译,2010.7:192-202.

[2] 霍伟.基于FPGA的高清视频分割技术的研究[D].南京大学,2012.5:32-33.

[3] 李秩博.基于FPGA视频图像处理的研究[D].电子科技大学,2010.4.

[4] 丁璐飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2002.6.

A high-speed radar video display and processing method based on rolling output mode

XING Yong-chang, ZHU Xiang-yun,XUE Yi-tong

(No.724 Research Institute of CSIC, Nanjing 211153)

With the improvement of radar repetition frequency and the display resolution, the speed of the current VRAM cannot satisfy the requirements of the real-time refresh of radar videos. A video output processing method based on the rolling output mode is proposed to solve such problem. It is verified through the test that under the premise of high data rate and high resolution, radar video images can be refreshed smoothly via this method.

radar repetition frequency; VRAM. FIFO memory; SRAM

2014-0609;

2014-07-03

邢永昌(1977-),男,高级工程师,硕士,研究方向:显控与数据融合;朱向云(1980-),女,工程师,研究方向:雷达显控;薛宜童(1979-),男,工程师,研究方向:大气与海洋类雷达系统。。

TN957.52

A

1009-0401(2014)04-0066-03