SCCB总线配置的FPGA视频采集与显示系统设计

2014-09-06高强王炜刘建郭毓敏

高强,王炜,刘建,郭毓敏

(天津工业大学 电气工程与自动化学院,天津 300387)

SCCB总线配置的FPGA视频采集与显示系统设计

高强,王炜,刘建,郭毓敏

(天津工业大学 电气工程与自动化学院,天津 300387)

提出了一种采用Altera公司的EP2C5Q208CN作为主控芯片,OV7670模块作为视频源输入并以SDRAM作为数据缓存的方案。通过对SCCB总线配置、图像数据采集、图像数据预处理、VGA显示等模块设计,完成了视频数据的采集与图像的输出显示。经过相关测试,本设计具有成本低、实时性强、可靠高好等优点。

FPGA;OV7670;视频采集;VGA

引 言

视频数据采集为图像采集与显示系统提供原始的数字图像数据,是信息处理、视频监控等系统的前端基础,也直接影响后端图像处理系统的性能[1]。随着近些年计算机及通信技术的发展,人们对视频采集系统的性能要求也越来越高。视频数据流数据量大和实时性要求高的特点直接影响到图像的采集与数据的处理速度。FPGA作为当今主流的大规模可编程集成电路,采用硬件逻辑实现数据处理和运算,具有集成度高、速度快、性能稳定、开发周期短、便于改进升级等一系列优点,还能实现视频采集、图像显示的外围逻辑控制,在视频采集和图像处理方面具有独特优势。

视频数据信息来源于图像传感器,目前被广泛采用的是CMOS传感器与CCD传感器。与CCD传感器相比,CMOS图像传感器可以把驱动与控制系统、ADC转换电路和信号处理等电路集成在一块芯片上,因此内部集成度高,外围电路简单,且在制造成本与功耗上具有优势。所以CMOS图像传感器在消费电子、汽车电子、工业控制、图像处理等领域得到越来越广泛的应用[2]。因此,本设计选用Altera公司的Cyclone II系列的EP2C5Q作为主控芯片,针对CMOS图像传感器,对输出的视频图像进行采集、处理及VGA显示。

1 硬件电路设计

本设计采用美国Omni Vision(简称OV)公司的OV7670图像传感器作为视频源,通过Altera公司Cyclone II系列的FPGA对其进行功能配置,并将传感器输出的格式为YCbCr(4:2:2)的图像数据进行采集,并完成YCbCr格式到RGB格式的转换,期间使用SDRAM作为数据缓存器,最终将FPGA输出的图像数据经过高速数模转换器ADV7123转换为模拟RGB信号输入到VGA显示器进行显示。其系统总体结构框图如图1所示。

图1 系统结构框图

2 图像采集及处理

系统上电之后,FPGA通过SCCB总线,对OV7670的201个可控寄存器进行配置,使OV7670输出格式为YCbCr(4:2:2)且有效像素为640(水平方向)×480(垂直方向)的图像数据,经过CMOS_CAPTURE模块对图像数据进行采集后写入SDRAM进行缓存,之后进行YCbCr(4:2:2)—YCbCr(4∶4∶4)—RGB(8∶8∶8)—RGB(5∶6∶5)图像数据格式的变换,完成图像数据的采集与处理。

2.1 OV7670初始化控制

美国OV生产的OV7670图像传感器,工作电压低、体积小,可提供单片VGA摄像头和影像处理器的所有功能,适用于玩具、多媒体电脑、数字照相机等领域。其具有标准SCCB(Serial Camera Control Bus)接口,兼容I2C总线接口,可以输出Raw RGB、RGB (GRB 4∶2∶2、RGB 5∶6∶5/5∶5∶5/4∶4∶4)、YUV(4∶2∶2)、YCbCr(4∶2∶2)等数据格式,并支持VGA、CIF和从CIF缩放到40×30的各种尺寸的8位影像数据。输出VGA图像可高达30 s,为逐行扫描方式,感光阵列共有656×488个像素,其中有效像素为640×480个。其具有曝光控制、伽马曲线、白平衡、增益控制、饱和度、色度调整等图像处理功能,可通过SCCB接口进行编程,按用户指定的参数进行配置。部分寄存器配置表如表1所列。

表 1 部分寄存器配置表

对OV7670的初始化过程,其实就是对OV7670中的201个可控寄存器进行数据写入的过程,即通过寄存器配置,设置OV7670输出图像的分辨率、帧频以及数据格式等,使OV7670输出自己想要的图像数据。整个过程需要通过SCCB总线协议完成。SCCB(Serial Camera Control Bus)是OV公司开发的一种双向三线的同步串行总线,其中当SCCB_E信号无效时,即只使用SIO_C、SIO_D时,变为两线制串行总线,兼容I2C总线时序,因此可用FPGA作为Master Device来模拟I2C总线时序,来完成对OV7670(Slave Device)的数据写入。其过程如下:先写入设备地址(ID-Address),参考Datasheet得知,OV7670地址为0x42,然后再写入要配置的寄存器地址(Sub-address),最后写入配置数据(Write Data),一次写入过程共传输24位数据,分为3个阶段完成,每一阶段传送完8位数据后,紧跟着由Slave Device产生Don’t-Care位,此时可由FPGA通过读取SIO_D得知其逻辑状态,该状态仅用于表明数据传输完成,并不能判断数据传输过程的错误。如此循环,按用户需求配置完所有的寄存器,即完成了OV7670的初始化[3]。本设计选择输出YUV(4∶2∶2)格式,且输出顺序为UYVY,分辨率为640×480,30 fps,一些较为重要的寄存器配置如表1所列。

2.2 图像数据采集

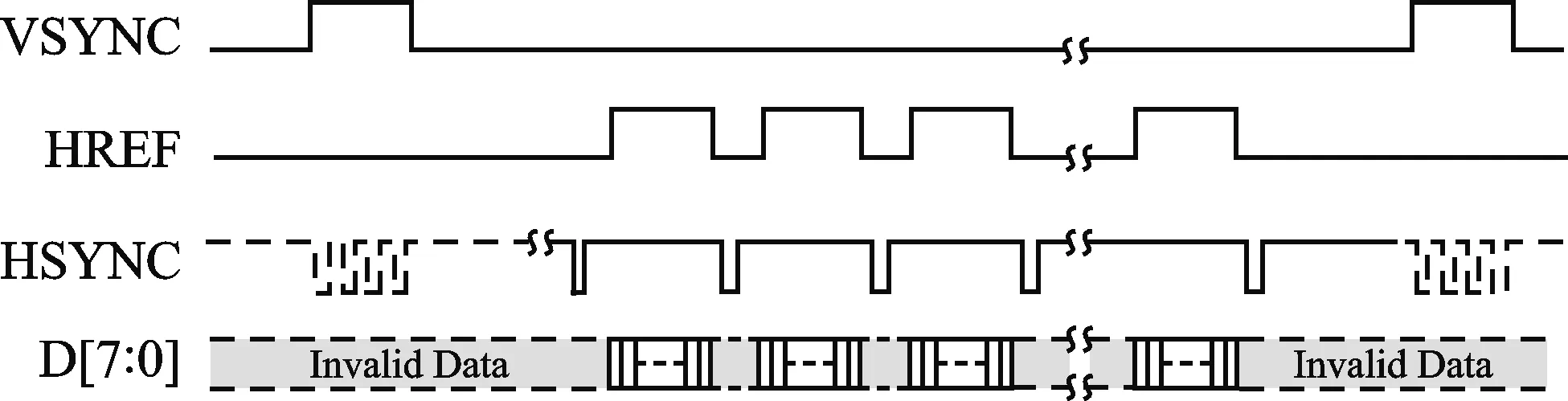

要正确采集到OV7670输出的图像数据,需要考虑行同步信号(HREF)、场同步信号(VSYNC)以及像素同步时钟信号(PCLK)。VGA帧时序图如图2所示。场同步信号低电平期间图像数据有效,行同步信号高电平期间有效,且维持640个像素时钟,每一个像素时钟数据总线输出8位数据,在场同步信号有效期间,行同步信号出现480次高电平,表明输出一帧分辨率为640×480的图像。

图2 VGA帧时序图

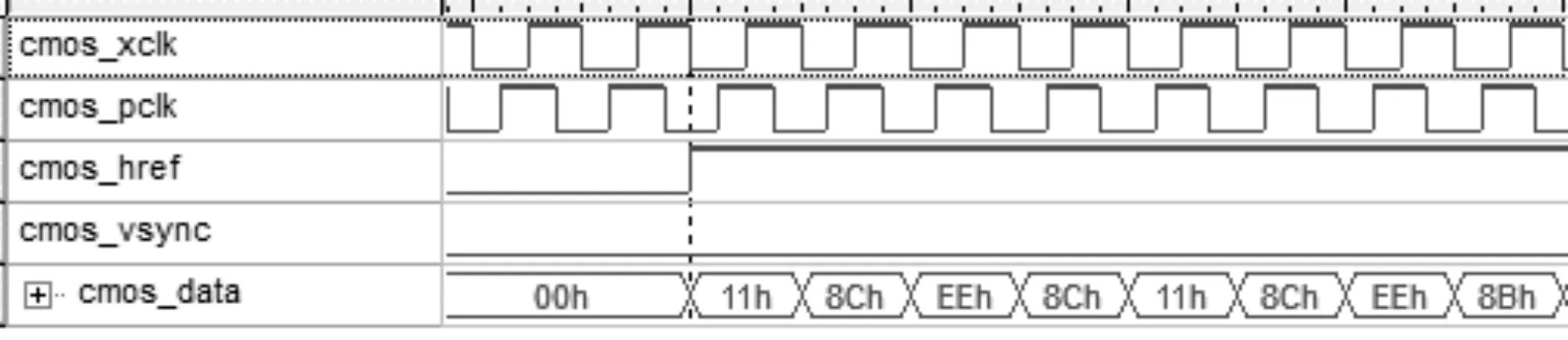

其中考虑到为了方便数据在SDRAM中的传输及缓存,本设计将先后输出的两个8位数据合并成一个16位数据进行采集。采用嵌入式逻辑分析仪Signal Tap II采集到的OV7670输出信号如图3所示。

图3 SingalTap II 采集信号

从图3中可知,在像素同步时钟上升沿到达之前,图像数据已达到稳定,因此选用像素同步时钟对其采集。另外从HREF上升沿开始,数据0x11、0xEE间隔出现是因为本设计在调试过程中,为了验证输出数据UV的顺序,配置寄存器时固定了UV数据的输出值,分别向地址67h(固定U)、68h(固定V)写入11h、EEh,数据按UYVY顺序正确输出。

2.3 图像数据缓存[4]

目前市面上常用的两种存储器分别为SRAM和SDRAM。相比于SRAM,SDRAM具有容量大、面积小、功耗小、成本低等优点。因此本设计选择SDRAM为数据提供缓存空间。由于前端输出的是30 fps、分辨率为640×480的图像,且并未对像素同步时钟PCLK分频,因为使用的典型时钟为25 MHz,为使缓存速度更快,图像能够实时传输,SDRAM选用读写时钟为125 MHz,VGA的像素也为25MHz,因此需要在图像采集模块与SDRAM、SDRAM与VGA显示模块之间用FIFO来完成异步时钟域的数据传输。

通过FPGA自带的IP核,产生两个存储宽度为16位、深度为512的FIFO,分别命名WRFIFO与RDFIFO。用图像采集过程中生成的数据输出标志位作为WRFIFO的写入使能,用rdusedw来控制SDRAM的写入请求信号,当WRFIFO中可读取数据达到256个,就申请将数据写入SDRAM。同样,在RDFIFO中,用wrusedw来控制SDRAM的读请求信号,当RDFIFO中写入个数少于256个时,就申请读SDRAM,之后将数据从SDRAM中写入RDFIFO中。在读取端,由VGA的像素时钟控制作为读取时钟,时钟扫描坐标xpos作为读取使能信号,控制数据在VGA行场可视区内输出,并最终在VGA上显示。

2.4 图像数据预处理[5]

YUV由Y(亮度)、U(色彩)、V(饱和度)复合而成,有诸如4∶4∶4、4∶2∶2、4∶2∶0等格式。本设计中摄像头中输出的为YUV(4∶2∶2)格式,即水平方向上UV的采样速度为Y的一半,相当于每两个点采集一个U、V,每一个点采样一个Y,通过牺牲色度的采样率达到图像数据压缩的目的。YCbCr是在YUV基础上经过发展产生的应用于数字视频的一种格式,基本可以等同YUV。

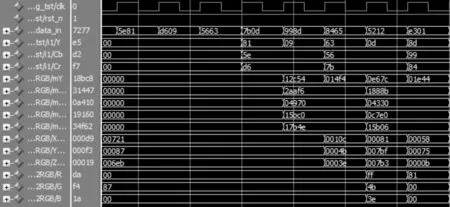

首先要将YCbCr(4∶2∶2)格式的数据转换为YCbCr(4∶4∶4),即在每一个时钟采样到的像素点数据同时包含Y、Cb、Cr三个分量信号,此处通过寄存器几级打拍之后,同步输出即可完成。之后为了使图像数据能够正常在VGA显示,需要将YCbCr(4∶4∶4)格式转换为RGB(8∶8∶8)。常用的转换公式如下:

R=1.164Y+1.596Cr-222.912

G=1.164Y-0.391Cb-0.813Cr+135.488

B=1.164Y+2.018Cb-276.928

考虑到FPGA进行浮点数运算较为繁琐,因此将以上公式进行移位放大处理,之后便可通过公式计算出RGB的对应值。但为了使图像最大限度地实时显示,本设计针对以上公式采用移位变换后,对数据处理采用三级流水线设计,最后截断正负溢出的部分,使数据保持在0~255内。最后通过简单的对应信号高位截取,完成RGB(8∶8∶8)到RGB(5∶6∶5)的变换。图4为Modelsim仿真图。

图4 YCbCr(4∶2∶2) to RGB(8∶8∶8)仿真图

3 VGA显示

根据VGA的工业时序标准设计VGA显示模块,产生VGA显示所用控制信号:行同步、场同步、行坐标、列坐标等[6]。在VGA显示数据有效期内,通过图像坐标控制图像数据从RDFIFO中读出,然后将数据及部分控制信号输入ADV7123对应的端口,即可实现图像的VGA显示。整个采集系统的采集实景图如图5所示。

图5 显示效果

结 语

FPGA Video Acquisition and Display System Based on SCCB Bus Configuration

Gao Qiang,Wang Wei,Liu Jian, Guo Yumin

(Institute of Electrical Engineering and Automation,Tianjin Polytechnic University, Tianjin 300387,China)

The paper proposes a solution which choose the Altera's EP2C5Q208C8 as the master chip,OV7670 module as a source of video input and the SDRAM as data buffer.Based on the design of the SCCB bus configuration,image data acquisition,image data pretreatment and VGA display module,it achieves video data acquisition and image output display.Through the relevant tests,the design has the advantages of low cost, good real-time performance and high reliability.

FPGA;OV7670;video acquisition;VGA

TP302.1

A