基于Nios II的SPI接口实现

2014-08-30康宾孙亮周玉娟

康宾孙亮周玉娟

(1中国电子科技集团公司第五十四研究所河北石家庄050081)

(2解放军理工大学江苏南京210007)

1 引言

SPI作为一个通用的接口在越来越多的芯片上使用,是一种4线的低速接口;AD9517-1ABCPZ就是一款支持SPI接口的时钟芯片,SPI接口是该芯片的配置接口。Nios II处理器作为一个简单的CPU,在很多SOPC系统中都被使用;在FPGA设计中搭建Nios II系统,结合SPIMASTER模块,可以用于配置AD9517-1ABCPZ,让其输出所需频率的时钟。

2 简介

2.1 Nios

Nios II系列软核处理器是Altera公司的第二代FPGA嵌入式处理器,其性能超过200DMIPS。Nios II包括3种产品,分别是:NiosⅡ/f(快速)最高的系统性能、中等FPGA使用量;NiosⅡ/s(标准)高性能和低FPGA使用量;NiosⅡ/e(经济)低性能,最低的FPGA使用量。这3种产品采用32位处理器的基本结构单元:32位指令大小、32位数据和地址路径32位通用寄存器和32个外部中断源;使用同样的指令集架构(ISA),100%二进制代码兼容,可以根据系统需求的变化更改CPU,选择满足性能和成本的最佳方案[1,2]。

2.2 AD9517-1ABCPZ

AD9517-1ABCPZ是Analog Device公司生产的时钟发生器,其工作电压+3.3 V,最大输入频率2 400 MHz,最大输出频率2 650 MHz,输出时钟为TTL电平或LVPEL电平[3]。

2.3 SPI总线

SPI总线系统是一种同步串行外设接口,可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接相连,该总线一般使用4条线:SDO(主设备数据输出,从设备数据输入)、SDI(主设备数据输入,从设备数据输出)、SCLK(时钟信号,由主设备产生)和CS(从设备使能信号,由主设备控制)等信号[4]。

3 实现方案

使用Nios II初始化、配置AD9517-1ABCPZ的实现方案可以分为两部分:硬件设计和软件设计[4]。硬件设计主要包括基于Nios II的SOPC系统的搭建,SPI-MASTER接口FPGA程序设计。软件设计主要包括:SPI读写函数设计,AD9517-1ABCPZ寄存器配置函数设计。

3.1 硬件设计

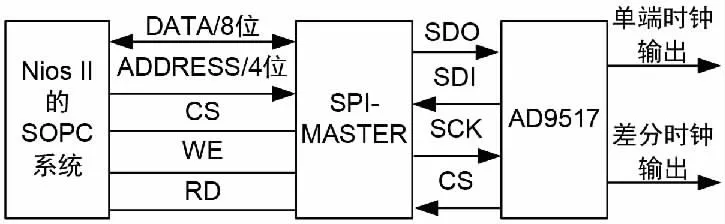

硬件设计包括:Nios II的SOPC系统和SPI-MASTER模块两部分。Nios II的SOPC系统通过并行的CPU接口与SPI-MASTER模块相连,SPI-MASTER通过 SPI接口与AD9517相连,其原理框图如图1所示:

图1 硬件系统原理框图

Nios II的SOPC系统,采用硬件程序和软件程序都存储在EPCS芯片的方式,采用该方式FPGA无需外接FLASH、SDRAM芯片,节省了电路板的布局空间以及成本,其主要包括以下几个部分[5]:①Nios II,系统的CPU;②On-chip Memory RAM,存储系统启动后的程序指令以及数据;③On-chip Memory ROM,存储只读数据,例如波形数据等;④EPCSSerial Flash Controller,控制EPCS芯片,指定启动地址;⑤JTAG UART,程序调试输出接口,相当于系统串行接口输出,用于观察调试过程中输出信息;⑥Avalon-MM Tristate Bridge,其用于连接以上5个部分;⑦Typical Avalon-MM Tristate Slave,系统的CPU接口,控制片选,读写信号等。以上7个部分组成一个简单的带有CPU接口的SOPC系统,用于承载AD9517-1ABCPZ配置程序。

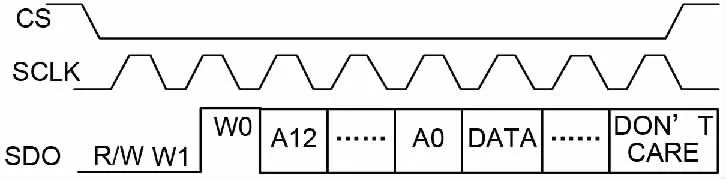

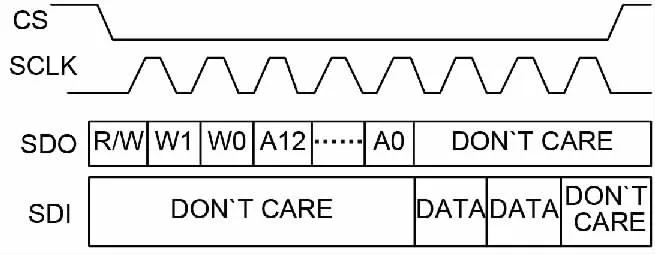

NIOS系统数据线是32位的,也就是按照32位进行读写操作。但图1所示的原理框图中DATA宽度是8位的,这样的话就会出现一个问题:若不对CS信号作调整,在一个读周期内CS信号会出现4次有效状态。要完成8位的读操作,就必须对CS信号进行调整:在Typical Avalon-MM Tristate Slave里加入4位Byteenable[3..0]信号,当Byteenable信号和RD信号同时有效时,CS信号才有效,这样就可以避免一个读周期内CS信号出现4次有效状态的情况。NIOS系统的读操作不会出现类似情况,所以数据读过程CS信号不需要调整[6]。AD9517-1ABCPZ的SPI接口默认是MSB方式,SPI-MASTER模块以MSB的方式设计,其读写时序图如图2和图3所示。

图2 SPI接口写时序

图3 SPI接口读时序

在FPGA内部,SPI-MASTER模块有以下几个寄存器,用于存储命令以及数据:①R/W寄存器,用于指示本次操作是SPI读操作还是SPI写操作;②W1WO寄存器,用于指示本次SPI读写操作要访问AD9517-1ABCPZ的寄存器个数;③地址寄存器,用于指示本次SPI读写操作要访问的AD9517-1ABCPZ的寄存器起始地址;④开始SPI读写寄存器,用于发起SPI读写操作;⑤状态指示寄存器,用于指示SPI读写操作是否为空闲;⑥写数据寄存器,用于暂存本次SPI写操作的数据;⑦读数据寄存器,用于暂存本次SPI读操作的数据。

R/W寄存器、W1WO寄存器、地址寄存器、开始SPI读写寄存器和状态指示寄存器等的内容用于指定本次SPI操作的属性,其决定了SPI接口的指令周期;写数据寄存器和读数据寄存器用于存储SPI接口的读写数据,其决定SPI接口的数据周期。

SPI的接口时序设计分为SPI读时序和SPI写时序2个部分。

SPI写时序:SPI接口的CS信号只有在“开始SPI读写寄存器”被置位后有效,其有效状态要一直保持到最后一个数据传输完成;SCLK信号的频率一要在AD9517-1ABCPZ的SPI接口SCLK频率范围内,其是SDO、SDI信号的同步时钟,可以由其他高频率时钟分频得到;SDO信号在SCLK时钟上升延依次输出“R/W寄存器”、“W1WO寄存器”、“地址寄存器”的内容,完成SPI接口的指令周期;SD0信号在SCLK时钟上升延依次输出由“W1WO寄存器”决定数据字节数,完成SPI接口的数据周期。

SPI读时序:SPI接口的CS信号只有在“开始SPI读写寄存器”被置位后有效,其有效状态要一直保持到最后一个数据传输完成;SD0信号在SCLK时钟上升延依次输出“R/W寄存器”、“W1WO寄存器”、“地址寄存器”的内容,完成SPI接口的指令周期;SD0信号在SCLK时钟上升延依次储存由“W1WO寄存器”决定数据字节数,完成SPI接口的数据周期。

3.2 软件设计

配置AD9517-1ABCPZ的NOIS系统软件设计可以分为2个主要的部分:SPI读写函数设计和AD9517-1ABCPZ寄存器配置函数设计。AD9517-1ABCPZ寄存器配置主要包括:SPI接口MSB或LSB寄存器配置、PLL使能寄存器配置、REFCLK选择寄存器配置、分频寄存器配置和倍频寄存器配置等,按照其手册进行配置就可以让其输出相应频率的时钟。SPI读写函数设计是该系统程序设计的重点,其决定SPI接口能否正常配置AD9517-1ABCPZ时钟芯片。

SPI读函数设计流程:①设置“R/W寄存器”为读指令状态;②设置“W1WO寄存器”,指示被读寄存器的个数;③设置“地址寄存器”,指示本次SPI读操作要访问的AD9517-1ABCPZ寄存器起始地址;④判断“状态指示寄存器”是否为空闲状态,若为空闲状态,则进行⑤的操作,若为忙状态,则等待;⑤设置“开始SPI读写寄存器”为开始读状态,发起SPI读操作;⑥等待SPI读操作完成,把暂存的数据读入Nios II的CPU接口;⑦SPI读操作完成后,由硬件FPGA程序,清除“开始SPI读写寄存器”的开始读状态,为下次读操作做准备。

在开始SPI读操作后,“状态指示寄存器”指示SPI读操作为忙状态,直到SPI读操作完成,“状态指示寄存器”再次指示SPI读操作为空闲状态。在2次SPI读之间,上一次读操作完成,才能开始下一次的读操作。本次SPI读操作完成后,才能把数据读入Nios II的CPU接口。何时把数据读入到Nios II的CPU接口的程序有2种方法设计:①不作任何判断,只在程序中加入足够的时延;②对“状态指示寄存器”的指示状态进行判断,在其指示忙状态时程序一直处于等待状态,但是等待要有一定的限度,在等待足够的SCLK时钟周期后,要跳出等待状态,若此时“状态指示寄存器”还是处于忙状态,则输出告警信息。

方法①的设计比较简单,其执行效率不高,可靠性比较低,适合于程序处于理想状态下运行的情况;方法2对状态进行判断,执行效率较高,虽然也进行了等待,但是在足够的SCLK周期以后就跳出等待状态,防止了程序死锁,程序执行的可靠性较高。

SPI写函数设计流程:①设置“R/W寄存器”为写指令状态;②设置“W1WO寄存器”,指示被写寄存器的个数;③设置“地址寄存器”,指示本次SPI写操作要访问的AD9517-1ABCPZ寄存器起始地址;④判断“状态指示寄存器”是否为空闲状态,若为空闲状态,则进行⑤的操作,若为忙状态,则等待;⑤设置“开始SPI读写寄存器”为开始写状态,发起SPI写操作;⑥等待SPI写操作完成;⑦SPI写操作完成后,由硬件FPGA程序,清除“开始SPI读写寄存器”的开始写状态,为下次写操作做准备。

在开始SPI写操作后,“状态指示寄存器”指示SPI写操作为忙状态,直到SPI写操作完成,“状态指示寄存器”再次指示SPI写操作为空闲状态。在2次SPI写之间,上一次写操作完成,才能开始下一次的写操作。这样的话在2次SPI写操作之间,要加入延时判断程序,若在每次SPI写操作之间都加入延时判断程序,会对程序执行效率带来较大影响。在SPI MASTER模块了加入适量的FIFO,用于缓存SPI写指令,结合FPGA程序的乒乓设计,可以较大的提高程序的运行效率。

4 结束语

使用NOIS II搭建的SOPC结合自主设计的SPI MASTER模块,可以灵活轻松的完成AD9517-1ABCPZ配置工作,让其输出系统所需的多种时钟。基于Nios II的SOPC系统设计简单灵活、开发周期短、成本低和系统维护升级方便,是许多中、低速系统设计不错的选择,今后必将在各个领域得到更广泛的应用。

[1]孟 芳,于立佳,张文志.基于NiosⅡ的SOPC系统设计分析[J].无线电通信技术.2012,38(1):73-76.

[2]ALTERA ComPany,Nios IIprocess Reference handbook.Ver13.1.0[R].ALTERA ComPany,2014.

[3]ANALOG DEVICESComPany,AD9517-1ABCPZ datasheet.Rev.D[R].ALTERA ComPany,2012.

[4]Freescale ComPany,The Freescale SPIBus Specification.VERSION 4.01[R].ALTERA ComPany,2004.

[5]侯建军,郭 勇.SOPC技术基础教程[M].北京:清华大学出版社,2008.

[6]ALTERA ComPany,Embeded Design handbook.Ver2.9[R].ALTERA ComPany,2011.