深亚微米并行CRC32编码芯片的设计和实现

2014-08-15郭宝增吴鹏飞

郭宝增,吴鹏飞

(河北大学 电子信息工程学院,河北 保定 071002)

CRC的全称是循环冗余校验(cyclic redundancy check),是一种非常著名的检错手段,在通信和数据存储领域得到广泛应用.其特点是检错能力极强,开销小,易于编码器及检测电路实现.从检错能力来看,其不能发现的错误的几率在0.004 7%以下.著名的通讯协议X.25的FCS(帧检错序列)采用的是CRC-CCITT;ARJ,LH等压缩工具软件采用的是CRC32;磁盘驱动器的读写采用了CRC16;通用的图像存储格式GIF,TIFF等都使用CRC作为检错手段[1].

1 CRC32算法研究

1.1 LSFR串行编码算法

CRC32属于线性分组码的分支,同时还具有循环特性,符合一般循环码的编码方法[2],其过程可以采用LSFR实现编码电路,这种电路主要由移位寄存器和异或门组成[3-4].对于CRC32校验码,生成多项式为

g(x) =x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1.

(1)

以8 bit的数据输入为例,其硬件实现框图如图1所示.

图1 LSFR串行编码电路Fig.1 LSFR serial encoder circuit

图1中,32位移位寄存器用于存储CRC32校验码,称其为CRC寄存器.编码前将寄存器各位置1,每个时钟周期1 bit数据输入,通过移位和异或运算,CRC寄存器中的数据进行随之更新,8个时钟周期后,数据输入完毕,此时CRC寄存器的值即为CRC32的码序列,该算法原理简单,便于硬件实现,但效率不高,主要应用于串行通信.

1.2 并行CRC32算法

从本质上说,LSFR算法是一种串行算法,针对LSFR电路效率低的问题,本文从LSFR电路的结构入手,通过相应的逻辑运算推导出高效并行的CRC32编码算法.

(2)

(3)

(4)

(5)

(6)

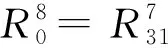

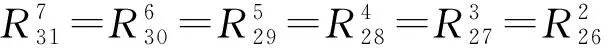

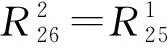

将(3),(4),(5),(6)式代入(2)式,可以求得

(7)

即移位寄存器R0经过8个时钟后的状态值可以表示为移位寄存器R30,R24的初始值与输入数据D7,D1的异或运算,这样就可以将LSFR中8 bit的串行输入数据转换为等效的并行输入,将其记做CRC0.按照上述的推导原则,可以求得其他31个寄存器经过8个时钟后的状态值.

8 bit并行输入,经过并行运算单元运算之后,将运算结果存储到移位寄存器R0-R31,移位寄存中的值有2个用途:当前时钟周期下,直接以运算结果的形式作为输出;下一时钟周期作为保护数据反馈到并行运算单元,共同作用到下一时钟周期.

2 并行CRC32算法的FPGA验证

在算法研究的基础上,鉴于ASIC(application specific integrated circuit)流片成本高,风险大,因此大规模量产之前需要事先对芯片的设计进行FPGA验证.通过验证,一方面可以确保系统逻辑功能的正确;另一方面可以说明系统的时序基本可以满足设计要求[3].

依据推导出的逻辑关系,编写并行CRC32算法的verilog代码[5]

module crc(

input[7:0] data_in,

input crc_en,

output [31:0] crc_out,

input rst,

input clk);

reg[31:0] lfsr_q,lfsr_c;

assign crc_out = lfsr_q;

always @(*) begin

lfsr_c[0] = lfsr_q[30] ^ data_in[7] ^ lfsr_q[24] ^ data_in[1];

⋮

lfsr_c[31] = lfsr_q[23] ^ lfsr_q[29] ^ data_in[2];

end

always @(posedge clk, posedge rst) begin

if(rst) begin

lfsr_q <= {32{1’b1}};

end

else begin

lfsr_q <= crc_en ? lfsr_c : lfsr_q;

end

end

endmodule

生成的并行CRC32编码模块如图2所示.

图2中data_in为8位数据输入端;crc_en为使能端,只有当crc_en为高电平时,编码器才进行编码工作;rst为复位信号(高电平有效),当电平为高时,进行初始化;clk为时钟信号;crc_out为32位CRC编码输出端.

通过编写testbench,利用Modelsim软件对生成的编码模块进行功能仿真,其仿真结果如图3所示.

图3 并行CRC32编码电路功能仿真结果Fig.3 Function simulation result of Parallel CRC32 encoder circuit

仿真输入数据为8’h12,8’h34,8’h56,8’h78,8’h9a,8’hcf;得到的CRC32校验码为16’h5c86227b,16’h669666e7,16’ha36a7c64,16’he68f6fad,16’h0a1e9dc3,16’hb5ecce06,通过观察仿真结果,其编码结果与理论计算的结果一致.

将编译后的工程文件下载到DE2-70开发板,通过实验检测,可以得到一致的输出结果,至此芯片代码的FPGA验证工作结束.

3 并行CRC32编码芯片的实现

FPGA的使用费用太高,资源利用率较低;在功耗、设计密度以及产品的运算速度方面相对ASIC来说存在相当程度的劣势,因此,为了实现产品的大规模生产,必须进行系统逻辑的版图GDS II设计.设计过程采用中芯国际180 nm的数字工艺库,主要使用Synopsys公司的Design Compiler逻辑综合软件,和Cadence公司的Soc Encounter自动布局、布线软件实现版图的GDS II文件设计.

3.1 编码电路的逻辑综合

使用Design Compiler软件,对编码电路的verilog代码进行逻辑综合,其主要工作包括:一方面将硬件语言描述的行为级电路、RTL级电路转换到基于工艺库的门级网表[6];另一方面要根据综合产生的时序报告,对综合过程中的各项参数进行修改,以保证时间余量(slack)为给定时钟的30%以上,这是由于综合过程中设置的连线负载只是工艺库提供的延时参数,并不是实际延时,必须以足够的slack为后续的实际布局、布线提供充足的延时空间,图4为综合后的时序报告.

图4 逻辑综合时序报告Fig.4 Logic synthesis timing report

从图中可以看出给定的时钟clk为10 ns,而综合后的slack为6.18 ns,超过要求的最少时间余量3 ns,说明综合过程可以提供充足的时间余量用于布局、布线.

将满足上述要求综合后的verilog文件(门级网表文件)和sdf文件(时序约束文件)进行导出,采用Formality形式验证工具对综合后的网表进行逻能的验证,形式验证相对于时序仿真的优势在于,能够以较短的时间消耗比较综合前、后电路逻辑功能是否一致.

3.2 编码电路的布局、布线

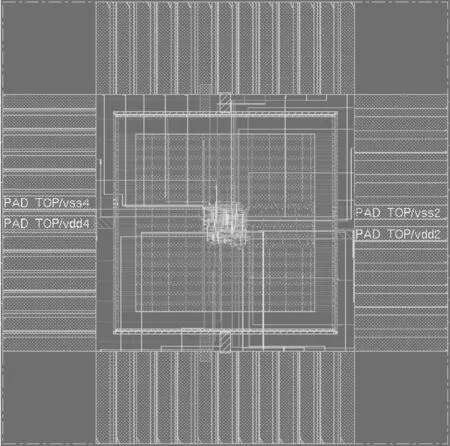

使用Soc Encounter软件,导入逻辑综合后的verilog文件和sdf文件,完成版图GDS II的设计,设计过程需要针对版图的面积、时序进行分析,采取面积约束、优化布局布线、时钟数综合等方法达到合理的版图设计,随后完成版图的LVS比较和DRC规则检查,得到的版图文件如图5所示.

图5 并行CRC32编码芯片版图Fig.5 Parallel CRC32 encoder chip layout

3.3 编码电路的时序仿真

上面提到过对于验证电路功能是否与原始代码一致可以采用形式验证工具Formality.而本设计是优化的并行电路结构,其结构简单,使用的逻辑单元较小,时序仿真的耗时可以接受,因此可以采用Modelsim对编码电路进行时序仿真加以验证,时序仿真的结果如图6所示.

图6 并行CRC32编码芯片时序仿真结果Fig.6 Timing simulation result of Parallel CRC32 encoder chip

通过比较功能仿真和时序仿真结果,可以证明所设计芯片完全能够实现CRC32的并行编码功能.

4 结语

在研究CRC算法及编码原理的基础上,从代码编写到GDS II版图生成,完成了数字集成电路前端到后端的整个设计流程;所实现的编码芯片能够以高效的速率完成编码工作.此外,本文介绍的芯片设计方法对了解和掌握数字芯片设计思想起到一定的指导作用.

参 考 文 献:

[1] 张树刚,张遂南,黄士坦.CRC校验码并行计算的FPGA实现[J].计算机技术与发展,2007,17(2):56-62.

ZHANG Shugang,ZHANG Suinan,HUANG Shitan.CRC Parallel Computation Implementation on FPGA[J].Computer Technology and Development,2007,17(2):56-62.

[2] 樊昌信,张甫翊,徐炳祥,等.通信原理[M].北京:国防工业出版社,2001.

[3] SHIEH M D,SHEU M H,CHEN C H,et al.A systematic approach for parallel CRC computations [J].Journal of Information Science and Engineering,2001,17:445-461.

[4] RAMABADRAN T V,GAITONDE S S.A tutorial on CRC computations[J].IEEE Micro,1988(8):62-75.

[5] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[6] 韩雁,洪慧,马绍宇,等.集成电路设计制造中EDA工具实用教程[M].杭州:浙江大学出版社,2007.