在IC设计中应用STA处理时序问题的方法

2014-08-07孙佳佳赵庆哲

孙佳佳,赵庆哲

(中国电子科技集团公司第四十七研究所,沈阳110032)

在IC设计中应用STA处理时序问题的方法

孙佳佳,赵庆哲

(中国电子科技集团公司第四十七研究所,沈阳110032)

当代数字IC的设计规模和复杂性在不断增加,验证工作也越来越困难,特别是静态时序分析在此背景下变得尤为重要。目前业界普遍采用自动化的设计方式,通过应用工具软件,来对设计时序进行分析。主要探讨了在IC设计当中对于时序违例的一些处理方法。

数字IC;静态时序分析;建立时间;保持时间

1 引 言

当代数字IC的设计规模和复杂性在不断增加,设计的时序验证已经成为制约成品率的一个重要因素。是否能够全面分析设计时序关系到产品的成败。然而,设计过程中不可避免地会出现一些与要求时序相违背的情况,怎样处理这些问题是静态时序分析的一个重要方面。本文主要阐述了在设计中对静态时序分析时序违例的处理方法。

2 静态时序分析中时序分析对象

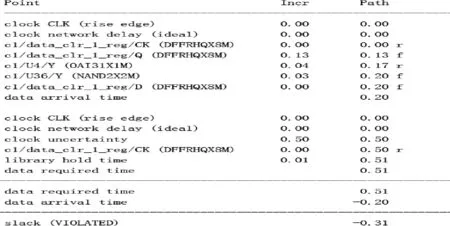

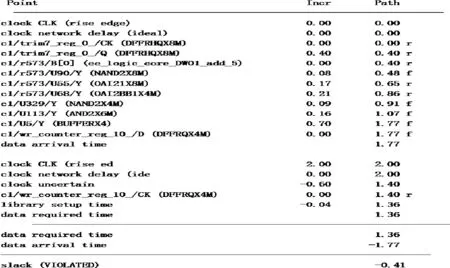

在静态时序分析中,时序分析工作主要检查设计的建立时间和保持时间,即setup timing和hold timing。关于以上检查目标的概念,这里就不再赘述。设计的时序违背主要体现在这两个时序目标的违背。图1是保持时间违背的情况,图2是建立时间违背的情况。

从图1可以知道,保持时间的违背在电路上是相邻两个寄存器之间的组合逻辑路径延迟过小,导致前一个寄存器的数据在时钟边沿有效期的后段存入了后一个寄存器中,从而导致逻辑混乱。也即由于寄存器之间的延迟较小,导致后一个数据追赶上了前一个数据,从而将前一个数据冲掉,导致逻辑错误。而建立时间的违背则是相邻的两个寄存器之间组合逻辑路径的延迟较大,导致在时钟上升边沿到来的时候,有效数据还没有到达,此时寄存器存储的是有效数据之前的数据,从而引起数据发生错误。这两种时序违背的情况都会导致逻辑错误,是比较典型的违背情况,也是静态时序分析的重点,关系到整个系统的功能正确性,因此,我们着重探讨如何分析并处理这两种时序问题。当然,对于静态时序分析而言,其本身并不改变设计的逻辑功能,而是通过一些手段方式来检查导致时序问题的原因并提供给后端设计者作为时序修正参考。

3 时序违背的处理方法

这是本文论述的重点。作者在实际工作中,总结出了静态时序分析中对于时序问题的方式方法:对于保持时间的违背,其实质是相邻寄存器之间的组合路径延迟不够,因此,我们可以试着从增加组合逻辑的延迟入手来解决这个问题,常用的办法是在逻辑路径中插入buffer或delay元件。但是究竟插入什么元件还需视电路情况而定。对于图1的情况,我们可以利用静态时序分析工具软件在c1/U36/Y(NAND2X2M)与c1/data_clr_1_reg/D(DFFRHQX8M)之间插入一个delay元件,这个元件的作用是增加相关逻辑路径上的延迟,从而解决保持时间的问题,但是这样做的一个不良影响就是如果加入的延迟过大,可能导致建立时间的违背或者设计规则比如最大转换时间的违背,因此每增加一个delay,都要评估其对整体时序的影响。对于delay和buffer两种元件,我们应当如何选择插入路径呢?一个基本原则就是如果保持时间的违背情况比较严重,可以考虑加入delay,如果不十分严重,可以考虑插入buffer。同时还要兼顾上下级电路的驱动能力情况。

图1 保持时间违背情况

图2 建立时间违背情况

对于建立时间的违背,本质上与保持时间的情况正好相反,寄存器之间组合逻辑的延迟过大导致数据不能及时向下传递,因此,提出的解决办法是减少组合逻辑的延迟。此时可以观察电路的延迟情况,找出制约建立时间的原件,用其它延迟小的同类器件来替代本元件从而达到减少电路延迟的目的。在图2中,观察电路延迟,发现在数据路径的末端,c1/U5/Y单元,也就是BUFFERX4的延迟为0.70ns,因此,可以减少此元件的延迟。通常,对于BUFFER器件,驱动能力越大延迟越小,因此,我们可以将BUFFERX4替换为BUFFERX12,重新进行分析,观察分析结果。如果还是达不到要求,那么采用再增大驱动能力的方法来解决。

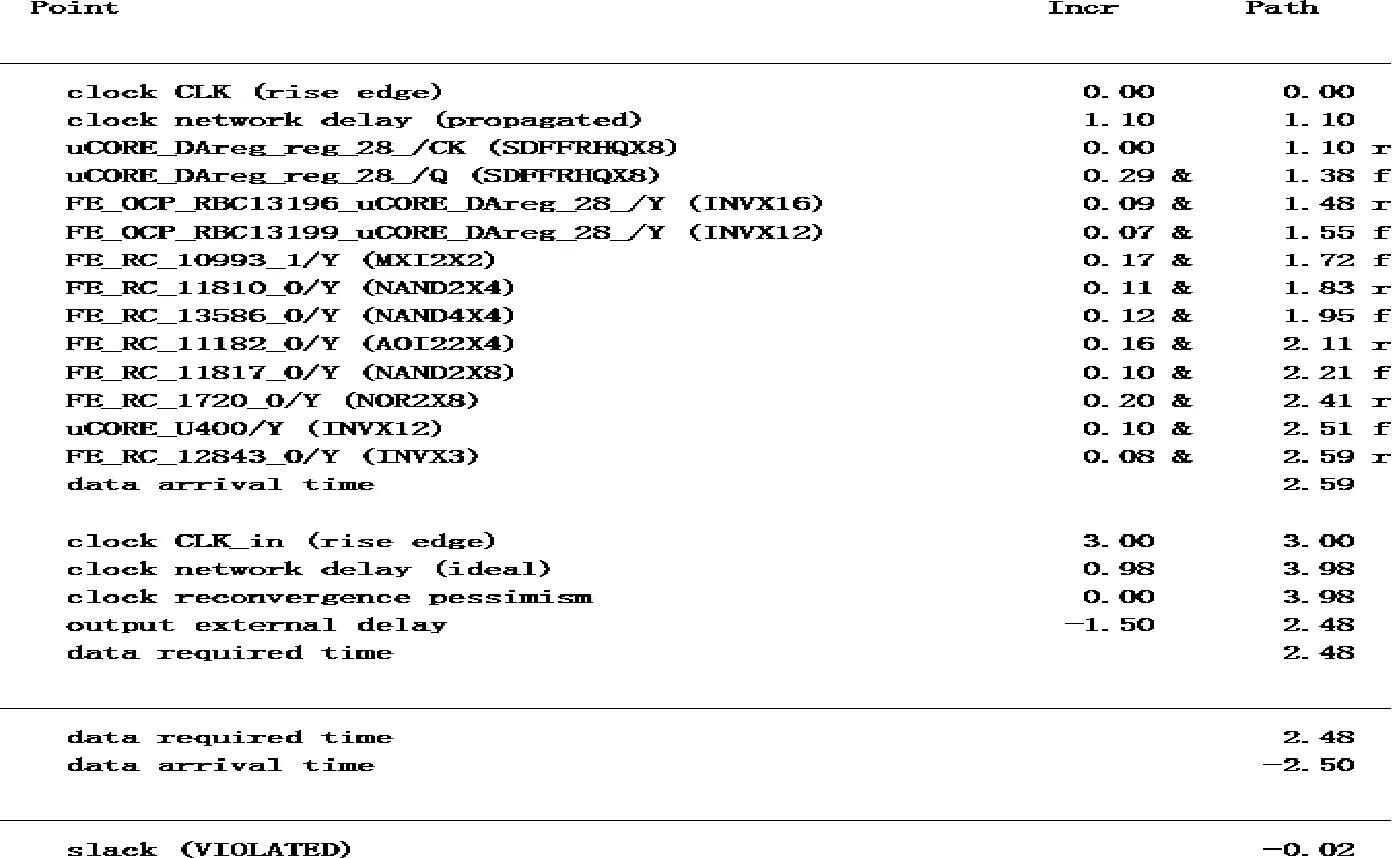

图3是在实际工作中分析的某型芯片的时序分析报告,将它作为一个典型案例来讲解具体的时序问题解决方法。

图3 实际的建立时间违背情况

报告分析的是setup timing的结果,最后部分提示有-0.02纳秒的时序违背,仔细观察该报告体现的时序路径,其中FE_OCP_RBC13199_uCORE_ DAreg_28_,也即INVX12的延迟为0.07纳秒,其本身延迟并不大,但是下级电路的延迟有进一步缩小的空间,因此,我们用INVX16来代替INVX12,以增大驱动的方式来减少下级电路的延迟时间,修正后的报告如图4所示。

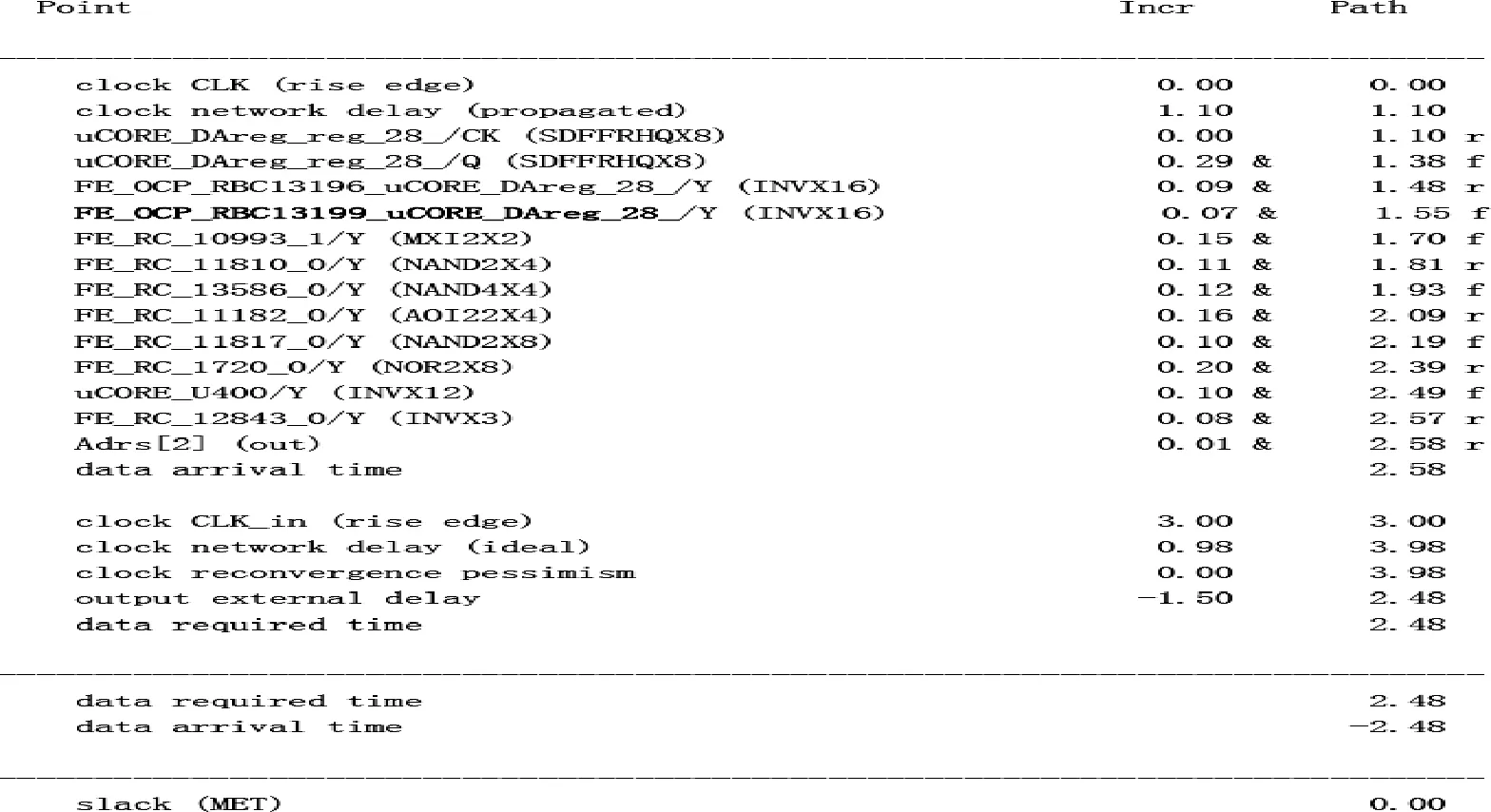

图4 修正后的建立时间状况

从报告中可以看到,由于INVX12变为了INVX16,因此下级电路的延迟时间由0.17纳秒变为0.15纳秒,整个路径的setup timing时序满足了既定要求。

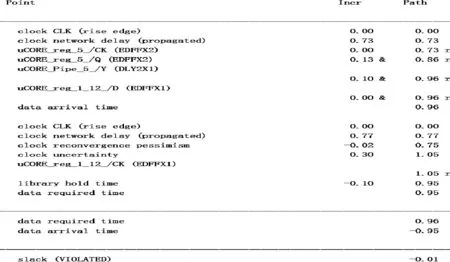

对于hold timing的修正,也以一个例子来阐述,图5是在实际工作中分析过的某型芯片的保持时间时序报告。

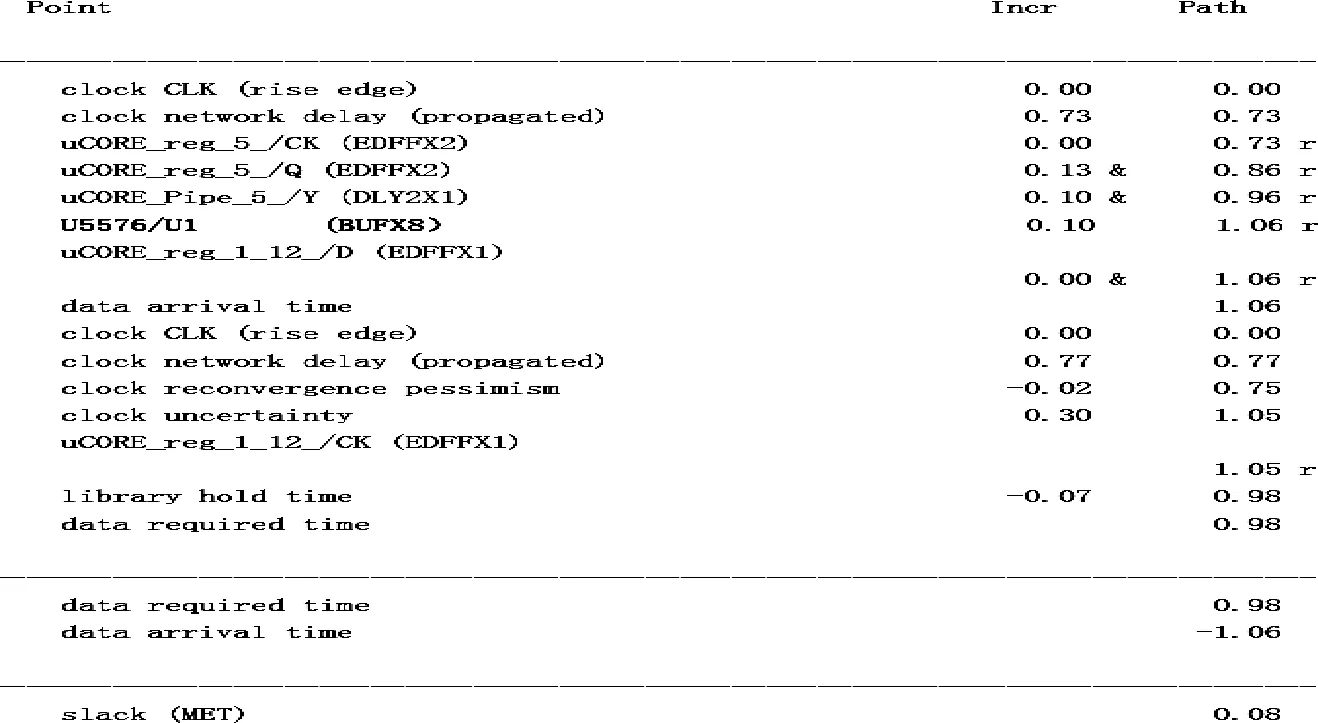

该报告提示路径存在着-0.01纳秒的时序违背情况,仔细观察路径,在uCORE_Pipe_5_/Y后面增加一个缓冲元件来增大路径延迟,从而修正hold timing的违背。修正后的报告如图6所示。

经过修正,hold timing变为0.08纳秒,满足了时序要求。

以上是在实际工作中总结出的对时序违背的处理方式,这是一种普遍方法。在实际工作中,如果后端对电路处理比较合理,那么在时序分析的时候处理的空间就很小,这时候就需要通过修改设计结构来改善时序。

应该注意,在修正建立时间违背的时候,由于逻辑电路延迟的减少,可能带来保持时间的违背,因此,设计者对器件的选取应该有一个大致的印象,不要盲目选择延迟大的器件,而是应该有目的地遵循由小到大的顺序来进行,之所以这样做是为了防止由于驱动过大而导致电流增大从而导致电迁移现象,这一点在深亚微米设计中尤为突出。

图5 实际的保持时间违背情况

图6 修正后的保持时间状况

4 结束语

静态时序分析是一个时序分析工具,它不能对设计进行改变,因此,上述方法旨在考察修正时序的切入点,而不是真正的修正设计时序。它提供了一种对设计的修改意见,反馈给P&R人员,由其来对设计进行修正,再将其修正结果回馈到静态时序分析工具来进行分析。由于不同的工具处理时序的算法可能有差别,因此,一般要经过反复迭代之后,最终才能得到符合要求的设计时序。

应该说,静态时序分析不光能分析设计的时序,还能分析设计规则如最大转换时间和电容等参数,同样是将分析结果反馈给P&R人员,修正后再反馈回来直到符合设计要求为止。

静态时序分析要求分析人员对逻辑电路时序有一个准确的把握,能找到影响时序的关键点,并能对此点进行有效处理。因此,分析人员要仔细对时序报告进行观察,找到合适的电路节点,采取有效的插入或替换方式,这样,才能对设计的时序全方位分析,提出一个正确的修正方法,从而减少设计的迭代时间。

[1]Himanshu Bhatnagar.高级ASIC芯片综合[M].张文俊,译.北京:清华大学出版社,2007.

[2]Zainalabedin Navabi.Verilog数字系统设计[M].李广军,陈亦欧,李林,窦恒,等译.北京:电子工业出版社,2007.

[3]Weste,Harris.CMOS超大规模集成电路设计[M].汪东,李振涛,李宝锋,等译.北京:中国电力出版社,2005.

Process Way for Tim ing Violation by STA in IC Design

SUN Jia-jia,ZHAO Qing-zhe

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

With increasing in scale and complication of the digital IC design,the verification becomesmore difficulty,especially the STA is getting extremely important under this background.Now the CAD is used in the IC design to analysis timing.This papermainly discusses the solution of timing violation in IC design.

Digital IC;Static Timing Analysis;Setup timing;Hold Timing

10.3969/j.issn.1002-2279.2014.04.005

TN492

:B

:1002-2279(2014)04-0015-04

孙佳佳(1980-),女,辽宁沈阳人,工程师,主研方向:集成电路设计。

2013-12-27