基于FPGA的列车信号采集系统设计与研究

2014-08-07陈安林林腾达

陈安林,刘 继,林腾达

(同济大学铁道与城市轨道交通研究院,上海201804)

基于FPGA的列车信号采集系统设计与研究

陈安林,刘 继,林腾达

(同济大学铁道与城市轨道交通研究院,上海201804)

列车工况信号对列车故障检测与分析有重要意义。以CycloneⅢ系列FPGA、AD9220、SRAM作为主要器件,利用MAX038输出信号以模拟列车工况信号,再对信号进行采集、存储进行系统设计与分析。为保证系统的稳定性和可靠性,制作了PCB板对系统进行测试。

信号采集;AD9220;静态数据存储器;现场可编程门阵列

1 引 言

铁道车辆的大幅提速给人们生活带来了极大方便,而列车安全问题也越来越引起人们的关注,因此列车故障检测与分析的重要性就突显出来。高铁在运行过程中,轮对等转向架部件磨损十分剧烈,并且部件的微小偏差也可能引起重大事故。在实际故障检测与分析中,以列车振动、噪声等信号作为依据。现有一种构想:先在轨道上布置多个传感器,当列车通过时采集轨道的振动信号,再通过AD转换器将各端电信号转换为数字信号,传输到FPGA和SRAM中,然后将各端信号通过光纤传输到总处理端,总处理端通过USB将信号传给上位机,最后在上位机上进行信号分析处理。这些信号数据量大、输出频率高。

为了解决这一问题,现专门针对前段数据的采集与存储,设计了一种高速数据采集与存储系统,它的数据采集功能完全由硬件完成。

2 系统硬件设计

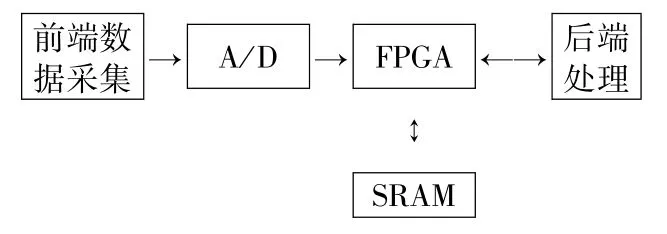

系统设计方案如图1所示,首先采用高速AD(模数转换)芯片采集数据,每采一个数据便通过FPGA将数据存入到SRAM芯片当中,这样能高速采集一长段连续数据;当需要读取时,再通过FPGA将数据从SRAM当中读出。主要针对前端数据采集与存储部分,故后端处理不做分析。

图1 系统信号采集与传输流程图

2.1 FPGA

主控芯片FPGA采用Altera公司的Cyclone III系列芯片EP3C25Q240C8。该芯片具有LE 24624个,M9K存储器模块66个,存储器总数量0.6Mbits,乘法器66个,PLL 4个,全局时钟20个,最大用户I/O引脚数量215个。

2.2 A/D

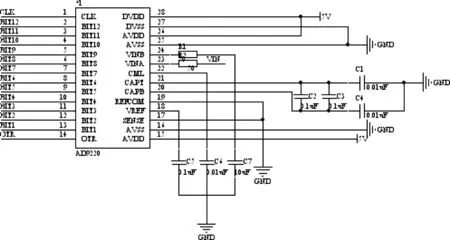

模数转换芯片采用Anolog Devices公司的AD9220芯片,此芯片驱动电压为+5V,最高采样速率为10Ms/s,采样精度为12bit,广泛应用于通信设备。AD9220电路的速率取决于输入时钟的频率,本实验利用FPGA控制AD的时序。其结构原理图如图2所示。

图2 AD9220结构原理图

2.3 SRAM

这里采用缓存设备对连续采集数据进行缓存处理,因此这里采用ISSI公司的IS61NLP102418芯片,该芯片最高存贮时钟频率可达200MHz,容量为1M×18bit。其具体操作的真值表如表1所示。

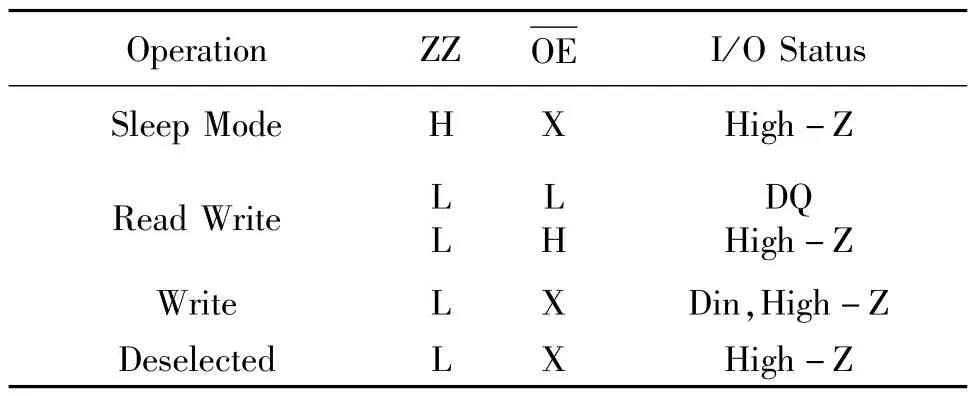

表1 IS61NLP102418真值表

图3 Vpp为1V,频率为50KHz的正弦波输入信号

3 实验调试

3.1 AD实验

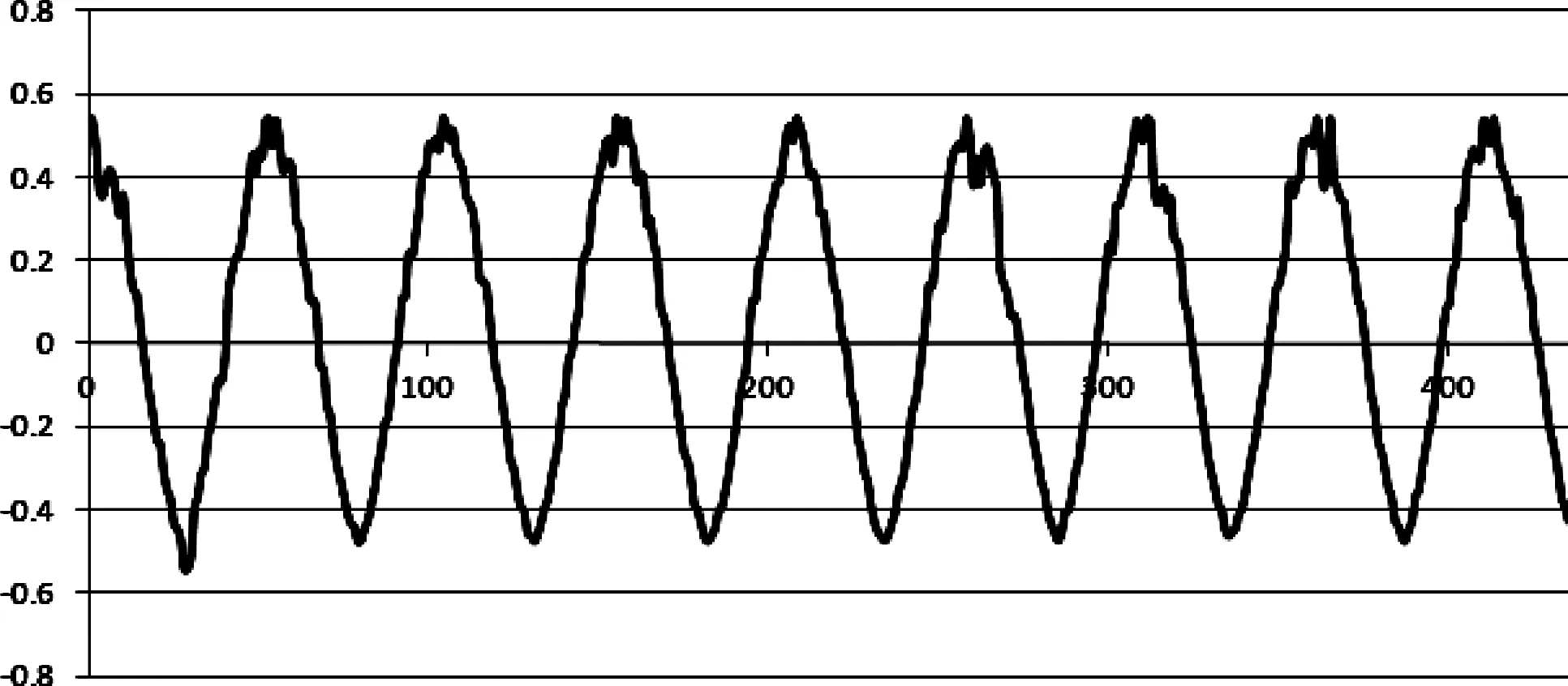

AD数据采集模块实验中,采用MAXIM公司的MAX038来产生需要的测试信号。利用该芯片产生Vpp为1V,频率为50KHz的正弦波如图3所示。根据Nyquist采样定理,Fs.max≥2Fmax,则采样之后的数字信号完整保留了原始信号中的信息。AD9220的外围电路连接如图4所示。

利用FPGA开发软件Quartus II内置的逻辑分析仪SignalTap II采集FPGA中与AD输出管脚相连的12个I/O口的BIT1~BIT12数据,并导入Excel中描述图形,如图5所示。

图4 AD9220外围电路图

图5 采集信号波形图

3.2 SRAM实验

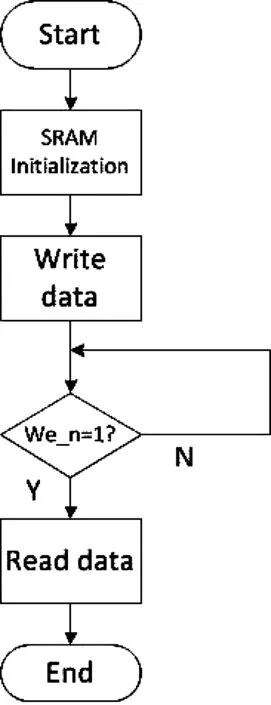

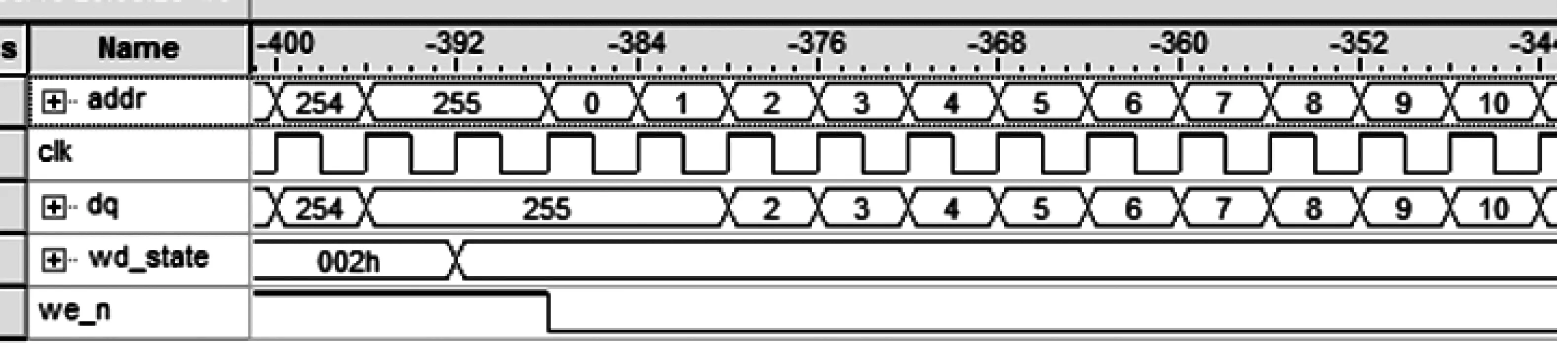

SRAM数据缓存模块实验中,利用FPGA对SRAM写入0~255这256个数,并在写完后从SRAM中读取数据,若数据相同则表示SRAM设计正确,当we_n为0时表示写SRAM。we_n为1时表示读SRAM,控制流程如图6所示,实验数据如图7和图8所示,表明SRAM电路正常工作。

图6 SRAM控制流程图

图7 SRAM写数据

图8 SRAM数据读取

4 结束语

以FPGA、AD9220、SRAM等器件为基础,设计和研究了高速数据采集与存储硬件电路,并制作PCB板进行测试。验证了系统数据采集与存储的正确性与稳定性。本文中所使用信号是利用MAX038芯片产生的正弦波,用它来模拟列车运行信号,符合实际需求。

[1]刘静.某雷达术A/D转换器AD9220及其应用[J].火控雷达技术.2003,32(3):26-28,50.

[2]周昊,柳刚,陈四海,等.用于检测红外焦平面阵列探测器信号的高速数据采集系统[J].红外技术,2005,27(2):171-174.

[3]杨全玖,张大伟,吕宗芳,等.以AD9220为核心的高速模数转换电路在核探测中的应用[J].微计算机信息,2006,22(29):92-93,98.

[4]Altera Corporation.CycloneⅢDevice Handbook[J].2012(2):1-34.

[5]Integrated Sillion Solution.IS61NLP25672/IS61NVP 25672IS61NLP51236/IS61NVP51236IS61NLP102418/IS61NVP102418[J].2006,(1):1-34.

[6]Analog Devices.AD9221/AD9223/AD9220[J].2003(5):1-32.

Design of Train Data Collection System Based on FPGA

CHEN An-lin,LIU Ji,LIN Teng-da(Institute of Railway&Urban Rail Transit,Tongji University,Shanghai201804,China)

The signal of the train working condition is very important for the fault detection and analysis of the trains.This article simulates signals of train working condition and designs a circuitmainly composed of field programmable gate array chip,AD9220 and static RAM,which enables high-speed data collection and data storage.A PCB is designed to protect the stability of the system.

Data collection;AD9220;SRAM;FPGA

10.3969/j.issn.1002-2279.2014.03.020

TP3

:A

:1002-2279(2014)03-0070-02

陈安林(1989-),男,安徽安庆人,硕士研究生在读,主研方向:工业自动化控制。

2013-11-04