基于FPGA三相正弦信号发生器的设计与实现

2014-07-20晏勇

晏勇

(阿坝师范高等专科学校物理与电子科学系,四川汶川 623002)

基于FPGA三相正弦信号发生器的设计与实现

晏勇

(阿坝师范高等专科学校物理与电子科学系,四川汶川 623002)

Alter公司CycloneⅡ系列EP2C20Q240C8为核心处理器,设计基于LPM_ROM三相正弦信号发生器。通过读写LPM_ROM正弦波数据,QuartusⅡ开发平台完成综合仿真配置,SignalTapⅡ嵌入式逻辑分析仪实时捕获显示三相正弦信号,连接10位串行D/A转换器TLC5615实现既定功能。

EP2C20Q240C8;LPM_ROM;三相正弦波;SignalTapⅡ;TLC5615

0 引 言

随着电子信息技术的发展,三相正弦信号发生器作为一种基础测量仪器广泛应用于计算机、通信、电力电子等行业及相关实验室。传统模拟信号发生器硬件电路复杂繁琐,输出波形受使用时间、硬件和环境因素影响大,输出信号频率和幅度漂移大、稳定性差、精度低。本文根据实际需要设计了基于FPGA三相正弦信号发生器,采用FPGA为核心控制器,用纯软件方法实现三相信号,实践证明利用FPGA设计三相信号发生器体积小、可靠性高、精度高、漂移小、功耗低,具有很高的实用价值,可广泛用于实际生产。

1 系统总体设计与功能模块

基于FPGA三相正弦波发生器由FPGA最小系统、频率合成器、地址发生器、LPM_ROM正弦波查找表、D/A转换器和滤波电路等模块构成如图1。FPGA最小系统包含系统供电电路、系统基准时钟、JTAG配置端口、AS配置端口、EPCS4配置器件、USB-blaster等;LPM_ROM存储器存储正弦波数据;频率合成器由FPGA内部锁相环构成,实现系统时钟倍变频,在频率合成器输出时钟控制下产生LPM_ROM正弦波查找表地址,通过D/A转换与滤波电路还原正弦波信号。频率合成器输出时钟越高,地址发生器产生地址频率越高,查找表寻址速度越快,输出正弦信号频率越高。三相正弦交流信号电压相位相差120°,计算三相正弦信号周期,改变LPM_ROM正弦波数据,得到稳定三相信号。

图1 基于FPGA三相正弦波发生器系统框图

2 三相正弦波信号设计

2.1 LPM_ROM宏功能模块制定

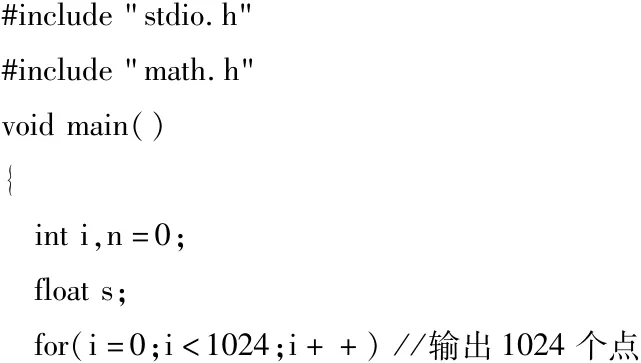

LPM_ROM宏功能模块制定分为ROM初始化和LPM_ROM宏功能模块调用及设定。ROM初始化是向ROM中写入三相正弦波一个周期采集数据点,ROM地址发生器通过寻址查找存储在ROM的正弦波数据信号。QuartusⅡ接受两种初始化文件Memory Initialization File(.mif)和Hexadecimal(.hex)格式,常用mif格式[1]。Mif文件生成方法有直接编辑法、文件编辑法、编程语言生成法和专用mif文件生成器,正弦波信号采集用直接编辑法和编程语言生成法混合生成正弦波mif文件。新建Memory Initialization File文件,设置采集数据宽度为10位,深度1024;将生成数据导入mif文件,完成mif文件制定[2],C语言程序格式如下:

LPM_ROM调用和设置,在原理图模式下单击Mega Wizard Plug-In Manager管理器,选择Create a new Megafunction variation复选框,Memory Compiler选择ROM:1-PORT,设置输出数据宽度10 bit,数据深度1 024 bit,存储器构建方式M9K,指定路径载入mif文件,完成ROM制定。

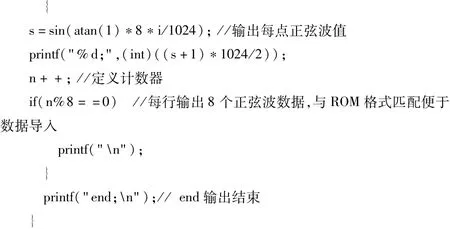

ROM地址信号发生器,由计数器产生,数据宽度10 bit,可以采用VHDL文本制定,也可以采用LPM_Counter制定,改变计数器步进长度,可改变输出信号频率。单相正弦波顶层文件包含地址发生器和ROM存储器,顶层文件如图2,功能仿真如图3。原理图模式下选择Creat/Update-Creat Symbol Current File建立原件符号为三相正弦波发生器调用[3]。

图2 正弦波顶层文件

图3 正弦波功能仿真图

2.2 移相模块设计

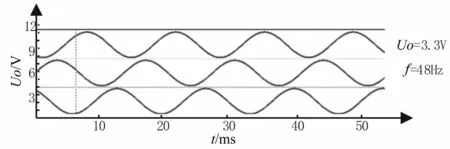

地址信号发生器时钟inclk频率f0与每个周期采集正弦波点数及D/A输出正弦波频率关系f=,正弦波每个周期采集1 024个点,周期内采集正弦波点数越多输出波形失真越小,ROM地址总线宽10 bit,深度1 024,输入信号频率为系统时钟频率50 MHz,D/A输出正弦波频率48 kHz。三相正弦波相与相间幅度频率相同,位相差120°,一个周期内B相比A相滞后,C相比B相滞后,ABC三相分别建立3个ROM顶层文件,通过文件中不同mif文件产生ABC三相信号[5],A相mif文件周期正弦信号采集点相位从0°~360°,B相mif文件周期正弦信号采集点相位从+120°~-120°,C相mif文件周期正弦信号采集点相位从+240°~-240°,实现ABC三相正弦信号[6-7]。

2.3 顶层电路设计与仿真

三相正弦信号发生器分别由ABC单相正弦信号作为底层文件生成顶层文件,三相信号发生器顶层文件如图4,功能仿真后波形文件[8-9]如图5。

图4 三相正弦波发生器顶层文件

图5 三相正弦波发生器波形仿真图

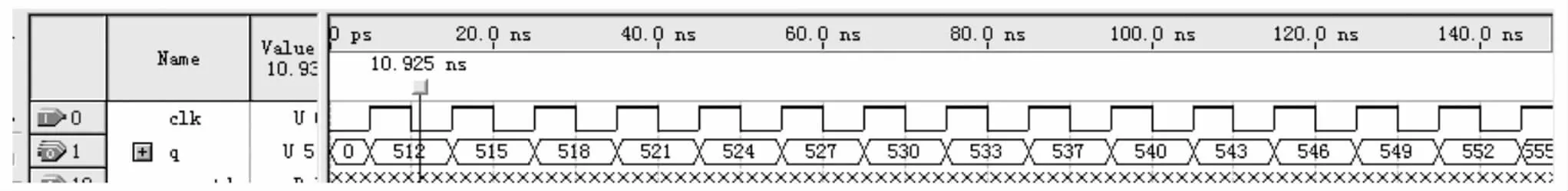

SignalTapⅡ嵌入式逻辑分析仪捕捉系统内部节点或总线数据流,不影响系统正常工作,将捕捉样本信号暂存于目标器件嵌入式RAM中,通过JTAG配置端口送入计算机显示和分析[10]。在NEW窗口中选择SignalTapⅡLogic Analyzer File建立SignalTapⅡ文件,SignalTapⅡ待测文件Instance与文本文件实体名相同;调入待测信号并设置SignalTapⅡ参数,工作时钟CLK,采样深度4K,JTAG模式下启动SOFManager下载sof文件并进行配置,待测信号选择总线模式Bus Display Format-Unsigned Line Chart[11]运行SignalTapⅡ实时采集波形如图6。

图6 三相正弦波发生器SignalTapⅡ嵌入式逻辑分析仪采集波形图

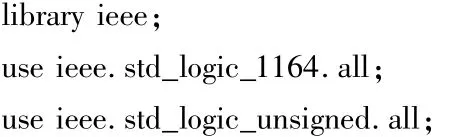

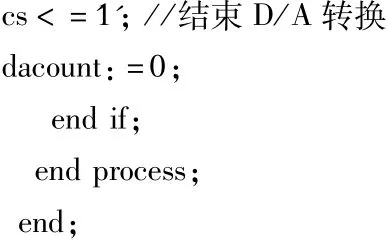

3 D/A转换电路设计

TLC5615是TI公司SPI串行10位D/A转换器DIP8封装,电源VCC为5 V,基准电压VREF为2 V,片选信号CS低电平有效,串行输入最高频率14MHz,3根串行总线完成10位D/A转换数据输入输出[12]。TLC5615内部包含一个10位DAC寄存器;一个16位移位寄存器分为高4位虚拟位,低两位填充位和10位有效位;两种工作模式,模式1:12位数据序列方式,向16位移位寄存器输入高10位D/A转换有效位,低两位填充位输入任意两位数字,12个时钟脉冲;模式2:16位数据序列方式,比模式1增加4位虚拟位,16个时钟脉冲。输出电压,N输入二进制数,D/A串行通信VHDL程序如下[13]。

4 结束语

设计利用EDA技术,在QuartusⅡ上完成了系统开发与仿真测试,使硬件功能通过软件实现,缩短了开发周期,提高开发效率。测试结果证明基于FPGA三相正弦波发生器具有精度高,稳定度高,设计灵活简单易升级等特点,可广泛用于实际生产和教学。

[1]陈赜.CPLD/FPGA与ASIC设计实践教程[M].北京:科学出版社.2010,9:120-160.

[2]潘松,黄继业.EDA技术实用教程—VHDL版[M].北京:科学出版社.2010,6:160-293.

[3]李俊.EDA技术与VHDL编程[M].北京:电子工业出版社,2012,6:91-136.

[4]张洪润,张亚凡.FPGA/CPLD应用设计200例(下册)[M].北京:北京航空航天大学出版社.2009,1:113-332.

[5]邹宏.基于FPGA的三相高精度工频信号源的设计与实现[D].杭州:杭州电子科技大学.2012,5:11-42.

[6]张博,孙伟波,张轶鹏.数字合成式三相低频正弦波信号发生器的设计[J].自动化技术与应用.2013,24(4):80-86.

[7]童子权,李双力,任丽军,等.基于SOPC的三相信号源的研究[J].电子测量技术.2009,16(12):10-13.

[8]徐运武,周泽湘.基于FPGA_LPM多功能信号发生器设计[J].电子设计工程.2011,32(8):197-182.

[9]朱其新,李辉,杨辉,等.基于SOPC的三相信号发生器设计[J].自动化与仪表.2010,26(4):16-19.

[10]郑争兵,魏瑞,陈正涛.一种基于FPGA的高速数据通道的实验方法[J].实验室研究与探索.2012,19(12):78-81.

[11]应芳琴.基于FPGA的内部信号实时监测方法研究[J].中国现代教育装备.2011,17(1):70-71.

[12]左现刚,余周,侯志松,等.基于SPI总线的TLC5615在AVR单片机中的应用[J].河南科技学院学报(自然科学版).2011,15(8):94-97.

[13]王媛媛,刘树林,刘宁庄,等.基于FPGA的串行通信控制系统的设计[J].微型机与应用,2011,12(3):57-63.

Design and Realization of a FPGA-based 3-phase Sinusoidal Signal Generator

YAN Yong

(Department of Physical and ElectronicScience,Aba Teachers Junior College,Wenchuan Sichuan 623002,China)

Using Alter's Cyclone IIseries EP2C20Q240C8 as the core processor,this paper designs a 3-phase sinusoidal signal generator based on LPM_ROM.By reading and writing LPM_ROM sinusoidal data,QuartusⅡdevelopment platform completes comprehensive simulation configuration.SignalTapⅡembedded logic analyzer conducts real-time capture and display of the 3-phase sinusoidal signal and connects 10-bit serial D/A converter TLC5615 to perform the designated function.

EP2C20Q240C8;LPM_ROM;3-phase sinusoidalwave;SignalTapⅡ;TLC5615

10.3969/j·issn.1000-3886.2014.04.013

TP346

A

1000-3886(2014)04-0038-03

晏勇(1983-),男,四川郫县人,物理与电子科学系讲师,研究方向嵌入式系统。

定稿日期:2014-03-20

阿坝师范高等专科学校校级课题资助项目(ASB10-15),基于fpga和dds技术的变频三相交流电源研发