数字存储示波器采样信息处理系统的设计与实现

2014-07-12钟惠球林盛鑫丁福财

钟惠球 林盛鑫 丁福财

数字存储示波器采样信息处理系统的设计与实现

钟惠球1林盛鑫2丁福财3

(1.东莞理工学院 资产后勤管理处,广东东莞 523808;2.东莞理工学院 电子工程学院,广东东莞 523808;3.东莞理工学院 总务部,广东东莞 523106)

提出采用现场可编程逻辑器件(FPGA)来设计数字存储示波器的采样信息处理系统,大大提高了系统设计的灵活性,硬件功能像软件一样可通过编程来修改,可快速更改数据采样方法,修正采样错误,有效地提高数字存储示波器的采样效率和数据的可靠性。

数字存储示波器;可编程逻辑器件;锁相环;分频器;等效采样

随着大规模集成电路技术、信号分析与处理技术及嵌入式微处理器软硬件技术的迅速发展,现代电子测量技术与仪器领域也在不断探讨新的仪器结构和新的测试理论及方法[1]。数字存储示波器作为电子测量系统中应用最为普遍的电子测量仪器之一。国外智能化数字电子测量仪发展迅速,正逐步取代采用大量分立组件和集成块,电路复杂,体积庞大,操作繁的传统电子测量仪器,正以高频率、高带宽、高智能和高集成方向发展。而目前国内数字示波器技术发展与国外相比,仍存在很大的距离,在生产和研究中使用的高端电子测量仪器还基本上靠进口,而且价格昂贵。数字存储示波器集A/D技术、ASIC技术、FPGA技术、ARM技术,LCD显示技术于一体[2],具有极高的技术含量、很强的实用性和巨大的市场潜力。这对我国电子测量仪器的设计理论和方法提出了新的挑战,促使我们在引进、消化、吸收国外新型电子测量仪的基础上,尽快推出具有自主知识产权的智能化数字电子测量仪。

1 数字存储示波器采样信息处理系统的总体设计

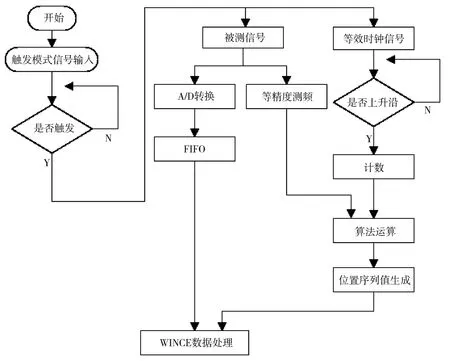

数字存储示波采用双处理器(ARM+FPGA)的嵌入式系统设计[2]方案,ARM内嵌WINCE操作系统,采样信息处理系统主要在FPGA里完成。如图1所示:

图1 采样信息处理系统功能模块图

本设计采用了硬件描述语言(VHDL),通过从上层到下层逐层描述的设计模式,在FPGA里实现了采样信息处理系统功能,把采样信息处理系统主要分为PLL锁相环功能模块、分频器功能模块、FIFO功能模块、等效采样功能模块、芯片驱动功能模块[3]和ARM接口通信控制模块,这些模块都是通过VHDL代码实现的,并非真实存在这些模块芯片,而是由FPGA通过VHDL语言对硬件进行描述例化而成。每个模块的实现都必须了解其模块对应的硬件的功能与原理[3]。

由图1可知FPGA的各模块之间的关系,图2为采样信息处理系统具体数据采样流程图。

图2 采样信息处理系统数据采样流程图

2 数字存储示波器采样信息处理系统的主要模块设计

2.1 ARM接口通信控制模块设计

ARM接口通信控制模块为主要的控制模块,主要有两个作用:

1)减少ARM接口的占用。由于ARM作为主控芯片的控制模块,引脚数量有限。如果ARM接口直接与FPGA接口相连,会占用ARM过多的接口。

2)减少ARM和FPGA相连的信号线存在各种干扰,由于有时会出现毛刺现象,会影响测量效果,降低了测量的稳定准确。

2.2 PLL模块设计

PLL是一种反馈环路[4],主要组成包括相位相位频率检测器(PFD)、电葆泵(CP)、环路滤波器(LF),压控振荡器(VCO)和反馈计数器M。主要作用就是把内部/外部时钟的相位和频率同步于输入参考时钟,共同完成相位调整。PLL锁相环技术在FPGA中的应用,其实就是一个时钟合成器,采用过Quartus II的MegaWizard外挂插件管理器实现PLL的设计。

2.3 FIFO模块设计

FIFO是RAM的一种,通过Quartus II的LPM/MegaFunction宏功能模块库,同时采用MegaWizard外挂插件管理器实现FIFO的设计。首先选择FIFO的深度,这里选择8位。接着选择触发方式,然后选择读时钟与写时钟等等,使用MegaWizard外挂插件管理器可以完成,在这里不再赘述。最后生成FIFO的例化元件。

2.4 分频器功能模块设计

分频器功能模块,实际是一个时钟分配器,因为PLL输出有限,且占用较多的系统资源,分频器对从PLL输出的时钟进行再次倍频和分频处理,分频器比较灵活,可以通过编程,设计各种各样的频率。每个功能模块都需要时钟作为时序驱动,此模块比较重要,时序错误,将影响整个模块的稳定性与准确性。本课题需要设计一个可设预置数的分配器,主要的功能是当输入端输入给定的不同数据时,将对输入的时钟信号有不同的分频比,由计数值可并行预置的加法计数器设计而成[5]。如图3所示。

端口说明:

CLK为时钟输入端,由PLL与一个输出端作为分频器的时钟上。其时钟值为1 GHz。

CLR为复位信号,让计算器重新计数。

D[19..0]为预置值输入端,是一个20位的预置值,因最小输出值设为1 KHz,通过计算从1 GHz分频为1 KHz,需要220,即20位。

FOUT为输出端,输出其预置值对应的需求输出值。

2.5 等效采样功能模块设计

等效采样功能模块包括被测信号与等效时钟信号处理两部分[6]。前者用来计数被测信号的频率,后者用于完成计算等效采样频率以及计算采样点数,再参与等效采样的采样点序列排序算法运算。

图3 分频器功能模块例化组件

3 数字存储示波器采样信息处理系统的实验结果分析

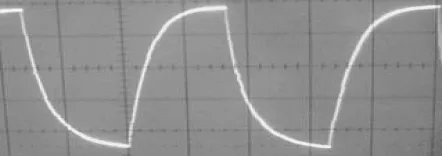

通过等效采样功能模块与FIFO功能模块分别得到采样点的电压值与采样点的序列值,把数据传送到ARM,由WINCE进行进一步的处理,图4为被测信号在示波器上的波形,直接连接示器观看。记下波形,目的是为了与通过采样信息处理系统后重现被测信号波形作比较。

图4 被测信号波形图

图5 被测信号重现波形图

图5 为该采样信息处理系统对被测信号进行等效采样后得到的波形重现,与图4作比较可知,与被测信号仍存在着一定差异,经过分析,需要加入排除毛刺和随机干扰信号,一般通过两种方法来进行,第一种方法是延时技术,主要在信号上设置微量的延时,或延时采样,使处理过的信号在输出能避开毛刺,一般的操作是通过使用时序组件来实现延时的目的,另一种方法就是增加一个信号滤波器,把毛刺和随机干扰信号滤掉,主要的方法是增加D触发器,当多个D触发器的输出都为1时才确定为真正的触发,有效排除了非真实信号触发的可能性,如图6所示。

图6 被测信号重现波形图(增加D触发器)

4 结语

通过使用VHDL语言,使用QuartusII为FPGA的集成开发平台,根据FPGA与VHDL的开发流程,详细给出了各个功能模块的实现过程。完成在FPGA可编程器件上实现数字存储示波器的采样信息处理系统,还需增加更多的模块来完善系统的不细致的部分。

[1] 杜吉伟.示波器的技术和市场发展[J].电子质量,2008(4):40-42.

[2] 李仪,潘佑华.基于FPGA和ARM的数字存储示波器控制系统的设计[J].计算机测量与控制,2010,18(3):575-579.

[3] 林盛鑫,钟惠球,黄丁香.基于FPGA的数字存储示波器对外围芯片的控制设计[J].东莞理工学院学报,2013,10(20):20-26.

[4] 邵帅,李曼义,刘丹非,等.全数字锁相环及其数控振荡的FPGA设计[J].现代电子技术,2008,10(273):1-6.

[5] 贾米娜.一种基于FPGA的分频器实现[J].机械管理开发,2006(1):100-102.

[6] 任斌,余成,陈卫,等.基于EDA技术的等效采样的设计实现[J].微计算机信息,2007,23(52):293-295

Design and Implementation of SamplingInformation Processing System in DSO

ZHONG Hui-qiu1LIN Sheng-x in2DING Fu-cai3

(1.Logistics and Management Division,Dongguan University of Technology,Dongguan 523808,China;2.College of Electronic Engineering,Dongguan University of Technology,Dongguan 523808,China;3.General Affairs Department,Dongguan University of Technology,Dongguan 523106,China)

This thesis makes use of field programmable logic device(FPGA)to design a sampling digital storage oscilloscope Information Processing module,greatly improving the flexibility of system design.Hardware functions can be changed as software can be programmed.Moreover,you can ruickly change the data sampling methods and correct sampling errors in order to increase the sampling efficiency of digital storage oscilloscope and data reliability.

FPGA;Phase-Locked Loop;divider;eruivalent sampling

TN77

A

1009—0312(2014)03—0017—04

2014-06-03

钟惠球(1980—),男,广东东莞人,工程师,主要从事软件工程研究。