多通道数字接收机采集测试系统设计与实现

2014-06-07严济鸿何子述

侯 硕,严济鸿,何子述

(电子科技大学电子工程学院,成都 611731)

多通道数字接收机采集测试系统设计与实现

侯 硕,严济鸿,何子述

(电子科技大学电子工程学院,成都 611731)

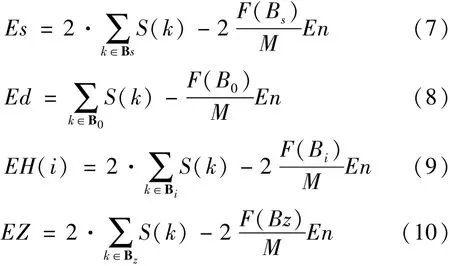

为了对某雷达接收机的采样信号进行指标测试,设计并实现了一种光接口数据采集测试系统。该系统硬件部分以FPGA为核心完成光接口对8路中频采样模块16位数据的接收,并配备大容量DDR2对数据进行实时存储,以cPCI芯片CY7C09449PV作为数据采集板与上位机的接口,由计算机应用程序进行控制,将采集到的数据传回计算机中进行时域、频域波形显示,以及ADC动态参数、通道参数的计算。经过测试,系统成功实现同时对8通道数据进行接收并且对其中任意4通道数据进行频谱的绘制以及进行指标计算。

FPGA;光接口;ADC动态参数;通道参数

0 引 言

雷达测试设备的发展源自20世纪50年代开始,随着计算机技术的发展,雷达测试技术进入了自动测试阶段,在随后的几十年,美军致力于测试技术标准化的研究,建立起模块化的软硬件测试平台,根据用户的不同需求,灵活快速的组建成相应的测试系统,提高了测试系统的制造速度和性价比。

进入21世纪之后,随着数模转换器(ADC)器件的快速发展,数字阵列雷达以及雷达测试系统也进入了一个新的阶段[1],国外多家公司都推出了多款高性能数模转换器件和高速信号采集模块,在采样频率超过1 Gs/s的情况下,许多ADC芯片通常能够达到10 bits或者12 bits。目前数字阵列雷达发展到了工业应用的阶段,数字波束形成的重要前提就是需要有高水平的多通道数字接收机[2],这样才能够保证回波在进入天线后能够减小失真;采用了数字波束形成技术之后,对接收机通道间的信号一致性和无杂散动态范围的要求又进一步提高,随着cPCI总线的发展,雷达测试系统的通用性得到了极大地提高。

数字接收机作为数字阵列雷达的重要组成部分,其性能指标特别是ADC性能和通道性能对雷达的整体性能有很大的影响。ADC是连接模拟信号和数字信号之间的桥梁。ADC的研究核心是不断提升其采样速度和转换精度,同时,抑制ADC的非线性也是研究的关键。数字接收机中ADC电路性能的测试及通道幅相一致性的测量也十分重要[3]。

为了满足对ADC电路性能的测试及通道幅相一致性的性能测量要求,提出了一种数据采集测试系统[4]。从系统的结构设计出发,给出了系统和软件的设计方案,并且做了实际系统的数据采集进而进行测试分析。与传统的雷达测试仪器不同[5],这种基于计算机软件的虚拟仪器,系统的整个测试工作都在计算机中完成,可以降低测试系统的更新、维护成本,避免记录测试数据时的人为误差。

1 测试系统方案

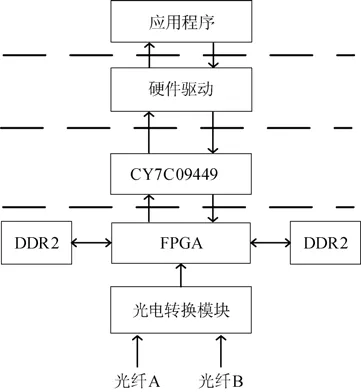

硬件系统采用4个光接口输入(2个单模,2个多模)原始数据,同时连接2个单模或2个多模,通过FPGA进行数据的转移及命令的控制,并且使用2个2G的DDR2进行数据在硬件部分的缓存[2]。由cPCI芯片CY7C09449PV作为硬件板卡与上位机连接的接口芯片负责上位机与硬件板卡的指令以及数据的交互。硬件部分系统结构如图1所示。

整个系统由计算机软件控制,当计算机发送采集命令后,FPGA接收来自光模块的数据然后存入DDR2中,当接收到的信号长度满足命令的需求时再由DDR2读出通过PCI总线发回计算机中进行保存和显示,随后系统进入待机状态等待下一个命令。

图1 系统示意图

2 测试方案设计

2.1 ADC动态参数及其测试方案[7]

2.1.1 ADC动态参数

测试系统中需要测试的指标包括ADC动态参数中所关心的信噪比(SNR)、信纳比(SINAD,signalto-noise and distortion ratio)、有效位数(ENOB,effective number of bits)和平均噪声电平(ANL,average noise level),除此之外本文还会介绍总谐波失真THD(Total Harmonic Distortion)、无杂散动态范围SFDR(Spurious Free Dynamic Rang)等参数。对于动态参数的具体定义以及计算公式,由于篇幅问题就不在一一陈述,详见参考文献[7]。

2.1.2 ADC动态参数测试方案[8]

对于ADC动态指标的测试,采用频谱分析的方法,为了测得更加准确的动态指标,测试条件是输入信号为接近满幅的正弦信号,在频谱分析的方法中,首先需要对信号经过加窗处理后再进行FFT变换。

汉宁窗(Hanning)能够很好的抑制频谱泄漏,具有良好的频率分辨率,在大多数情况下汉宁窗能够取得很好的效果,所以对讨论的FFT变换前均加汉宁窗进行处理。

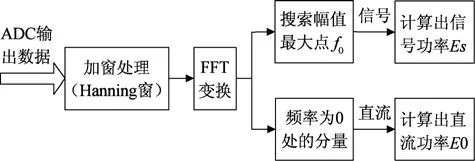

由前文各参数指标定义及其计算式可以知道,要通过对信号的频谱分析得出ADC动态指标参数需要将频谱中的信号分量、直流分量、谐波分量、杂波和噪声分量的功率计算出来,分离信号和直流方法如图2所示。

图2 信号和直流功率计算流程

假设Bs为计算信号功率所需谱线集合,B0为计算直流功率所需谱线的集合,X(k)为输入信号的FFT变换,M为FFT点数,则直流功率可以表示为式(1),信号功率可以表示为式(2)。

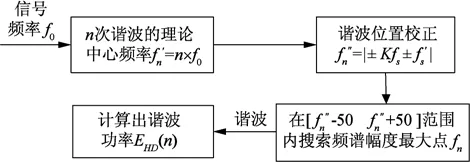

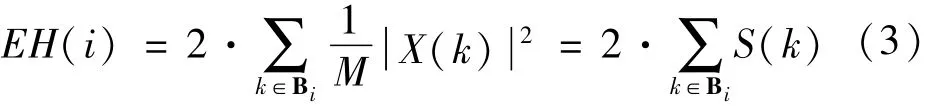

在确定信号谱线后可以得出信号频率为f0,由此可以大致确定第n次谐波的频率为fn=n×f0,其中n为整数,当谐波位置大于半采样率即fn>时(fs为采样率),会发生谐波频谱的折叠,此时谐波的频率为fn′=|±mfs±fn|,m为整数;因此,要对谐波频谱的位置进行校准得到谐波的中心频率,但由于经过了多次的计算,校准出的频率值不一定准确,即处频谱不一定是幅值最大点,因此,需要在周围的较小范围内搜索峰值作为实际的谐波,一般搜索位置的左右各50根谱线即可准确找到谐波位置,谐波分离策略如图3所示,设Bi是以上述的方法确定出的第i次谐波的所有谱线的集合,则可以通过式(3)计算谐波能量。

图3 谐波分离流程

去除信号、直流、谐波后的频谱可以看成杂波和噪声的和,其中幅值最大值点可以看成杂波,杂波个数N可以由用户自己设定,这N个谱线的功率就是杂波功率,而余下的功率可以看做噪声功率,按照上述方法提取出的杂波谱线的集合,为噪声谱线的集合,则杂波功率可如式(4)计算,假设噪声是白噪声,在信号、直流、谐波、杂波谱线集合中也是存在噪声,所以在计算噪声功率时要考虑这个因素,将这些谱线集合中的噪声去除,记F(B)表示集合中所包含的谱线数量,则噪声功率为式(6);噪声和杂波的功率计算方式如图4所示。

图4 噪声和杂波功率计算流程

在考虑到信号、直流、谐波、杂波谱线中的噪声后,为了更加准确的计算功率,需要对式(1)~式(4)进行修改得到测试系统中使用的计算公式,为

2.2 通道参数及测试方案

2.2.1 通道参数[9]

2.2.1.1 通道幅相一致性误差

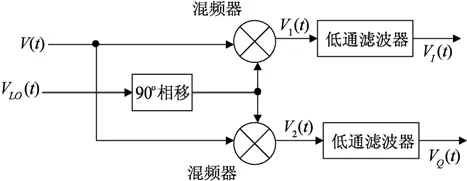

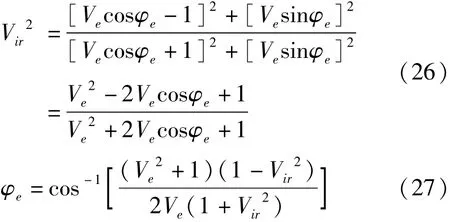

通道参数主要是由于接收机中数字下变频处理产生的,中频信号V(t)与本振信号VLO(t)正交混频将信号分成正交的I/Q两路基带信号 VI(t)和VQ(t),原理框图如图5所示。

图5 正交下变频原理框图

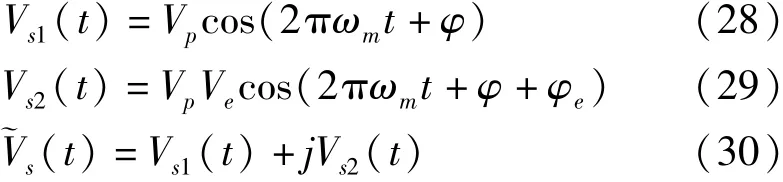

假设Vp、ωRF、φ分别表示为输入信号的幅度、频率和初始相位,那么输入信号的表达式可以写成式(11)的形式,本振信号为VLO(t)=Cos(ωLOt),I通道中混频产生的信号可以写成式(12)的形式,混频后的信号经过低通滤波后只保留了低频信号,最终I路输出可以写成式(13)的形式,其中ωm=ωRF-ωLO为调制频率,描述的是信号输入频率和信号本振频率的差值。

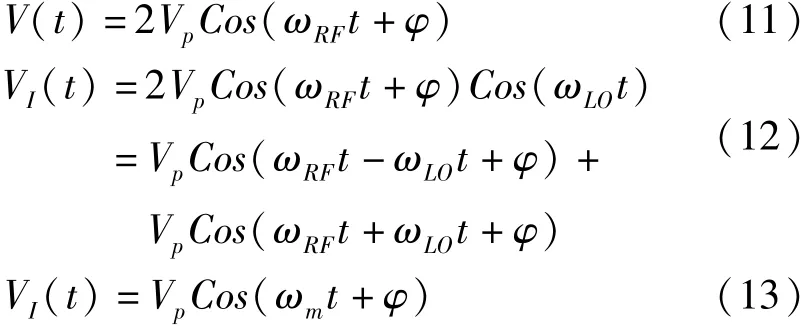

把两通道信号直流差异记成VDC,两通道的幅度一致性误差记成Ve用于表示两路信号的幅度比,把相位一致性误差记成φe用于表示两通道间相位的差异与90°的差值,把输入信号经过混频后产生的Q通道信号写成式(14)形式,式(14)中的Ve和φe可以表示成式(15)和式(16)的形式,再将Q路信号经过低通滤波,滤去其中的高频部分,保留式(17)中所示的低频部分。

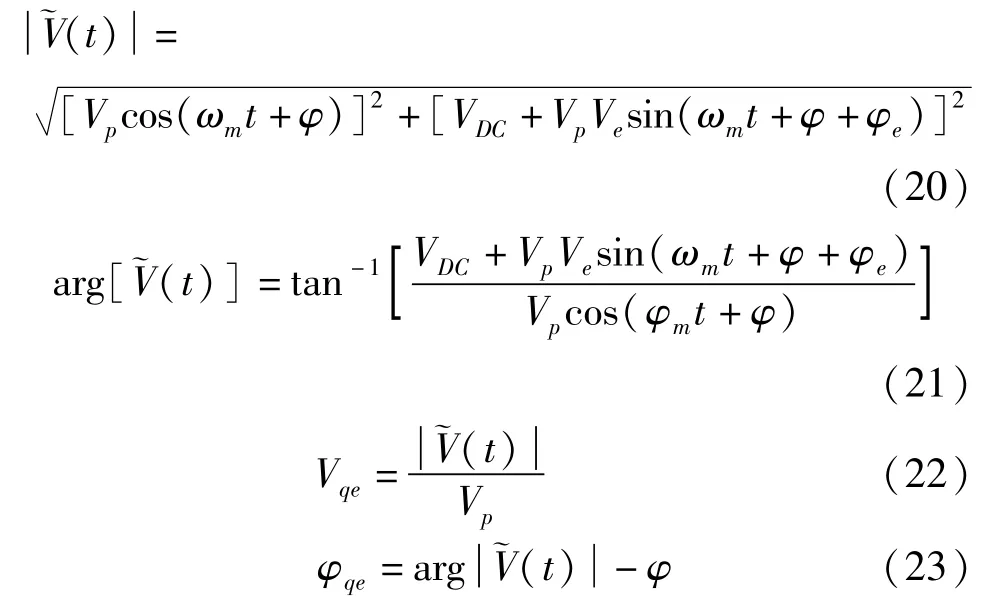

通常将输出的I/Q信号要合成一个复数信号来进行处理,合成的公式如(18),将式(13)和式(17)带入式(18),可得式(19),对于复解调器输出信号看来,理想情况下,此复信号的幅度应为Vp,相位值为ωmt+φ,但从式(19)可以看出实际情况并非如此,输出复数信号的幅度可以写成式(20)的形式,而将信号的虚部与实部之比用反正切计算,得到如式(21)实际信号的相位值与时间的关系式,最后可以得到如式(22)所示的实际复正交解调器输出信号的幅度误差Vqe和如式(23)所示的相位误差φqe。

2.2.1.2 镜像抑制比

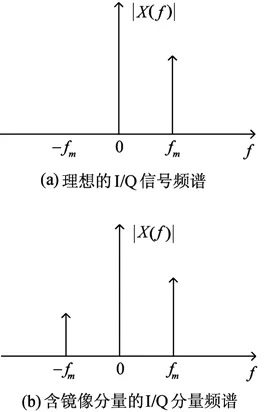

镜像抑制特性是指对一个理想的复正弦信号做正交解调,镜像抑制比示意图如图6所示。将信号的I分量作为复数的实部,Q分量作为复数的虚部,对复数信号做FFT后在频谱中只在信号频率fm处出现一个峰,如图6(a)所示,而工程中DDC无法产生理想的两路信号,对输出信号做复数FFT,频谱上除了fm处的峰外,位于-fm处也就是位于fm相对于零频镜像对称处还存在一个峰,就是信号的镜像分量,如图6(b)所示,镜像信号的产生是由于复正弦信号的实部(I路信号)和虚部(Q路信号)之间存在幅相不一致性,镜像抑制比就是-fm处的镜像分量和fm处的信号量幅度之比,通常用对数表示,对于正交解调器,镜像抑制比是一个重要的指标,复信号频谱镜像抑制比越低,下变频的效果越好。

图6 镜像抑制比示意图

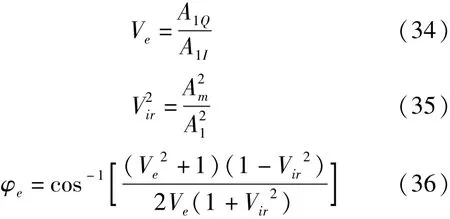

2.2.2 通道参数的测试方案

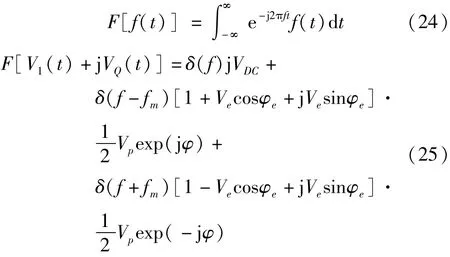

从式(30)、(31)可以看出,正交解调器的幅度误差Vqe和相位误差φqe是受正交解调器两路之间的幅度一致性误差Ve和相位一致性误差φe影响的,因此很难将Ve项和φe项从幅度误差Vqe和相位误差φqe中剥离出来。这里将利用镜像抑制比把相位一致性误差和幅度一致性误差对解调器的影响提取出来。以下将推导出相位一致性误差、幅度一致性误差和镜像抑制比间的关系。首先要将复时域信号转换到频域上,傅里叶变换写成式(24),将式(19)代入式(24),对复数信号作傅里叶变换,简化后得式(25)。

由式(25)可以看出,如果I/Q两路间的幅度一致性误差和相位正交误差不存在,即Ve=1,φe=0那么镜频分量也将不存在,由此可见,幅度一致性误差和相位正交误差的存在导致了镜频分量的产生,取信号的镜频分量的幅度与正频率分量的幅度之比,就是 I/Q解调器镜像抑制比 Vir,由此得出式(26),对式(26)进一步变换,得出镜像抑制比和相位幅度一致性误差、正交相位误差之间的关系如式(27)。

因此只要从信号的频谱计算出Ve和Vir,便可使用式(27)得出正交相位误差φe,以上内容主要针对同一通道中的I/Q两路正交信号的镜像抑制比、相位一致性、幅度一致性误差的计算,本测试系统中不仅要测试通道内的正交两路信号的指标,还需要测试两通道间信号幅相一致性误差和镜像抑制比的指标,后面将对这部分内容进行讨论。对于不同通道间一致性的测量,可以当成存在幅度和相位误差的两个同相而非正交信号,一般可以同时取两通道的I路或者Q路信号进行计算,将这两路信号合成一个复数信号,信号的具体形式如式(28)~式(30)。

同样的,需要将时域信号转化到频域上处理,对˜Vs(t)作傅里叶变换后得到式(31),用正频率分量的幅度比上镜频分量可以得到式(32)所示频谱的镜像抑制比,由此推算出的相位误差公式为(33),分别对两路信号进行频谱分析得出它的正频率幅度之比,用这两个变量就可以计算出两个通道中的I/Q信号之间的相位差。

最后,以I/Q通道内参数为例总结一下实际测试数字I/Q复解调电路的通道性能的步骤:首先将一个单频的正弦波信号输入数字I/Q复解调系统,把输出的I/Q两路信号保存下来,分别对两路信号做频谱分析,分别找出I/Q两路信号的最大峰值(信号频率分量)的幅度A1I和A1Q,这样,幅度一致性误差为式(34)所示,然后再把两路I/Q信号合成一路复数信号,对这个合成的复信号进行频谱分析,在这个复数频谱中找出最大信号峰值A1和镜像峰值A1m,得到镜像抑制比为式(35),最后根据式(36),由镜像抑制比Vir和幅度一致性误差Ve计算出如式(3-44)的I/Q两路的相位误差:

3 测试结果及分析

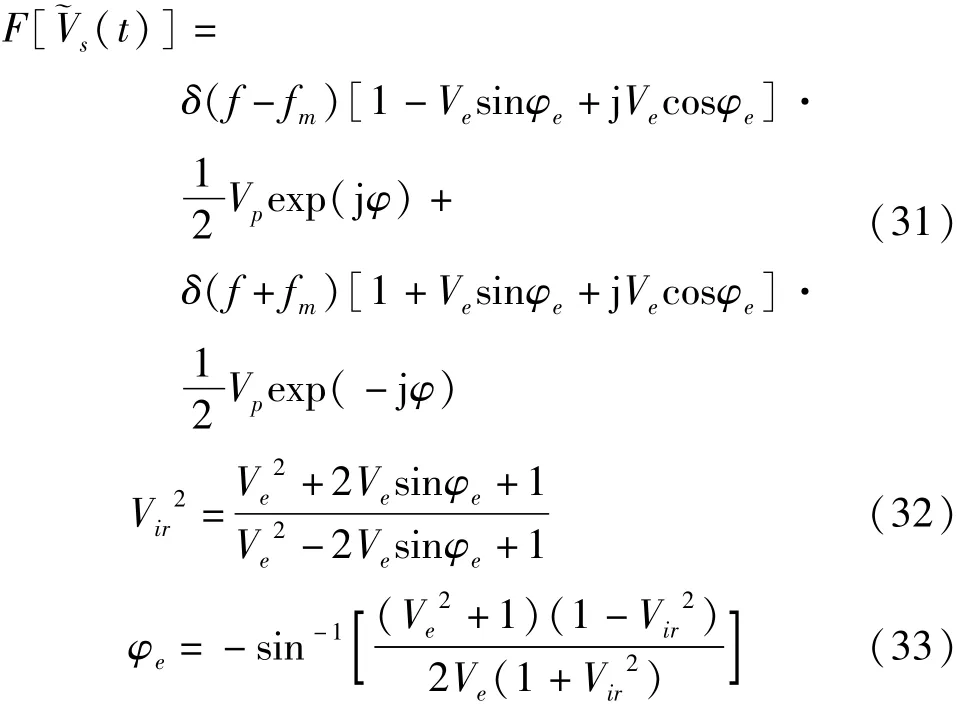

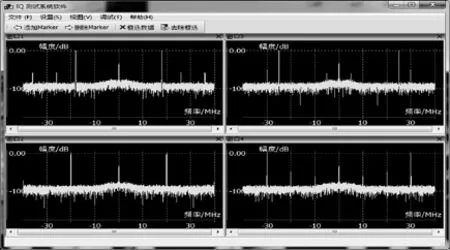

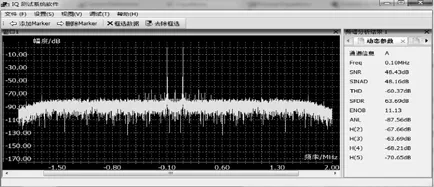

信号源产生四种中心频率分别为16 MHz、20 MHz、25 MHz、30 MHz的正弦信号,在80 MHz的采样率下采集该信号,打入一根光纤传输至上位机,缓冲区长度设置为64K,数据传至上位机绘制以半采样率为中心的频谱,如图7所示。

图7 80M采样率下采集16202530 MHz四通道信号的频谱

从频谱以及右边的参数显示中可以看出该系统能够正确显示有效信号的频率并准确的寻找到2~5次谐波。由于测试使用的信号源会产生高次谐波,采样后这些高次谐波向下搬移由此会产生一些尖峰,但这些谐波尖峰远远小于信号中心频率处的尖峰,不会影响对信号中心频率的识别。

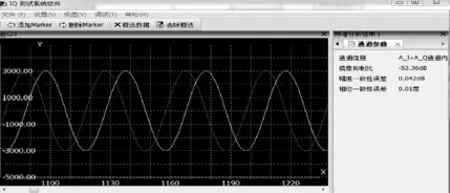

信号源产生28.1 MHz信号,在4 MHz采样率下采集信号并经过下变频处理后产生中心频率为0.1 MHz的I、Q正交信号如图8所示为上述信号的频谱;上述信号的时域波形,如图9所示。

图8 4M采样率下采集0.1M正弦信号所绘制的频谱

图9 I、Q两路正交信号时域波形

从图9中可以看出系统正确传输了经过正交化后产生的正交信号并精确计算出相位一致性误差等参数。

4 结 语

从测试结果可以看出基于cPCI的系统构架可以很好的实现高速采集,上位机中使用wxWidgets以及FFTW库函数可以精确分析信号参数。但是由于计算机硬件运算速度的限制,虽然采集系统的硬件平台可以完美的实现高速采集和传输,但是计算机无法实现持续大数据量的高速计算。当今计算机技术高速发展,相信在不久的将来,随着CPU运算速度的不断提高,实现对大数据量数据进行快速的频谱分析和运算不是难事。

[1]吴曼青.数字阵列雷达及其进展[J].中国电子科技研究院学报,2006,1(1):11-16.

[2]张奕,余海龙,谭剑关.四通道高速数据采集系统设计[J].现代电子技术,2012,35(9):10-12.

[3]杜俊蛟,曹旭东,李宝森,等.FPGA的多通道雷达接收机幅相不一致校正[J].电光与控制,2011,18(1):85-89.

[4]王永东.雷达接收机自动测试系统的研制[D].南京:南京理工大学,2008,2-3.

[5]朱祖德.多种雷达接收机的特点分析[J].现代雷达,2010,32(10):84-86.

[6]戴澜,姜岩峰,刘文楷.基于Matlab的高速高精度ADC测试研究[J].计算机测量与控制,2010,18(9):2044-2049.

[7]HOFNER TC.Defining and testing Dynamic ADCParameters[J].Microwaves RF,2000:75-84.

[8]陈祝明.软件无线电技术基础[M].北京:高等教育出版社,2007,17-22.

侯 硕(1990—),山东郓城人,电子科技大学硕士研究生,主要研究方向为信号与信息处理;

E-mail:houshuokaka@163.com

何子述(1962—),四川新都人,教授/博士生导师,主要从事阵列信号处理、智能天线、相控阵雷达等方面的研究工作。

Design and Implement of Acquisition AndTest System for Multi-Channel Digital Receiver

HOU Shuo,YAN Ji-hong,HE Zi-shu

(School of Electronic Engineering,University of Electronic Science and Technology of China,Chengdu 611731,China)

An optical-interface-based data acquisition and testing system is designed tomeet the requirements of a radar experiment platform.FPGA is the core to receive 16-bit data in 8-channel IF sampling module with optical interface,and the system is equipped with large-capacity DDR2 data real-time storage.The cPCI chip CY7C09449PV is the interface of data acquisition board and the host computer,controlled by a computer application pass collected data back to the computer to achieve time domain,frequency domain waveform display,the calculation of ADC dynamic parameters and the channel parameters.Experimental results demonstrate that the system can receive the 8-channel data simultaneously and can finish spectrum drawing parameter calculation for 4-channel data.

FPGA;optical interface;ADC dynamic parameters;channel parameters

TN79;TN957.51

A

1673-5692(2014)03-281-06

10.3969/j.issn.1673-5692.2014.03.011

2014-04-26

2014-05-13