高速信号过孔对信号影响因素研究

2014-05-31胡新星华炎生

余 凯 胡新星 刘 丰 华炎生

(珠海方正印刷电路板发展有限公司,广东 珠海 519100)

高速信号过孔对信号影响因素研究

余 凯 胡新星 刘 丰 华炎生

(珠海方正印刷电路板发展有限公司,广东 珠海 519100)

影响信号完整性的因素有很多,其中过孔结构对信号影响越来越明显,如何进行有效的过孔设计从而使过孔阻抗与激励源阻抗配从而达到信号完整性已经成为当今PCB设计业界中的一个热门课题。文章通过Ansys公司的HFSS仿真软件,利用仿真方法分析不同信号过孔结构对高速信号的影响,并对过孔残桩长度(stub),反焊盘,焊盘的不同大小对信号差损影响程度做了进一步研究。

高速印制电路板;信号完整性;焊盘;反焊盘;短桩;正交实验设计(DOE)

1 介绍

1.1 过孔简介

多层PCB板上的信号过孔(Via)主要的功能是用做各层之间的电气连接,过孔的结构主要由焊盘,反焊盘,钻孔孔径,三部分组成。过孔的生产在钻孔后的PCB板上进行沉铜,电镀,使孔的内壁镀上一层金属,这样过孔就具备的导通功能。在高速产品中,过孔不仅仅具有电气连接性,如果高速信号经过此过孔时,由于信号源阻抗和过孔阻抗不匹配,这将会造成信号发生反射,当信号速率增大会产生抖动,进而造成产品可靠性降低甚至报废。如果信号孔阻抗设计的不合理,通常不经过优化的过孔阻抗,其阻值约为25 Ω ~ 35 Ω,因此信号完整性工程师在设计电路时会对过孔进行优化,同时设计各类型过孔来提高过孔的信号完整性。

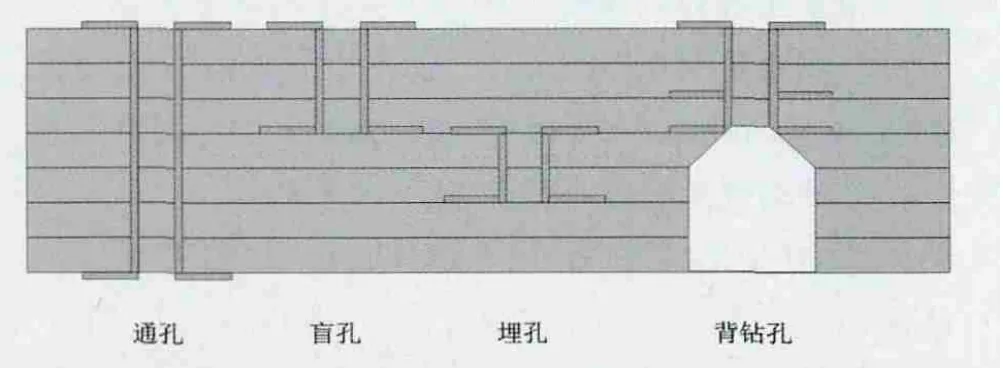

图1的孔类型为:通孔、盲孔、埋孔,以及背钻孔。通孔为钻穿这个线路板的孔,盲孔为PCB的顶层和底层与内层电气连接,埋孔在PCB的内层作为内层的电气相连。背钻孔是将一个电镀通孔在电镀后,用深度控制钻孔的方法把这个孔再钻一次,钻到要求的深度,为的是在高速信号中将过孔对信号的反射去除。

图1 常见过孔结构

1.2 过孔的特性

过孔在过高速信号时,其存在着寄生电容和寄生电感,若过孔焊盘的直径为D1,其反焊盘的大小为D2,板厚为T,板材的介电常数为,则过孔寄生电容为:

由于过孔存在着寄生电容,会造成信号上升时间延长,传播速度减慢,因此较小的寄生电容对信号完整性有较大的贡献。过孔除了寄生电容的效应也存在着电感性,寄生电感值近似公式为:

T为过孔的长度,d为钻孔的直径,寄生电感的危害通常较大,寄生电感的存在会对旁路电容有所消弱,进而使整个电源系统的滤波作用降低。

2 研究方案

本次研究高速信号过孔对信号影响因素主要通过仿真的方法来讨论过孔结构中的焊盘,反焊盘,背钻柱桩(Stub)三种参数变化对信号损耗的影响,及哪种因素是主要影响因子。本方案采用一个八层板作为研究对象,所用材料为台光的EM888材料,具体叠构如图2。

图2 叠构图

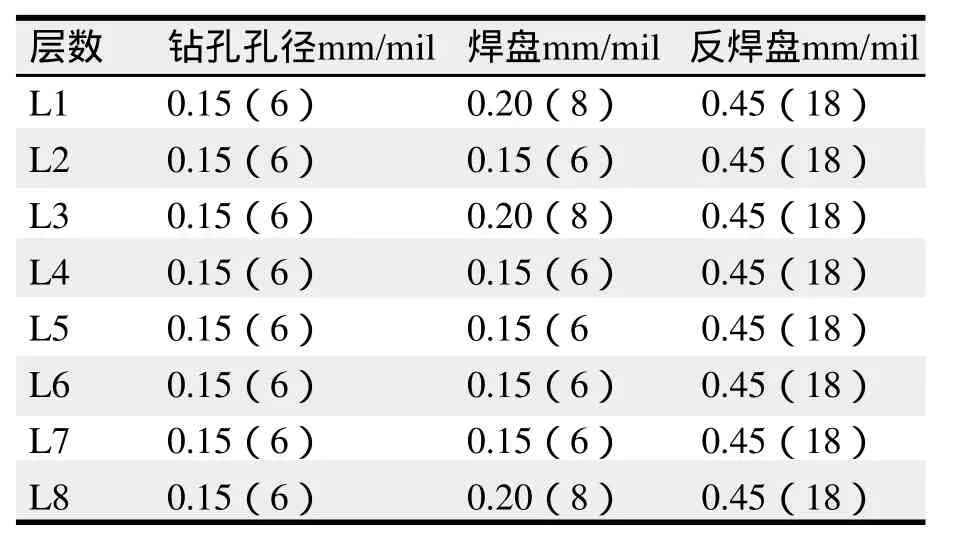

由图2可知,L1、L3、L6、L8为信号层,其余为参考层,背钻孔的设计为钻穿L4层不钻通L3层,通孔的信号走向为L1层进入信号,L8层出信号。若做了背钻处理则,信号为第一层进入,第三层出。信号源端阻抗设定为50 Ω,由于要研究不同参数对信号损耗的影响需要有一个标准的孔结构作为仿真基础,所谓标准的孔结构是指其阻抗要保证和源阻抗的50 Ω接近,这样在此基础上修改其他参数得出的损耗结果才有可比性,因此,初始设计的过孔结构,如表1。

表1

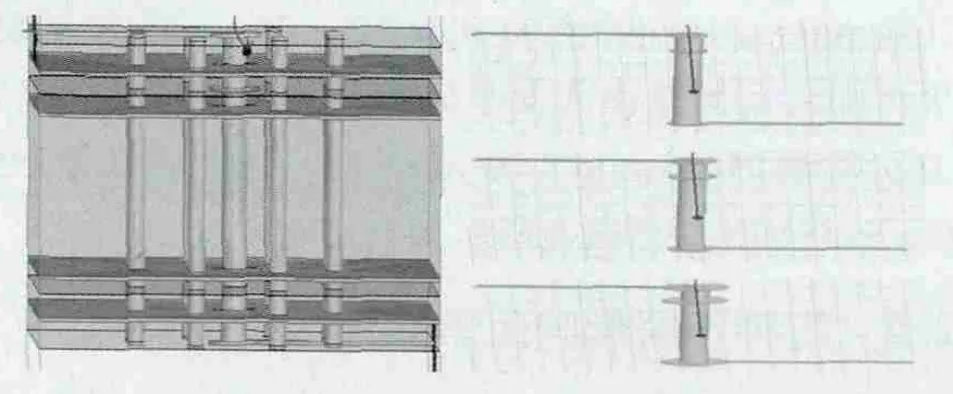

为仿真上述过孔结构的阻抗值,采用Ansys公司的HFSS,下图中间为信号孔,孔周围有八个接地孔,作为过孔信号回流路径,过孔的模型见图3。

图3 过孔模型

2.1 仿真分析

通过TDR仿真我们可以直观的看到,阻抗明显偏大,最高处达到58 Ω,和源端50 Ω阻抗不匹配,因此需要优化。这里主要通过优化其反焊盘(Antipad)大小来获得其标准阻值,图2中示例反焊盘的大小分别为0.3 mm(12 mil),0.4 mm(16 mil),0.5 mm(20 mil),为了获取准确的50 Ω阻抗值,我们可多选取不同的反焊盘大小来查看仿真结果。

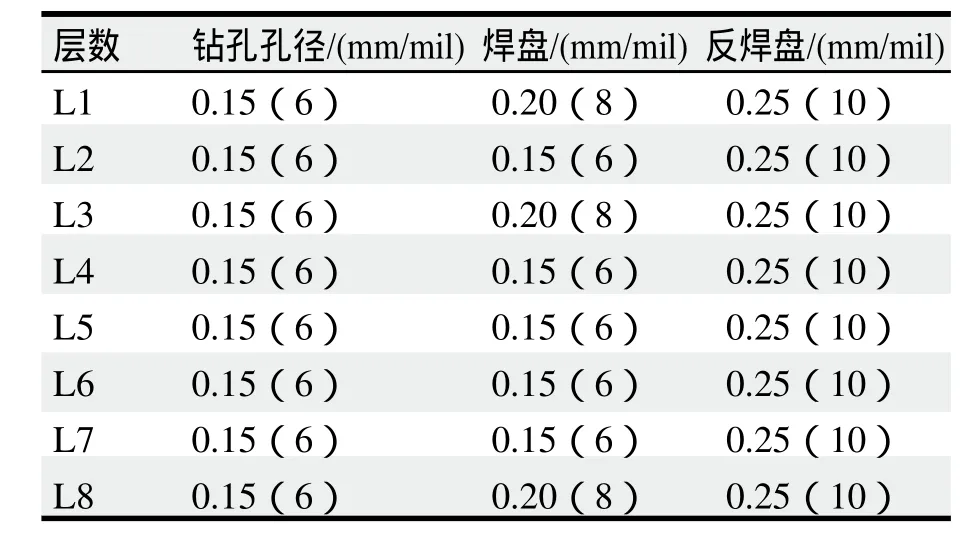

本次Antipad扫频大小从0.25 mm(10 mil)到0.6 mm(24 mil),步进位0.05 mm(2 mil),通过仿真结果可知,反焊盘由大变小时,过孔阻抗也会降低,当反焊盘位0.25 mm(10 mil)时,过孔阻抗接近50 Ω,最终优化后的过孔阻抗如表2。

2.2 三种不同影响因素探讨

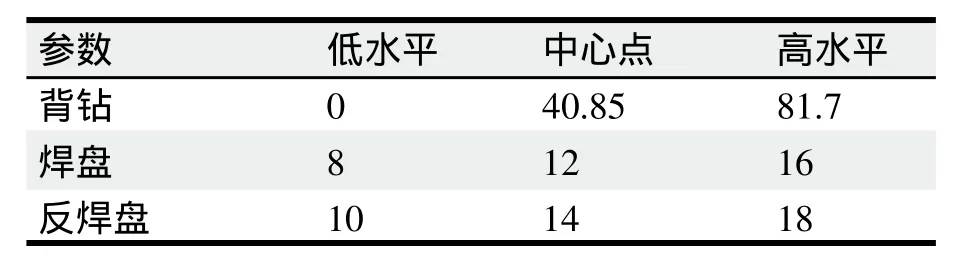

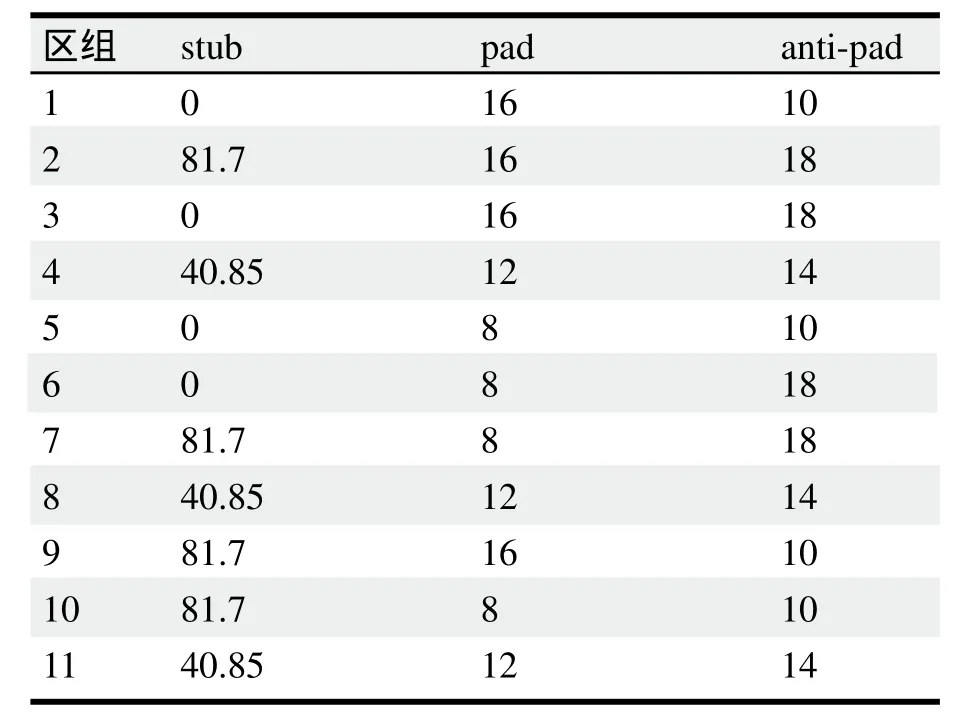

为了研究背钻,焊盘,反焊盘变化对信号影响程度,我们各选择三组不同的值作为实验因子,选取背钻,焊盘,反焊盘3因子,两个水平,加1中心点实验设计。设计表如表3。

表2

表3

正交实验表如表4。

表4

为获取上表中11组数据所对应的差损值,我们需通过建模仿真方法来模拟。

2.2.1 分析结果

三种不同影响因子(图4)仿真分析如下。

图4 三种影响因子

(1)焊盘大小对信号完整性影响

本研究方案为焊盘大小为0.20 mm(8 mil)到0.40 mm(16 mil),步进位0.05 mm(2 mil)。

从仿真结果可知,焊盘为0.20 mm(8 mil)时差损最小,随着焊盘的增大,信号损耗将增大,当焊盘在0.40 mm(16 mil)时 8 GHz的损耗比0.20 mm(8 mil)焊盘损耗大将近0.8 db。

(2)反焊盘大小对信号完整性影响

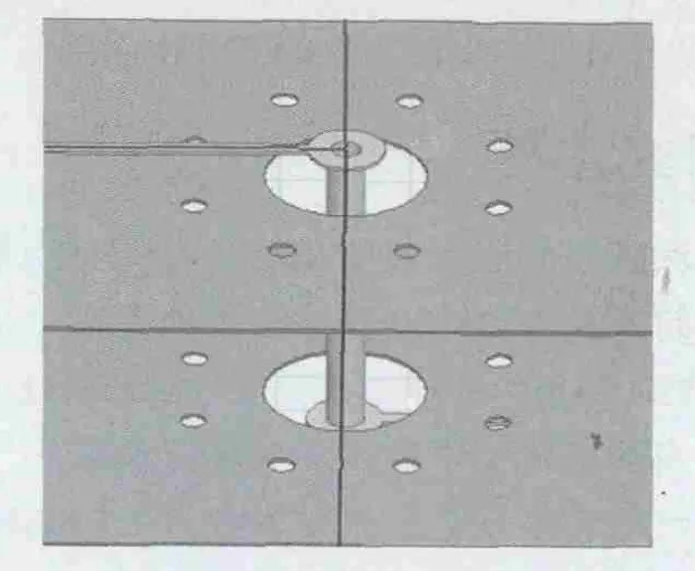

本次针对焊盘的变化范围对信号影响做定量的研究,通过模型建立出不同反焊盘长度对信号的影响信号从第一层进,第八层出(图5)。

图5 反焊盘进出

本研究方案为反焊盘大小为0.25 mm(10 mil)到0.45 mm(18 mil),步进位0.10 mm(4 mil)。从仿真结果可知,在5 Ghz之前反焊盘大小为0.25 mm(10 mil)比0.45 mm(18 mil)的反焊盘要小。

(3)背钻残桩大小对信号完整性影响

本次针对背钻stub的变化范围对信号影响做定量的研究,通过模型建立出不同背钻stub长度 信号从第一层进,第三层出。

本研究方案为背钻stub大小分别为0 mm(0mil),1.04 mm(40.85 mil)到2.07 mm(81.7 mil),从仿真结果可知,stub越长损耗越大,当stub=2.21 mm(87.1 mil)(不做背钻)时,信号插入损耗急剧变差,在11 GHz左右还发生了谐振。

通过以上的分析结果,可得出以下结论:

(1)4 GHz时三种因素影响分析

在4 Ghz时,stub对信号损耗贡献较大,占约69%;pad对信号损耗贡献次之,占约29%;anti-pad对信号贡献最小,约2%。

(2)8 GHz时三种因素影响分析

在8 GHz时,stub对信号损耗贡献较大,占约83%; pad对信号损耗贡献次之,占约13%;Anti-pad对信号贡献最小,约4%。

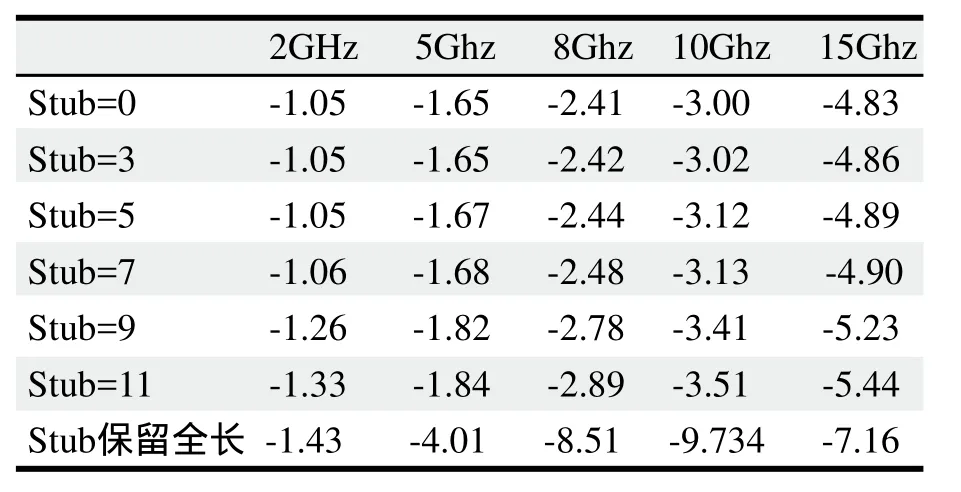

通过以上分析,当stub=0 mil,pad为0.20 mm(8 mil),antipad为0.279 mm(11 mil)时差损最小,但是在实际生产中背钻stub不能做到0 mil,因此需要再通过仿真来查看stub可接受的生产误差,我们选取stub长度分别为0到0.279 mm(11 mil)长度和保留总长进行仿真分析,可得具体数据如表5。

表5

由以上数据可知,stub长度保留在0.18 mm(7 mil)之内的时候,信号的损耗值几乎没变化,但是超过7 mil的时候损耗会急剧增大,因此只需保证背钻stub的公差在7 mil之内即可。

3 总结

高速信号在经过过孔传播时,过孔的结构对信

[1]Eric Bogatin. Signal Integrity:Simpli fi ed[M]. 北京:电子工业出版社, 2004.

[2]Ansoft Corporation,HFSS Full Book[R]. Ansoft Corporation, 2005.

[3]Laermans E,Geest J D,Zutter D D,et al,Modeling differential via holes[J].IEEE Trans.Advanced Pack aging,2001,24(3):357-363

[4]Martin Graham. PH.D. High-speed Digital Design,AHandbook of Black Magic. University of California at Berkeley.

[5]E.Laermans,J.De Geest,D.De Zutter,et al.Modelingdifferentialvia holes,IEEE ransactionson AdvancedPackaging, vol.24,no.3,pp357-363,2001.号不同频率起到不同的作用,每个影响因子对损耗的贡献度也不一样。

(1)在4 GHz时,对于过孔的结构,过孔stub长度对信号损耗的贡献度最大,其次是是焊盘,反焊盘贡献度最小。

(2)在8 GHz时,stub的长度是对信号损耗主要贡献,其次是pad大小,反焊盘贡献度最小。

由此可知,背钻stub是过孔结构中对信号损耗最大的因素,且随着频率的升高,过孔stub对信号的影响程度会随之增大,因此,在对信号过孔设计时要增加背钻步骤才能保证高速产品的可靠性。

Analysis of effects factors of high speed signal via on signal

YU Kai HU Xin-xing LIU Feng HUA Yan-sheng

Many factors can affect SI, and the via structure’s impact is more and more obvious. How to control the via impedance to match the excitation source’s impedance, thus, reduce SI problem. This is a new hot topic in PCB design. In this paper, the inf l uence of different via structure on high-speed signal is analyzed with simulation by ANSYS’s HFSS. Meanwhile we make further study on the inf l uence of remaining stub lengths, the size of anti-pad and pad on signal insertion loss prof i le.

High-speed PCB; Signal Integrity; Pad; Antipad; Stub; DOE

TN41 < class="emphasis_bold">文献标识码:A文章编号:

1009-0096(2014)06-0020-03