一种新型数字芯片测试仪的设计与实现

2014-05-25李天义耿跃华富坤张梅芳

李天义 耿跃华 富坤 张梅芳

(河北工业大学计算机科学与软件学院1,天津 300401;中国人民解放军93642部队2,河北 唐山 064000;河北工业大学电气与自动化学院3,天津 300401)

一种新型数字芯片测试仪的设计与实现

李天义1,2耿跃华3富坤1张梅芳1

(河北工业大学计算机科学与软件学院1,天津 300401;中国人民解放军93642部队2,河北 唐山 064000;河北工业大学电气与自动化学院3,天津 300401)

针对传统数字芯片测试设备检测芯片固定、PC机软件不可扩展、测试电路复杂等问题,设计了一种新型数字芯片测试仪。仪器设计为上位机和下位机两部分,并着重突出了上位机的作用。对组成上位机的编译模块、数据管理模块、SQLite数据库、测试模块和串口设置模块进行了研究,同时对以PL2303芯片为主的串口通信模块和以STC89C52为控制芯片的下位机电路进行了设计。系统能够准确地检测组合逻辑芯片、定位故障点,并能动态生成测试集、扩展可测组合逻辑芯片。

编译功能 SQLite数据库 芯片测试 测试集 结果集 故障检测

0 引言

随着电子技术的不断发展,组合逻辑芯片被广泛使用在数字系统研究中,因其反复使用、频繁插拔等,极易出现故障。为及时检测出问题芯片、提高芯片利用率,各大高校和实验室纷纷推出自己的芯片测试仪器或设备[1-5]。这些测试仪器在一定程度上实现了对问题芯片进行检测的目的。然而,这些测试仪器注重对芯片测试能力的设计,对适用范围、交互能力没有进行充分的考虑,主要体现在3个方面:一是将被测芯片的测试集提前写入检测系统中,导致被测芯片型号固定;二是忽略了上位机软件的扩展开发,使得测试系统不能够扩充被测芯片;三是通过拨码开关来对芯片类型和型号进行选择,增加了硬件电路的复杂度。本文引入软件编程技术、数据库技术等,将研究重点放在上位机的开发上,通过增加上位机的编译模块和SQLite轻型数据库管理模块,配合下位机相应的硬件电路,有效地解决了上述问题。

1 系统总体设计

1.1 测试原理分析

数字芯片测试仪的基本测试原理是:首先,根据被测试片的逻辑功能生成测试集和结果集;然后,利用硬件电路将测试集转换成电平信号并加载到被测芯片的输入引脚,而后读取被测芯片的输出电平信号;最后将采集到的输出电平信号与结果集进行比对,判断出被测芯片的完整性。

上述基本原理在实际应用过程中有2个突出问题需要解决。一是测试集和结果集的存放问题。每一芯片都有其对应的测试集和结果集,存储测试集和结果集是需要空间开销的。如果将测试集和结果集存放在下位机的硬件存储设备中,会使得原本就有限的下位机存储空间更为拮据,故本文将测试集和结果集存放在上位机中。二是被测数字芯片输入输出引脚的确立问题。每组数字芯片对其各自的引脚定义不一定相同,一些引脚是信息量输入引脚,一些则是信息量输出引脚,在测试开始之初便需要确立引脚的输入输出状态性质。本文通过建立上位机和下位机的通信协议、通信协议来配置上位机所传递的数据。

1.2 系统设计

通过上述分析,将系统总体框架设计为上位机和下位机两部分,如图1所示。

①上位机软件部分主要由编译模块、数据管理模块、测试模块、串口设置模块以及SQLite数据库构成,主要实现对被测芯片的选定、类型扩充以及通信设置等基本操作。

②下位机则由以PL2303芯片为主的通信模块和以STC89C52芯片为控制芯片的检测模块配以外围扩展电路组成,主要实现对芯片的测试信号加载以及测试结果捕捉等操作。

图1 系统总体框架图Fig.1 Framework of the whole system

系统工作时,上位机的测试模块将被测芯片的测试集发送到下位机通信模块。通信模块接收测试集并发送测试信号到下位机测试模块,由测试模块产生激励信号对被测芯片进行检测,并采集被测芯片的输出响应。检测模块将输出响应发送到通信模块,进而发送到上位机的测试模块。测试模块将反馈信息集与被测芯片结果集进行比对,从而判断被测芯片的好坏。

1.3 通信格式

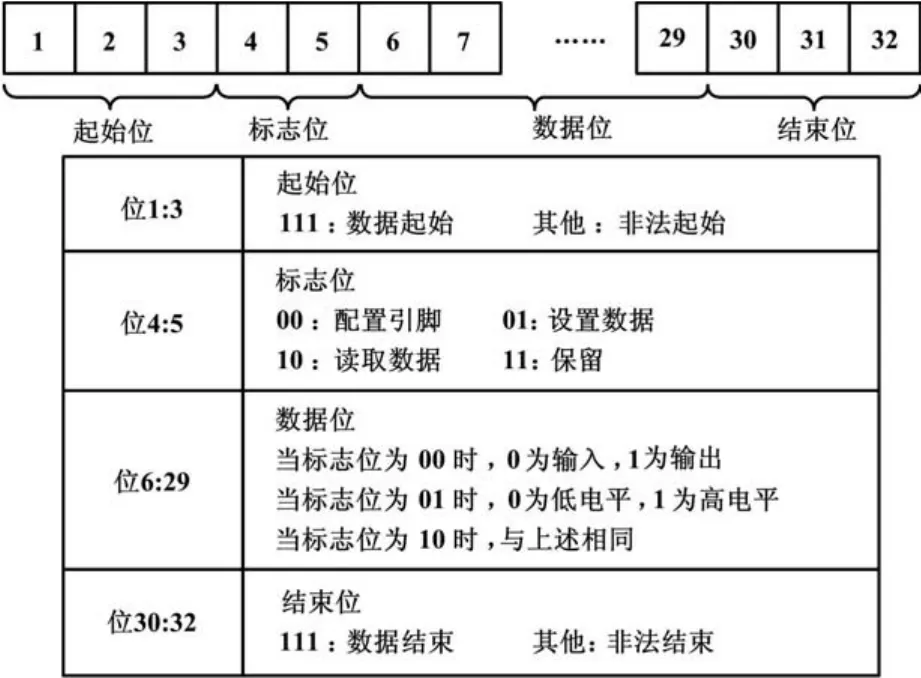

系统中上位机与下位机的通信需要有特定的格式,使上位机和下位机程序的编写遵循一定的依据,同时保证数据的完整性。上下位机间的数据通信协议具体格式如图2所示。

图2 上位机与下位机间的数据通信格式Fig.2 The data communication format between host computer and lower computer

上位机与下位机间的通信是通过数据帧来完成的。一个标准的数据帧分为32位:1~3位为起始位,标示该帧数据发送开始;4~5位为标志位,用于说明该帧数据的作用;6~29位为端口引脚的设置信息或输入输出情况;30~32位为结束位,标示该帧数据发送结束。

2 上位机设计实现

上位机软件使用C#语言编写,在Microsoft Visual Studio 2005环境和DotNetBar开发工具支持下完成。系统具有2个特色功能:一是能够由芯片的功能表达式生成测试集和结果集,二是芯片的测试集和结果集能够导出导入。这两个功能均需要在上位机上实现。由此可见,上位机是整个系统的指令控制枢纽。为实现有效的测试数据传输和数据存储管理,系统将上位机功能划分为4个模块。

上位机的软件体系架构如图3所示。

图3 上位机软件体系架构图Fig.3 The architecture of the host computer software

①编译模块,为有效扩展测试芯片,需要为每一个新增加的被测试芯片添加相应的测试集,这里采用编译模块来完成该项工作。根据用户输入的芯片功能表达式,利用编译原理的思想,结合测试集生成算法,生成被测芯片的测试集和结果集,并将测试集、结果集和被测芯片基本信息存入SQLite数据库中。编译模块的作用是根据用户要求动态添加新的芯片测试支持。

目前,常用的测试集生成算法有临界通路法、D-算法、FAN算法[6-9]、布尔差分法[10]等,每种算法各有其优缺点。本文采用操作简单、易于程序实现的临界通路法为数字芯片的测试集生成算法。

②数据管理模块,主要是通过操作SQLite数据库,完成对已存在的数字芯片的类型、基本信息及其测试集和结果集进行查找、修改、删除等基本数据操作。同时,数据管理模块具备整体数据的导入和导出功能,通过该功能及时更新数据库,从而满足用户对被测试芯片种类的及时更新要求。

开源的关系型数据库SQLite数据库,支持大部分标准SQL语言[11]。它没有独立的数据引擎,本文使用可视化管理工具SQLite Expert Pro v3.4.17实现对SQLite文件的构建和编写。SQLite数据库的数据文件是后缀名为.db的文件。该文件可直接由上位机程序通过API接口进行调用,实现对数据库的存取操作。

③测试模块,是直接实现对数字芯片进行检测的关键模块。测试模块根据用户对芯片类型的选择信息,从SQLite数据库中提取出对应芯片的测试集与结果集。同时,测试模块根据串口设置模块提供的串口传输信息,输出测试集、接收反馈信息,与结果集进行对比分析得出测试结论并显示。

④串口设置模块,是设置串口通信的基本配置模块,主要是针对不同的下位机对测试的串口设置要求不同而进行设计的。Microsoft Visual Studio 2005开发环境提供了SerialPort类,用于实现对串口通信的支持。通过初始化该类的实例即可完成对串口资源参数的配置。

除上述4个基本模块功能外,为满足用户的多样性要求,软件还包括如工具软件、快捷方式、日期提示、帮助文档、主题风格等多种功能。

3 下位机设计实现

3.1 程序流程设计

下位机是系统中具体的指令执行体,负责执行设备的控制指令,同时将测试结果反馈到上位机。下位机程序的执行主要分为串口中断处理程序和数据执行程序两部分。

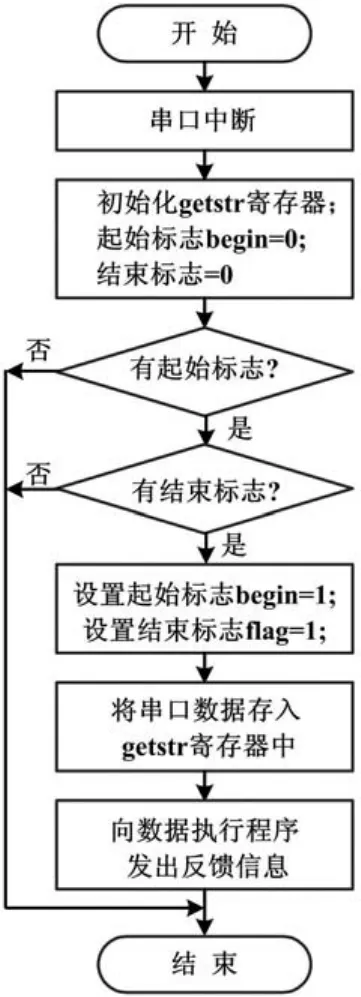

①串口中断处理程序流程图如图4所示。

图4 串口中断处理程序流程图Fig.4 The flowchart of the serial port interrupt program

每当下位机接收到上位机通过串口发送的指令时,下位机执行串口中断程序。根据定义的通信协议,中断程序首先判断该组数据的起始位和结束位是否完全正确。若不正确,则舍弃该组数据;若正确,则将数据存入getstr寄存器中,同时对数据执行程序进行信息反馈。

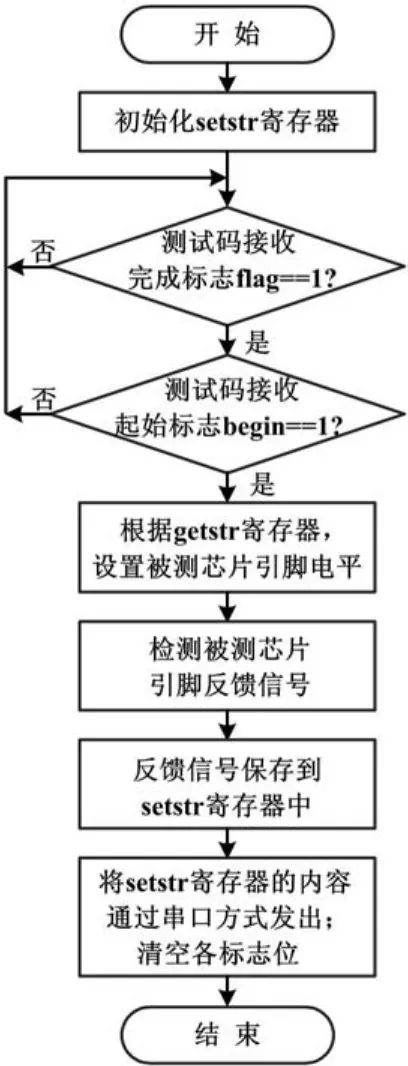

②下位机数据执行程序流程图如图5所示。

图5 数据执行程序流程图Fig.5 The flowchart of the data execution program

收到串口中断程序的反馈信息后,数据执行程序开始执行,程序首先判断flag和begin标志位是否均为1。若是,则执行测试程序;否则退出程序。

3.2 硬件设计

根据上述下位机程序的分析可知,下位机需要识别处理上位机的串口数据请求,需要有引脚与被测芯片进行连接,并具有一定的指令执行能力。经过仔细分析,系统采用STC89C52芯片作为下位机MCU,配合其他外部设备构成。下位机主要分为3个部分:USB转串口通信、STC89C52芯片最小系统、40引脚芯片锁紧座。

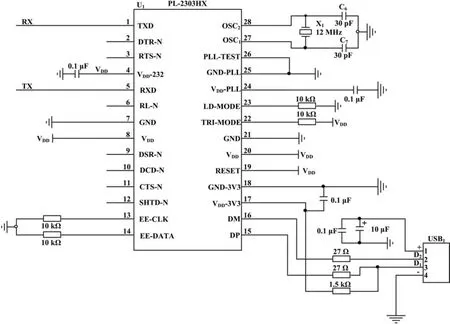

完成上位机与下位机进行通信数据解析的USB转串口通信电路图如图6所示。模块中采用PL2303芯片作为主要的数据处理芯片,另外包含驱动芯片工作的晶振电路以及稳压电路等。PL2303芯片能够将上位机提供的5 V电压进行转换,可提供3.3 V和5 V的两种电压型号,实现对不同工作电压芯片的检测。

图6 USB转串口通信电路图Fig.6 The conversion circuit of USB to serial port communication

下位机工作的STC89C52最小系统电路由晶振电路、开关复位电路等构成。为使芯片的P1引脚能够正常工作,将P1引脚进行上拉,上拉电阻为10 kΩ。

系统通过40引脚芯片锁紧座,将被测芯片与STC89C52的3组(P0、P1、P2)I/O口连接。由于被测芯片的最后一个引脚为VCC,因此本设计将最后一个引脚直接接电源,并通过STC89C52的P1.0引脚选择是连接3.3 V还是连接5 V电源。

3.3 硬件测试

硬件测试既是对所设计的下位机硬件电路的检测也是对上位机软件功能的检验。如对一片AT28C16芯片进行测试,需将芯片置放于芯片放置端,用锁紧座将其固定供电,在上位机的“其他芯片”一栏中选择AT28C16芯片,对其双击进行检测,实现硬件检测的目的。

4 结束语

本设计通过在上位机软件中引入编译功能和SQLite轻型数据库,以及对相应下位机硬件电路的设计,实现了新型数字芯片测试仪。该仪器具有两个突出特性:一是能够检测多种型号、不同功能的数字芯片;二是在系统中没有该芯片的测试集和结果集的情况下,可以通过编译功能实现测试集和结果集的生成,也可以通过数据导入的方式对测试芯片种类进行更新。因此,本设计具有更强的适应性和灵活性。

另外,本设计只能对24位以内引脚数目的芯片进行检测,在下一步的研究中本设计会在锁紧座引脚上引入数据锁存器,通过分时加载测试信号的方式实现测试引脚数的扩充。

[1] 尹超平,张秉仁,赵吉祥.基于VIIS-EM平台的虚拟数字集成电路测试仪的设计[J].电子技术应用,2013(5):89-92.

[2] 江丽君.数字集成电路故障模型研究及故障注入平台设计[D].哈尔滨:哈尔滨工业大学,2013.

[3] 余波,李维,吴兆耀.新型数字IC测试仪的设计[J].成都师范学院学报,2013(7):122-124.

[4] 肖宝森.多功能数字芯片测试仪的设计与应用[J].实验技术与管理,2010(12):133-136.

[5] 包本刚,刘坤,邹帅,等.基于FPGA/DSP的数字芯片测试仪[J].仪表技术与传感器,2010(7):42-45.

[6] 付鹏.专用电路测试方法的研究与实现[D].北京:北京理工大学,2011.

[7] 刘刚,黎放,狄鹏.基于融合算法的测试优化选择问题研究[J].计算机科学,2013(S1):54-57.

[8] 王红霞,潘红兵,叶晓慧.多故障的测试序列问题研究[J].兵工学报,2011(12):1518-1523.

[9] 付欣,付帅.求解测试集优化问题[J].科技通报,2012(6):96-97,100.

[10] 孙昌爱,程庆顺.基于故障的布尔表达式测试技术综述[J].计算机科学,2013(3):16-23-40.

[11] 付蔚,刘谋黎,蔡林沁.智能家居系统嵌入式家庭服务器设计与实现[J].自动化与仪表,2013(4):37-40.

Design and Realization of a New Digital Chip Tester

Aiming at the problems of traditional digital chip test equipment,such as the tested chips are fixed,PC software cannot be extended,and the testing circuit is complex,etc.,a new digital chip tester has been designed.The design consists of two parts:the host computer,and the lower computer,and the role of the software in host computer is highlighted emphatically.The compositions of host computer,including compilation module,data management module,SQLite database,test module and serial port setup module are researched, in addition,the serial communication module based on PL2303 as the core,and the circuit with STC89C52 as control chip in lower computer are designed.The system can precisely detect combinational logic chip,positioning the fault point,and dynamically create test set,expand measurable combinational logic chip.

Compilation function SQLite database Chip test Test set Result set Fault detection

TP36

A

国家自然科学基金青年基金资助项目(编号:31100711);

河北省高等学校科学技术研究青年基金资助项目(编号:20111122)。

修改稿收到日期:2014-02-20。

李天义(1986-),男,现为河北工业大学计算机应用技术专业在读硕士研究生;主要从事嵌入式系统的研究。