一种适用于空间飞行器的可重构信息处理平台硬件设计*

2014-05-22徐梦茗谢永春

江 卫,郑 艳,徐梦茗,谢永春

(中国电子科技集团公司第三十研究所,四川成都610041)

0 引言

随着空间技术的发展,世界各国对太空领域的争夺愈演愈烈,我国各种卫星、深空探测器等不断的发射成功,标志着我国进入了空间领域的大国。随着空间通信技术的不断发展,空间飞行器不断的增加,对空间通信系统的信号处理要求越来越高,各种业务信息、载荷数据以无线电方式进行着天地互通;越来越多的信息处理设备需要有逻辑功能可重构、参数可更换、运行代码可升级的特点,因此设计一种具有可重构的,能抗空间辐射的信息处理硬件平台对空间通信技术的发展具有非常积极的意义。

目前商用领域信息处理的硬件平台广泛采用的是大规模集成电路和高性能数字信号处理器,由于该类元器件大量采用片上SRAM,受空间高能粒子影响发生单粒子翻转(SEU,Single Event Up set)的概率大大提高,严重影响器件的正常功能,限制了这类元器件在空间环境中的应用,制约着我国空间通信技术的发展。文中结合商用可重构硬件平台的特点,在此基础上提出了一种基于DSP+FPGA架构的空间可重构信息处理硬件平台,可适用于空间飞行器信息处理设备的设计,并对其中的硬件功能重构、软件代码更换以及单粒子效应防护等关键技术进行了研究。

1 设计需求

随着通信技术的发展,大多数信号处理设备的硬件设计都具有高速的信号处理能力,运行代码可升级,算法参数可更换,功能可重构等特点;例如用于数据保护的信息安全防护设备,对涉及国家安全、军事信息、外交及商业机密的无线通信系统,提供安全防护[1]。在常规的星载电子设备中,为了防止空间中的辐射效应,选用的器件都是型号较老的反熔丝器件,数据一般都是固化在PROM里面,而对于某些信息处理来说,其中的算法、保护参数等都是具有生命周期的,在使用一段时期后,应该根据设计的生命周期进行相应的更换,固化的存储器、低速的处理器等电子器件显然不合适作为信息处理的硬件平台。DSP+FPGA的硬件架构最大优点是结构灵活,有较强的通用性,适合于模块化设计,能提高算法效率,系统容易扩展,非常适合做信息处理的硬件平台。这种硬件架构如果能有效规避空间辐射导致的故障,就可应用于设计空间飞行器的信息处理平台。

空间辐射效应主要包括总剂量效应、单粒子翻转、单粒子闩锁、单粒子功能中断、单粒子瞬时效应、单粒子烧毁等。DSP处理器具有高速度、低功耗的优势,一般采用CMOS工艺制造,内部主要由存储器、寄存器、地址程序译码单元和乘加单元组成;对DSP处理器来说容易受到单粒子翻转和单粒子功能中断的影响,这些辐射效应有可能引起DSP器件中某一个功能部件的失效,甚至导致整个DSP处理器无法正常的工作;对SRAM型FPGA器件来说,空间辐射效益危害较大的是单粒子效应;国外发射的39颗同步卫星资料异常情况统计显示:卫星异常状态记录中的71%是由空间辐射效应引起的,而单粒子效应故障占这类故障的55%[2]。高能粒子可导致配置存储器和块存储器中数据发生翻转,FPGA器件的控制寄存器、触发器和分布式RAM等也有可能发生单粒子翻转;如果翻转发生在逻辑功能区,可能导致设备的功能中断;如果翻转发生在RAM单元,可能导致数据错误或者丢失[3]。SRAM型FPGA需通过配置存储器进行加载,因此配置存储器中的数据控制着FPGA器件各组件的连接关系和逻辑功能,一旦发生单粒子效应就有可能破坏FPGA器件实现的功能,配置区域出错导致的功能错误不可预估,且可能会持续扩散,直到重新配置该器件功能才可恢复正常。因此,这种数据打翻被认为是FPGA中最突出的单粒子效应。随着微电子技术的发展,基于SRAM型FPGA和高性能DSP器件的晶体管工艺尺寸越来越小,密度越来越高、内核工作电压的降低和工作频率的大幅度提高,意味着电子设备的功耗更低、体积更小和重量更轻,这些特征都是空间飞行器电子设备所需要的。但电压降低和晶体管密度的增加,意味着器件更容易受到单粒子效应的影响,空间飞行器信息处理设备因单粒子翻转发生故障的情况会进一步增加,因此,使DSP+FPGA架构的硬件平台具有较好的抗单粒子效应的能力是其在空间飞行器信息处理设备中应用的关键技术。

基于SRAM型FPGA的动态加载技术为空间飞行器信息处理的可重构提供了基础,在本硬件架构的设计中,采用高可靠器件对SRAM型FPGA和DSP器件的单粒子效应进行监控,采用动态重构技术修复单粒子效应引起的器件故障,使高性能的SRAM部件可以在空间飞行器电子设备中得到运用。采用该架构的硬件平台运用于空间信息处理,既满足了算法要求运行速度高,关键参数可更换的需求,又符合空间飞行器电子设备应具备抗空间辐射的要求。

2 硬件平台的实现

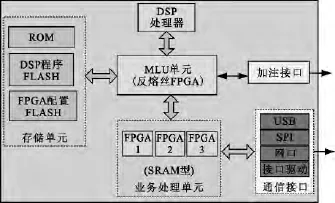

2.1 硬件架构设计

空间飞行器信号处理设备的硬件在传统DSP+FPGA架构上,增加了反熔丝FPGA器件作为监测和逻辑译码单元。硬件架构如图1所示,该硬件架构中主要对设备的处理器等部分的抗辐射和可重构进行了考虑,由于信息防护设备形态各异,与系统设备接口各不相同,关于通信接口不作具体描述。该设计采用高可靠等级的器件实现整个硬件电路的状态稳定,其中ROM单元和MLU(Monitor&Logic element Unit)采用一次性烧写的反熔丝器件作为可靠性设计中高可靠部件,再结合FPGA的动态配置能力和DSP运行代码的二次BOOT功能,实现抗空间辐射中的单粒子翻转。

图1 硬件架构示意Fig.1 Schematic diagram of the hardware architecture

在该架构中,MLU单元采用高可靠抗辐射的大规模集成电路实现,一般选用较多的是Actel公司的高可靠等级的反熔丝型的FPGA器件。MLU单元主要用于监测FPGA和DSP的运行状态并进行电路的逻辑译码,在MLU内部实现FPGA配置区回读功能、DSP器件的译码及看门狗功能等。通过FPGA回读功能可以发现FPGA内部配置区的功能块是否被打翻,如果打翻,可重新进行FPGA的配置,修复单粒子翻转导致的故障;高速数字信号处理器DSP芯片一般选用的是TI公司TMS320系列,该系列DSP芯片没有进行抗辐射加固处理,因此容易受到空间辐射的影响;该架构中,当DSP发生严重错误后,可通过MLU的看门狗复位及译码控制,重新引导ROM中的程序到DSP中运行。

2.2 DSP 电路设计

DSP芯片一般都是CMOS工艺器件,空间辐射的总剂量效应会对CMOS器件的PN结电路阈值电压和静态漏极电流造成影响,严重时会导致DSP功能的失效,但随着元器件升级和制造工艺的发展,处理器内核电压的降低、工艺水平的提高,器件的辐射总剂量承受能力会越来越高。因此对采用先进工艺的高性能DSP来讲,总剂量效应对元器件影响正逐渐降低。单粒子翻转、单粒子功能中断对DSP的影响主要是引起程序的“跑飞”或者“死机”,逻辑功能紊乱和模块间数据通信的异常等问题。对于这些问题,通过抗辐射容错、检错方法、以及高可靠器件实现的外部监控对处于错误状态的DSP进行重新加载等措施来解决。

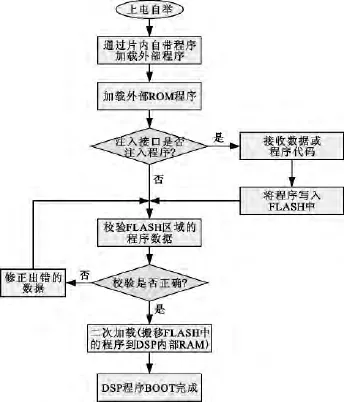

考虑到要进行参数更换,代码升级,因此该设计中,DSP程序分两种芯片存放,一种是不可更换的ROM,另一种是可更换内容的 FLASH存储器。ROM用于存放最基础的程序,主要用于对FLASH程序的校验、加载,以及通过注入接口人工注入代码等;程序FLASH中存储DSP的运行代码,该程序为空间飞行器信息处理设备的业务处理程序,具有周期性自检,外部存储区校验、SRAM型FPGA配置加载、FPGA实现的算法校验等功能,当发现数据区校验结果有问题时,重新刷新数据区域。DSP程序的自举流程如图2所示。

DSP芯片的BOOT过程是把程序数据导入内部RAM空间,然后运行业务程序,虽然RAM单元易受到高能粒子的影响而打翻,但可以充分利用其具有快速加载更改的特性,重新加载或更改出错单元来实现抗单粒子干扰。在上电加载过程中,首先进行第一次加载,该加载后的程序要设计得相对完善,因为固化后,不可再更改,在该程序中,具有注入接收处理程序,用于通过注入器注入二次加载运行的代码,以实现代码的更新,且存储代码以三模冗余的方式存储;如果无需注入,再进行第二次加载,在FLASH芯片的存储单元中选择校验正确的代码,进行加载,加载成功后,代码跳转到正常的业务处理入口处,开始执行程序。在业务处理中,必须有周期检验功能,随时校验RAM中的程序区代码有否打翻,如果有,则重新改写为正确的数据;数据区中的关键数据处理则进行三模冗余处理,通过以上处理方式,可大大增加抗单粒子翻转的能力。如果刚好导致当前运行程序出错,使自检失效、程序紊乱,则通过MLU单元中的监控电路,重新配置FPGA或者加载自身DSP运行程序,以实现单粒子翻转导致的功能部件出错。

图2 DSP上电加载流程Fig.2 Boot load flow chart

2.3 FPGA硬件设计

在该硬件架构中,有两类FPGA芯片,用于监控和逻辑译码的MLU单元采用反熔丝型FPGA实现,用于算法实现和数据业务处理功能的FPGA采用Xilinx公司的SRAM型FPGA实现,抗辐射设计主要是对SRAM型FPGA而言。SRAM在空间辐射环境中工作易受单粒子翻转的影响,带电功能粒子投射到FPGA器件的敏感区域通常会导致FPGA中的存储单元内容发生翻转,可能带来程序执行序列出错、计算结果出错等后果,严重情况下可导致系统崩溃。发生错误后,可通过后端的SEU恢复,如错误检测和纠正编码(EDAC),以及Xilinx公司提出的刷新(Scrubbing)、回读检测等[4]方法进行恢复。

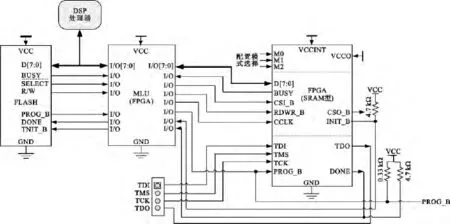

(1)FPGA的动态重构

SRAM型FPGA不仅具有可重编程能力,且处理速度快、集成度高。通过处理器或配置存储器将配置数据写入片内SRAM中,完成配置后,FPGA器件进入工作状态;器件掉电则配置数据丢失,FPGA内部逻辑功能和连接关系随之消失。这种SRAM型FPGA器件的逻辑功能随配置文件的变化而改变,非常适合信息处理的算法实现、定期参数更换等特点需求。这种可重构的特点为用户提供了很大的灵活性,使得在轨编程成为可能。硬件原理示意图如图3所示。

图3 FPGA动态重构电路示意Fig.3 Schematic diagram of FPGA reconfigurable circuit

SRAM型FPGA的配置通过MLU单元完成,FLASH存储器中存储 FPGA的配置代码,且该FLASH芯片的内容可通过DSP进行读写,就可以离线或在线的方式更换FLASH存储器中存储的FPGA的配置文件内容,实现FPGA的逻辑功能的动态重构。在MLU中实现DSP和FLASH以及FPGA配置线的逻辑译码,以及配置引脚的控制,对SRAM型FPGA的配置就可由DSP主动发起,刷新FPGA的内容,或加载不同逻辑功能的配置文件,实现FPGA功能的恢复或重构;当SRAM型FPGA内容被打翻时,就可通过动态重构功能刷新配置区,纠正因空间辐射导致的逻辑功能错乱。在进行FPGA动态重构的时候,可以采用局部重构或者是全局重构,局部重构这种方法能够在系统运行的状态下,对FPGA器件其中某些模块进行修改和更换。相对于全局重构来讲,局部重构的优势是对部分模块进行修改或更换,不干扰整个系统的运行,由于只修改部分模块,需要地面上传的配置数据也比较少。

(2)FPGA回读电路

回读电路的设计主要解决空间单粒子导致FPGA的配置区出错。当单粒子引起配置区数据翻转的时候会导致逻辑功能出错甚至系统崩溃;通过回读校验以及动态重构技术可以修复单粒子翻转造成的FPGA配置区错误。Xilinx公司的FPGA芯片可通过SelectMAP模式将配置区的内容进行回读校验,并动态刷新。为防止上电加载的配置数据受到单粒子翻转的影响,通常该存储器采用抗单粒子翻转的PROM存储器,但为了满足空间飞行器信息处理所需的参数可更换,代码可更新的特点,因此采用的是FLASH存储器,其中对数据进行三模冗余存储。如图3中左侧的FLASH存储器中存储着原始的配置数据,中间的MLU单元实现对SRAM型FPGA的回读及配置控制,通过配置端口对目标FPGA配置区域的数据进行刷新。

这种硬件架构具有很好的灵活性,可通过DSP或者MLU单元实现对目标FPGA的回读功能,回读配置区域中的数据,然后将回读的数据与外部FLASH存储器中保存的配置数据进行比较,如果检测出回读数据有错,则对出错部分的配置数据进行刷新,修复因单粒子效应导致的配置数据出错。对判断回读数据是否出错的检验方法通常有两种:一种是将回读的配置数据与原始数据进行比较,另一种是采用类似CRC纠检错编码;通过对回读数据的检错并刷新,能够准确地发现并修复FPGA器件发生的单粒子翻转错误。

(3)软件逻辑设计

在进行FPGA的软件功能实现时,也应充分考虑抗单粒子翻转。通过前面的方法,可以有效的防止配置区发生出错的情况,但是在FPGA中,还有很多的寄存器、分布式RAM和块RAM等等,这些里面存储的数据是根据输入或逻辑条件变化而变化的,通过回读电路无法检测有错误的发生。因此,在FPGA逻辑功能的实现时,要通过一些传统的手段,规避发生单粒子翻转,比如进行三模冗余设计,需实现三个相同功能的模块进行三选二的表决。若有一个模块发生单粒子故障,另两个模块工作正常,从而通过三取二的方式,保持最后输出结果的正确性。三模冗余方法消耗的资源较多,因此该方法需根据资源利用的实际情况进行选择。在星载FPGA中,空间环境辐射产生的存储单元SEU效应就相当于某种干扰和噪声对通信信道的影响[5],在本硬件架构中,对于实现较复杂的算法,较大的静态参数表等,则可以通过DSP处理器周期性进行检测,周期性刷新参数表;通过发送样本数据,检查算法输出的结果是否一致、检测算法本身运行结果是否出错。通过以上手段,可有效规避SRAM型FPGA遭受SEU效应的影响。

3 结语

该硬件架构设计既具有低功耗、高速度的优势,又具有FPGA的逻辑功能可重构和DSP运行代码可在线更新的能力;通过该功能能够实现空间飞行器电子系统的在轨升级以及功能更改,适应了某些信息处理设备需算法或参数周期性更换的特点。且可以充分利用天地互通信道对在轨平台进行持续的技术更新,减少空间飞行器的研发与发射,从而节约成本。值得注意的是,FPGA重新完全配置和DSP重新自举期间,设备处于非工作状态,在进行应用考虑时,应注意规避该情况的风险。文中的硬件设计能达到较好的抗SEU效果,为航天电子产品抗单粒子翻转设计提供了一种解决方案。

[1]刘在爽,王坚,孙瑞,等.无线通信物理层安全技术综述[J].通信技术,2014,47(02):128 -135.LIU Zai- shuang,WANG Jian,SUN Rui,etc.Review on Physical-Layer Security Techniques of Wireless Communications [J].Communications Technology,2014,47(02):128-135.

[2]王长河.单粒子效应对卫星空间运行可靠性影响[J].半导体情报,1998,35(03):1 -8.WANG Chang-he.The Single Particle Effect on the Reliability of Satellite Spatial Effect[J].ConductorIntelligence,1998,35(03):1-8.

[3]邢克飞,杨俊,王跃科,等.Xilinx SRAM型FPGA抗辐射设计技术研究[J].宇航学报,2007,28(01):123-129.XING Ke-fei,YANG Jun,WANG Yue-ke,etc.Study on The Anti-Radiation Technique for Xilinx SRAM -based FPGA[J].Journal of Astronautics,2007,28(01):123-129.

[4]徐斌,王贞松,陈冰冰,等.适用于空间环境下的FPGA容错与重构体系[J].计算机工程,2007,33(03):231-233.XUN Bin,WANG Zhen - song,CHEN Bing- bing,etc.FPGA Fault Tolerance and Reconstruction System of Suitable for Space Environment[J].Computer Engineering,2007,33(03):231-233.

[5]熊剑平,贾惠波,尤政.微小卫星数据存储器单粒子作用的检测及纠错[J].中国空间科学技术,2000(06):50-55.XIONG Jian- ping,JIA Hui- bo,YOU Zheng.Detection and Correction Micro Satellite Data Memory Single Particle Effect[J].China Space Science and Technology,2000(06):50-55.