一种干涉合成孔径声纳信号源系统的软件设计

2014-05-07冀志轩

冀志轩

一种干涉合成孔径声纳信号源系统的软件设计

冀志轩

(海军驻沈阳弹药军事代表室,沈阳 110045)

本文介绍了干涉合成孔径声纳信号源系统的软件设计过程,主要阐述了SOPC的系统设计过程、DMA数据传输方法、信号产生方法等。最后通过系统的部分测试结果表明能够达到要求。

干涉合成孔径声纳 信号源 软件 设计

0 引言

干涉合成孔径声纳信号源系统分成信号传感器数据采集子系统、发射信号产生子系统等。本文从SOPC的系统设计过程、DMA数据传输方法、信号产生方法等方面对该声纳信号源系统进行了软件设计。

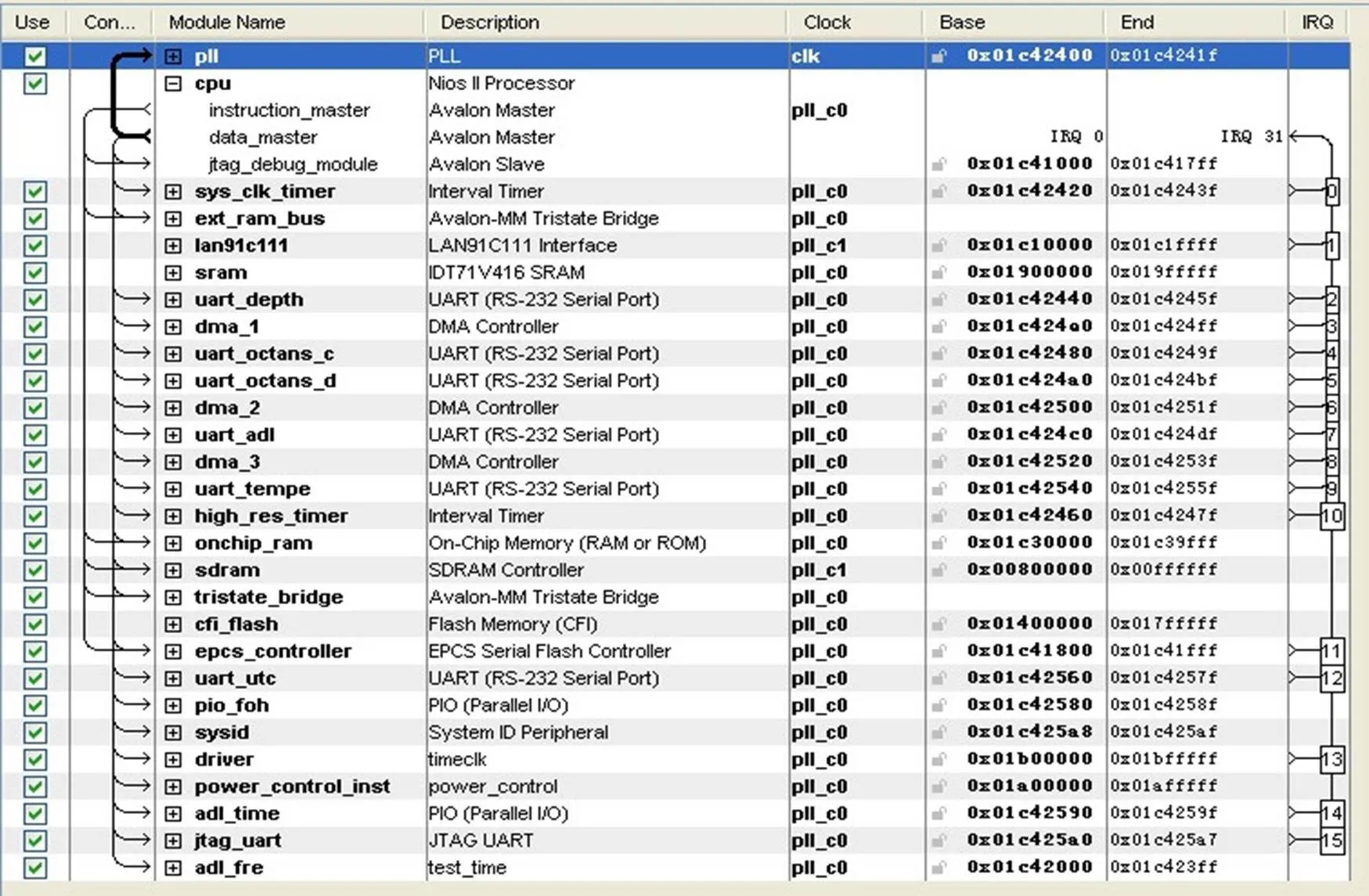

1 SOPC Builder开发

在干涉合成孔径声纳信号源系统的软件设计中,绝大部分组件都是Altera公司提供的IP,可以很方便的集成到SOPC Builder中去。如NiosII软核,LAN91C111网络接口,SDRAM和Flash控制器等,都是直接可以应用的。但也有一些自己开发的IP核,如DA的控制接口,通过按照Avalon总线接口标准设计,同样可以很容易的集成到SOPC系统中去。整个系统在SOPC Builder GUI下如图1所示。

2 基于DMA传输的传感器数据采集

2.1 Altera DMA控制器简介

DMA控制器用于执行从源地址空间到目的地址空间的直接存储器访问数据传输[2-3]。源和目的可以是Avalon从外设或是存储器内的一段地址范围。DMA控制器可以同具有流控制的外设联合使用,可以进行有固定和可变长度的数据处理。当DMA传输结束,DMA控制器可以发一个中断请求信号。

DMA数据传输定义为一个或多个由DMA控制器内核发起的Avalon传输的序列。DMA控制器具有两个Avalon主端口:一个主读端口和一个主写端口。一个Avalon从端口用于控制DMA,如图2所示。

Nios II中的DMA传输有以下三种形式:

1)存储器到存储器

这种情况下需要同时打开发送通道和接收通道,而且源地址和目标地址都是自增的。

2)存储器到外设

这种情况下只要打开发送通道,而且源地址是自增的,目标地址是固定的。

3)外设到存储器

这种情况下只要打开接收通道,而且源地址是固定的,目标地址是自增的。

在本设计中,由于是采集传感器的数据,属于外设到存储器这一类,源地址是固定的,目标地址随数据递增。

进行一次DMA传输的基本操作是:首先设定DMA要传输的数据量,当DMA传输完成后,产生一个中断,在中断服务程序中可以再次发起传输,这样可以对传感器的数据进行不断采集。

采用定长方式,对同样是定长数据包的传感器可以很好的采集其数据。但对于数据包不是定长的传感器采用定长数据传输的话,在一次DMA传输结束与发起下一次传输之间,会有数据的丢失,在实际调试时,也证实了这一点。

图1 SOPC Builder GUI

图2 DMA控制器内核原理图

2.2 对Altera DMA控制器的改善

由于采用Altera DMA控制器只定长方式传输存在如上述所描述的问题,所以要对其进行改善,以解决上述问题。

对数据丢失的原因进行分析可知,造成数据丢失是因为在一次DMA传输结束后,产生中断,在中断服务程序中发起新的传输。也就是说在系统响应中断服务函数的过程中,传感器数据仍在发送,而此时DMA没有在工作,所以造成了数据的丢失。

解决的方案是想办法让DMA在一次传输完成后,自动加载初始目标地址并启动新的传输,即让DMA工作在一种循环模式。这样就不会因为软件上的切换而造成数据丢失。同时,还要产生一个半传输完成中断,即在DMA传输完成设定数据的一半时,产生一个中断,此时软件可以对这前一半的数据进行处理,同时进行后一半数据的DMA传输。当传输完成时对后一半数据进行处理,这样相当于是在进行一个乒乓操作,而不会引起数据覆盖问题。

具体操作也很简单,在SOPC Builder中加入DMA控制器后,会生成相应的HDL描述文件,在工程目录下找到这个文件并对其进行修改,主要任务有:

1)增加几个备份寄存器。

如:reg [23:0] half_length; 半长度寄存器

reg [23:0] length_temp; 长度备份寄存器

reg [23:0] writeaddress_temp; 初始目标地址备份寄存器

reg hdone; 半长传输完成标志位

2)增加一个半完成中断信号。

Assign dma_ctl_irq = i_en & (done || hdone);

3)当传输完成时重新加载初始值。

//重新加载初始目标地址

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 0)

writeaddress <= 24'h0;

else if (clk_en)

if(done_transaction & ~d1_done_transaction) writeaddress <= writeaddress_temp;

else

writeaddress <= p1_writeaddress;

End

//重新加载初始长度值

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 0)

length <= 24'h0;

else if (clk_en)

if(done_transaction & ~d1_done_transaction) length <= length_temp;

else

length <= p1_length;

end

4)在NiosII中修改DMA的寄存器文件。

//状态寄存器中半传输完成中断位

#define ALTERA_AVALON_DMA_STATUS_HALFDONE_MSK (0x20)

#define ALTERA_AVALON_DMA_STATUS_HALFDONE_OFST

#define IOADDR_ALTERA_AVALON_DMA_HALFLENGTH(base) __IO_CALC_ADDRESS_NATIVE(base, 4)

#define IORD_ALTERA_AVALON_DMA_HALFLENGTH(base) IORD(base, 4)

#define IOWR_ALTERA_AVALON_DMA_HALFLENGTH(base, data) IOWR(base, 4, data)

通过实验证明,采用这种循环模式后,可以有效的解决在DMA切换时数据丢失的问题,提高了DMA传输效率。

2.3 数据采集工作流程

在数据采集的过程中,需要对接收到的数据进行打包,校验等工作,数据接收与发送的控制流程如图3中(1)所示,数据处理过程如图3中(2)所示。

图3 数据采集工作流程

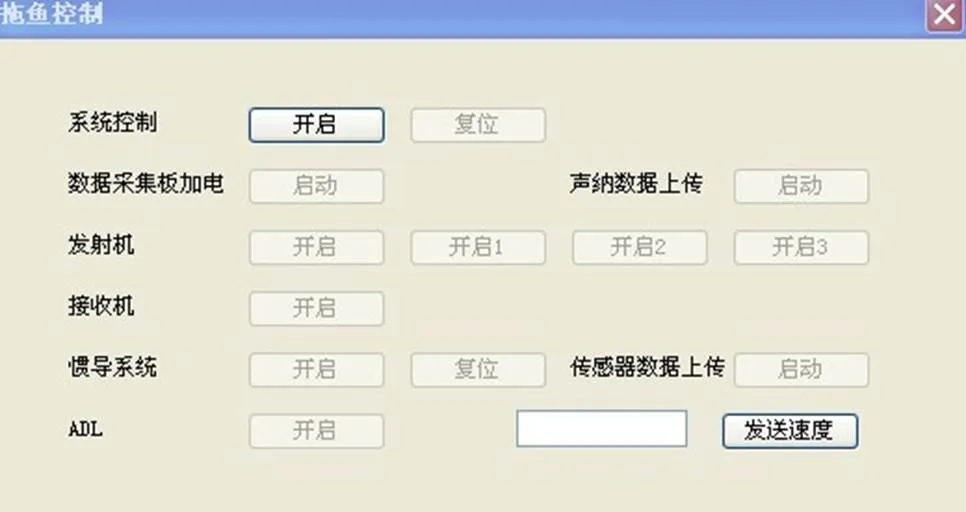

2.4 数据采集测试

在显示控制台端(其控制界面如图4所示),当启动传感器数据上传后,网络接将收到的数据写入文件中,以Octans数据文件为例,在Octans数据包中有时间信息,每一个数据包的时间间隔为200 ms。因此从时间信息可判断有没有丢数据包的情况。在数据包中的每一行数据信息结尾处,都有两位数据信息校验位,可以通过这两位对整行数据进行校验,这样可验证数据是否出错。Octans两个连续的数据包信息如下:

$HEHDT,269.15,T*16

$PHTRO,0.07,M,0.31,B*5B

$PHLIN,0.000,0.000,0.000*51

$PHSPD,0.000,0.000,0.000*5D

$PHROT,0.000,0.000,0.000*53

$PHHRP,-01,d,0F00002F*34

$PHZDA,000106.330,01,01,2006,00,00*5A

$HEHDT,269.16,T*15

$PHTRO,0.07,M,0.31,B*5B

$PHLIN,0.000,0.000,0.000*51

$PHSPD,0.000,0.000,0.000*5D

$PHROT,0.000,0.000,0.000*53

$PHHRP,-01,d,0F00002F*34

$PHZDA,000106.530,01,01,2006,00,00*5C

其中$PHZDA行为时间信息,分别是分.毫秒,日,月,年,最后两位为检验位。经过长时间上十万数据包的测试,没有出现丢包,错数据的情况。

图4 系统控制界面

3 信号产生

在合成孔径声纳系统中,需要发射余弦信号,线性调频信号和余弦二相码信号,这三种信号都是采用直接数字频率合成(DDS)技术,其理论基础是奈奎斯特采样定理[4-6]。当采样频率大于等于信号的最高频率两倍时,采样序列信号就保留了原始信号的全部信息。

3.1 余弦信号

产生余弦信号的方法有很多种,常见的有查表法,曲线拟合法等。其中查表法易于实现,且精度高,速度快,所以在本设计中采用查表法实现。

由余弦信号函数表达式:

其中振幅=1;初始相位=0;偏移量=0;角频率=2π,其中为输出信号的频率;所以余弦信号表达式可简化为:

首先建立余弦表,在Matlab下面可计算出0~2π对应的余弦值,为了提高信号的精度,在表中存储了0~2π对应的65536个余弦值。其值从-1到1,均为小数,无法直接作为DAC的输入,需要进一步处理。由DAC可知,当DAC的输入为全1,即65536时,输出信号为正的最大;当DAC的输入为全0时,输出信号为负的最大。DAC输入为32767时,输出为零电平信号。所以将0~2π对应的余弦值先乘以32767再加上32767,即可使得0~2π对应的余弦值处在0~65536范围内。

先计算出每个点对应的相位:

当相位不在0~2π内时,根据余弦信号的周期性可知,对2π取模,使其处于0~2π范围内,然后即可得出每个点对应余弦表的偏移量:

得到每个点对应的DAC转换数据后,将其写入SRAM中,当信号产生的门控到达时,DAC从SRAM读取数据,即可输出余弦信号。

3.2 余弦脉冲二相码信号

余弦脉冲二相码信号是携载二进制数字信息的随机脉冲序列,是一种数字基带信号。

表征二进制数字代码最常见的数字基带信号是矩形脉冲的单极性不归零码,如图5(a)所示,该信号易于产生,但带外辐射较大,且不含有同步信息,因而不便于直接在系统中传输。所谓余弦脉冲二相码信号就是图5(b)所示的余弦脉冲信号,利用前后相邻码元的载波相对相位变化传递数字信息。假设当前相位为,表征二进制数字代码“1”时,用π的余弦脉冲表示;表征二进制数字代码“0”时,用π的余弦脉冲表示,表示二进制数字代码“0110010” 的余弦脉冲二相码信号波形如图5所示。

余弦脉冲二相码信号是数字基带信号,是随机二进制脉冲序列,它可表示为:

其中是余弦脉冲信号,为码元持续时间,表示信息代码,当表示“0”码时,其取值为-1,当表示“1”码时,其取值为+1。

3.3 线性调频信号

调频信号是通过非线性相位调制获得大的时宽带宽乘积的典型例子,而线性调频信号是其中研究最早、应用最广泛的一种脉压信号。采用这种信号可以使声纳同时获得更远的作用距离和更高的距离分辨率,在信号分析中有独特的作用。其突出的特点是匹配滤波器对多普勒频移不敏感,即使回波信号有较大的多普勒频移,匹配滤波器仍能起到压缩的作用。但是这类信号的主要缺点是匹配滤波输出响应的旁瓣高。这样做的代价是:使输出信号的主瓣降低、展宽,从而导致输出信号信噪比损失及距离分辨力变差,在一定程度上降低了系统的灵敏度。

线性调频信号的复数形式数学表达式如下:

式中:为信号幅度;0为载波中心频率;为脉冲宽度;为信号带宽;=/为信号的调频斜;()为矩形信号包络。线性调频信号示意图如图6所示。

线性调频信号的瞬时频率为:

在Matlab下仿真结果如图7所示,其中:A=1000,f0=100,K=400。

图7 线性调频信号在Matlab下仿真结果

4 结论

本文主要介绍了干涉合成孔径声纳信号源系统的软件部分,详细介绍了系统开发中的主要过程,给出了各主要过程的流程图和部分例程,并给出了系统的部分测试结果,测试结果表明,系统达到要求。

[1] 陈钦树,文爱军.应用SoPC Builder开发电子系统[J].电子设计应用,2004,(09).

[2] 王静爽,孙楹.DMA控制电路在单片机中的应用设计[J].山东煤炭科技,2003,(03).

[3] 张晓明,王勇军,张民选.网络处理器中协处理器设计方法研究及实现[J].计算机工程与科学,2007,(03).

[4] 侯锡立,靳鹏云.基于SOPC的任意波形发生器的设计[J].计算机测量与控制,2008,(12).

[5] 崔坤,张文明,王滨.基于NiosⅡ的UART与PC间的数据通信[J].电子技术,2007,(Z1).

[6] 周亚凤,李跃华,朱昊.基于FPGA的16阶FIR滤波器的设计[J].南京工业大学学报(自然科学版),2005,(01).

Design of Software On Interferometric Synthetic Aperture Sonar

Ji Zhixuan

(Shenyang Naval Ammunition Millitary Office, Shenyang 110045, China)

TP319

A

1003-4862(2014)12-0009-05

2014-09-28

冀志轩(1989-),男,助理工程师。研究方向:弹药工程。