电场式时栅信号处理电路硬件平台设计

2014-03-26郑方燕

郑方燕

(重庆理工大学机械检测技术与装备教育部工程研究中心,重庆 400054)

0 引言

课题组前期研制的磁场式时栅位移传感器的信号频率为400 Hz,对信号的处理是通过一块FPGA对信号周期和相位差进行预处理,一块DSP实现复杂的算法处理,Flash和SDRAM分别作为程序存储和数据缓存,一块ARM做信号格式转换,FPGA、DSP、ARM 3块主芯片以及其外围配置电路放置在一块PCB上,系统复杂,速度慢。课题组正在研制的电场式时栅的信号频率为40 Hz,信号频率提高了100倍,对信号处理速度提出了新的、更高的要求,需要对信号处理电路进行重新设计以满足对40 kHz信号进行有效的、高性能处理[1]。

1 信号处理电路方案设计

提出基于SOPC技术的解决方案,将信号采集、处理和传输集成在单片高性能FPGA上,在FPGA上采用IP复用,使用VHDL硬件描述语言设计各部分功能模块,在Nios II软核处理器中对采集到的信号进行处理,整个设计结构简单、功耗低。设计好的系统方案原理框图如图1所示,由信号调理电路、FPGA主控电路和通信电路3个模块组成。时栅传感器动、定测头产生的感应信号为强度较小的正弦信号,这两路信号通过前置信号调理电路放大、滤波、整形得到两路方波信号,这两路方波信号送入主控电路板的FPGA内,通过在FPGA内设计的比相、计数模块获得动、定测头两路感应信号的周期和相位差,Nios II处理器对采集到的周期和相位差数据进行处理,最后转换成位移量,通过通信接口电路传输至计算机。

图1 信号处理电路原理框图

2 信号处理电路硬件平台设计

电场式时栅信号处理电路硬件平台包括信号调理电路、FPGA主控电路和通信接口电路。高精度、高抗干扰能力的模拟信号调理电路由放大电路、滤波电路及过零比较电路构成;高性能的主控电路以FPGA为核心,辅以高精度温补晶振;通信接口电路采用USB2.0的集成微控制器CY7C68013设计,这几部分电路模块构成的信号处理电路的硬件平台是信号处理软件运行的载体,为系统运行提供有力支撑。

2.1 信号调理电路

信号调理电路是对传感器感应到的原始信号进行放大,滤波及过零比较,以实现模拟信号向数字信号的转换,提取信号的相位信息。根据时栅位移传感器原理,时栅传感器通过获取动、定测头信号的相位差来确定位移量值[2],所以信号的相位信息是否准确将影响传感器的测量精度。

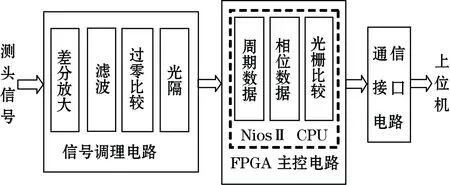

2.1.1 信号采集放大电路

电场式时栅通过平板电容进行信号耦合,输出阻抗较大[1],需要高输入阻抗的采集电路;定测头与动测头信号做差得到驻波[3],需要高共模抑制比的放大电路。根据电路需要设计的信号采集放大电路如图2所示,放大器由两级电路构成,其中U2A及U2B为第一级同相放大器,提供高的输入阻抗;U5为第二级差动放大器,提供高的共模抑制比。

图2 信号采集放大电路

由于信号频率较高,为避免进入非线性区,该电路设计增益Av=10,各电阻值根据放大倍数获取。为避免图2中Vin1和Vin2所包含的共模信号超出放大器的允许范围,将2个等值电阻R1、R2跨接到2个测头至参考地,将输入共模信号牵制在参考地电位值附近,保证了采集电路的正常工作。

2.1.2 滤波电路

电场式时栅传感器原始信号高频干扰信号将通过传感器耦合至采集电路,直接导致最终测量数据的较大波动,加大随机误差,影响数据稳定性[3]。传感器信号频率为40 kHz,为保证传感器信号有效通过,将滤波器的截止频率设计为48 kHz.预留一定冗余是为了有利于系统在复杂环境下的正常工作,提高系统可靠性。滤波电路如图3所示。

图3 滤波电路图

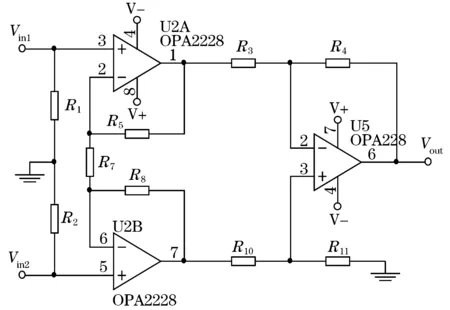

2.1.3 过零比较电路

过零比较实现将模拟信号转换为数字信号,以便于提取信号的相位信息。根据信号变换要求设计的过零比较电路如图4所示。电路采用正负双电源供电,解决了信号正负电轨问题,比较器的输出端为晶体管输出模式,输出用电阻下拉至地,实现与TTL电平兼容。

图4 过零比较电路

2.2 主控电路设计

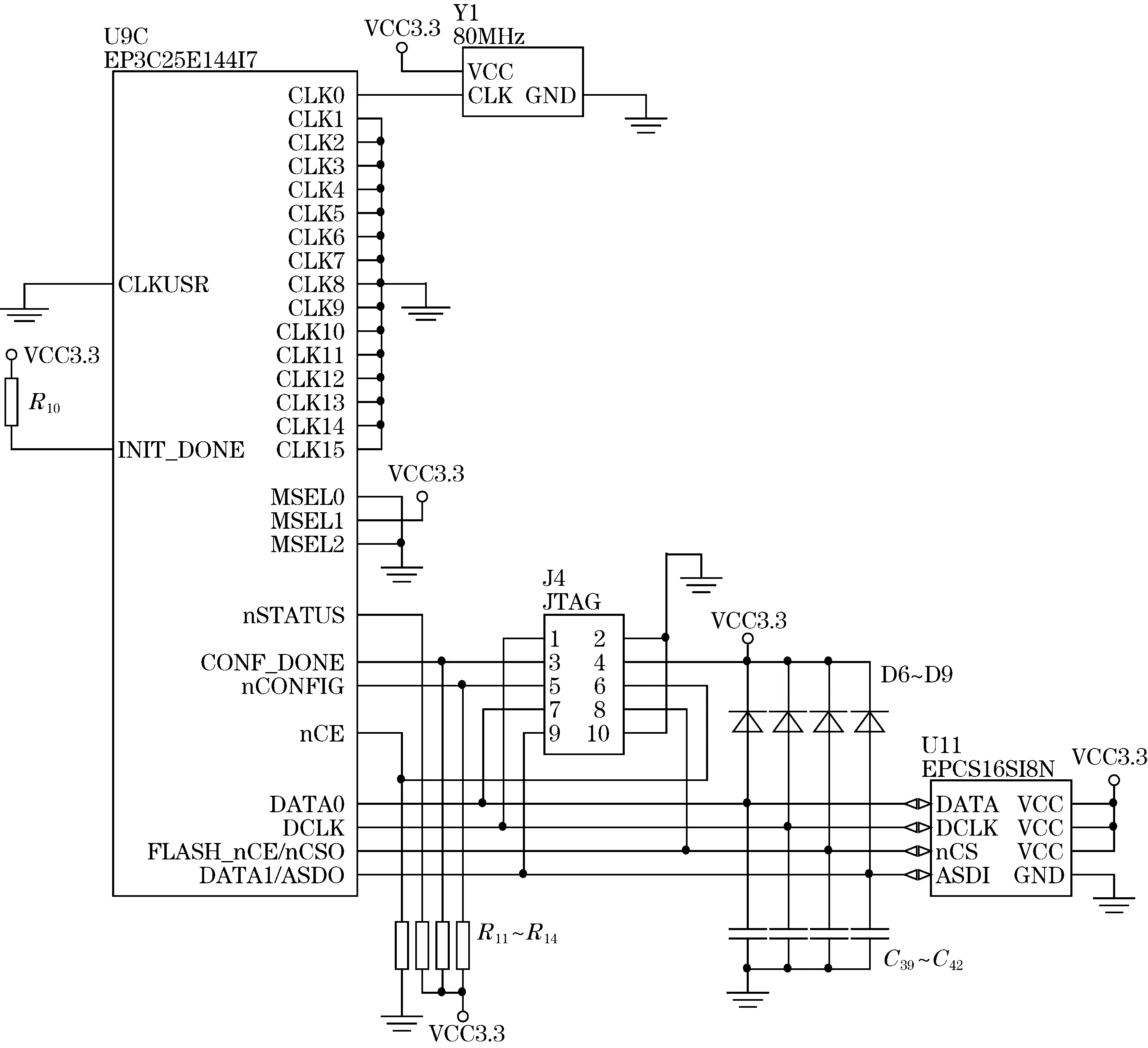

根据功能要求及FPGA资源参数,Cyclone III系列中的EP3C25E144I7满足设计需求,系统的配置电路如图5所示。

图5 系统配置电路

将FPGA配置为3.3 V电平标准的AS模式,即将MSEL0、MSEL1、MSEL2的逻辑值分别设为0、1、0。芯片配置分为复位,配置和初始化3个阶段,当nCONFIG或者nSTATUS为低,芯片处于复位状态,经过POR时间后,FPGA释放nSTATUS,进入配置模式,FPGA生成的串口时钟(DCLK)控制整个配置周期并为串口提供时序[4]。在AS配置模式下,配置芯片在DCLK的上升沿锁存输入和控制信号,并在下降沿送出数据,FPGA会在DCLK的下降沿发出控制信号并在DCLK的下降沿锁存配置数据,FPGA接收完配置信息后,释放开环输出的CONF_DONE,当CONF_DONE变成高电平时,FPGA开始初始化。外接的肖特基二极管和电容用于保护FPGA在AS配置模式下不会因过冲而导致对输入管脚的损坏。

2.3 通信接口电路设计

为了满足40 kHz信号测量要求,设计了USB通信接口电路以获得高速的数据传输速率。USB接口电路采用了USB2.0的集成微控制器CY7C68013进行设计,设计好的USB接口电路如图6所示。电路通过R42与C96构成的RC充放电电路为芯片提供上电复位信号,U14右侧的控制信号线和16位数据信号线与主控FPGA相连。通过标准的扁平USB接口插座J3即可与上位机或其他采用USB进行通信的设备相连。

图6 USB接口电路设计

3 实验结果

根据上述设计,制作的时栅信号处理主板电路简单、小巧。为了检验设计的信号处理电路的性能,对研制的信号处理电路板在电场式直线时栅测量装置下做了如下实验:

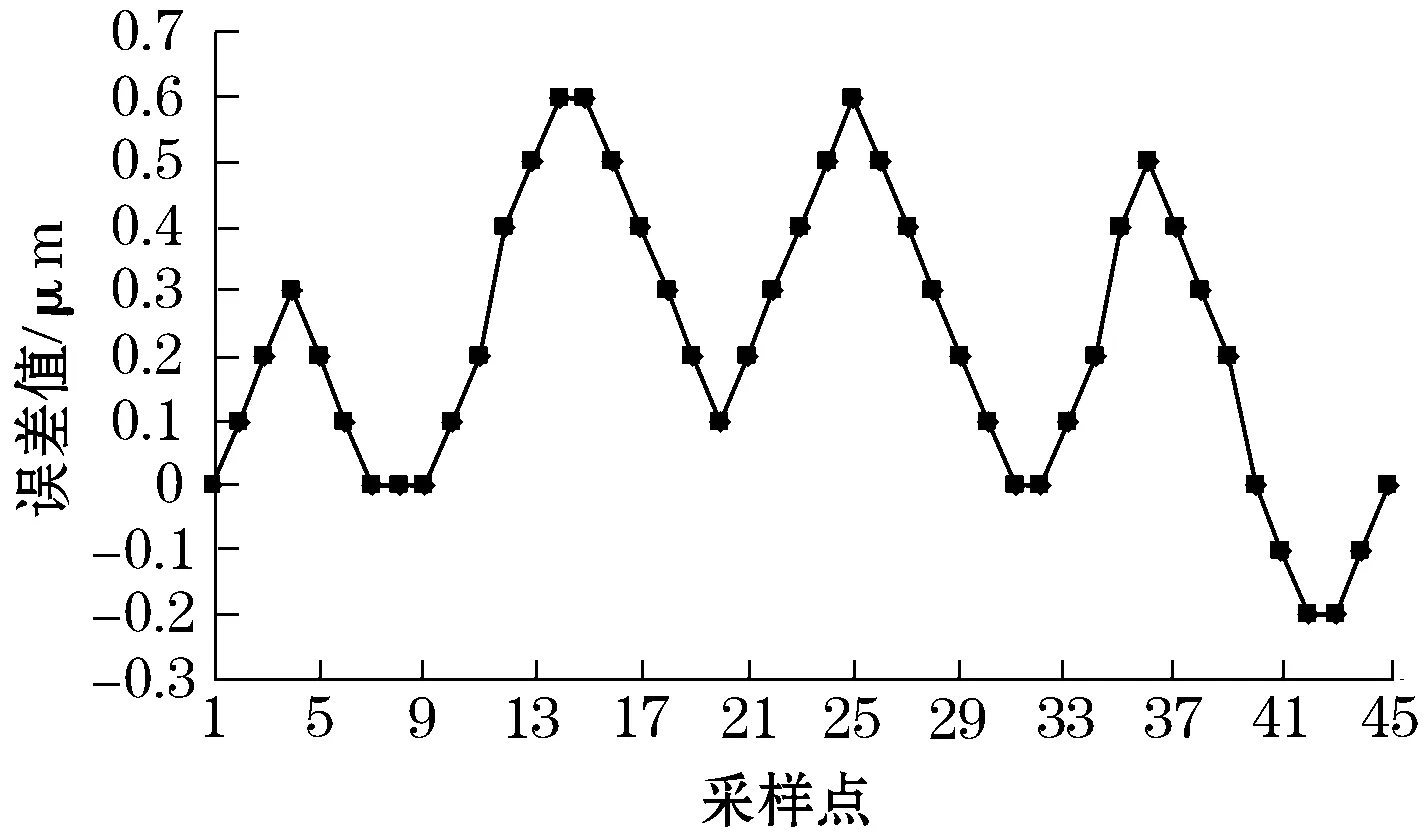

用RENISHAW ML10激光干涉仪作为测量基准进行精度测试,LabVIEW产生四相激励信号源,上位机控制直线导轨的运动,时栅的信号处理电路采用该设计研制的信号处理板,经信号处理主板处理好的数据为位移测量值,激光干涉仪采集到的数据为位移标称值,将位移测量值和标称值送至上位机进行对比,即得到时栅测量数据的精度值和误差曲线。图7为搭建的实验平台,图8为精度实验原始数据(未经过误差实时修正算法处理),在1个对极内误差的峰峰值为0.8 μm,根据时栅位移传感器的特点,误差在每个对极内具有重复性[5],表明用于该实验的量程范围为200 mm的电场式直线时栅在的误差峰峰值为0.8 μm,达到较高精度。

图7 实验平台

图8 电场式时栅原始误差曲线

4 结束语

(1)仅采用1块FPGA芯片完成了对信号的采集、处理、传输等功能,电路简单、稳定性好。

(2) 实验表明该电路在电场式直线时栅系统中得以应用,在200 mm量程内误差峰峰值达到0.8 μm,已达到较高精度,对图8的误差曲线进行频谱分析,误差主要为一次、二次和四次误差,采用谐波拟合的方法很容易对误差进行修改。经初步修正,电场式时栅的精度为0.3 μm,实现了高精度。

(3)此信号处理电路也可用于电场式圆时栅系统,或高速的磁场式时栅测量系统。

参考文献:

[1] 刘小康,彭东林,王先全,等.一种基于交变电场的时栅直线位移传感器:中国,2011101459675.2012-9-26.

[2] 彭东林,张兴红,刘小康,等.场式时栅位移传感器.仪器仪表学报,2003,24(3):321-323.

[3] 彭凯.精密电场式时栅传感器参数设计与优化:[学位论文].重庆:重庆理工大学,2013.

[4] Meyer-Baese.U.数字信号处理的FPGA实现.3版,刘凌,译.北京:清华大学出版社,2011.

[5] 刘小康.基于电气制导与误差修正的几何量计量新方法及新型栅式智能位移传感器研究:[学位论文].重庆:重庆大学,2005.