北斗/GPS双模射频接收模组的设计与实现*

2014-03-16朱常其孙希延纪元法廖桂生宁春林

朱常其 ,孙希延 ,纪元法 ,廖桂生 ,宁春林

(1.桂林电子科技大学 信息与通信学院,广西 桂林541004;2.西安电子科技大学 雷达信号处理国家重点实验室,陕西 西安710071;3.国家海洋局第一海洋研究所 海气相互作用及气候变化实验室,山东 青岛266061)

当前,北斗导航系统在大众层级中的普及应用有一定难度,相对于GPS的市场占有率,走北斗/GPS双模兼容之路不失为一种策略。为此本文提出了北斗/GPS双模兼容射频接收模组的设计方案,并详述了具体的设计经验,方案可以满足用户对高定位精度的需求[1-2]。

本文采用双MAX2769芯片的设计方案,芯片的工作性能比普通国产多模RFIC好,成本也远小于国产的相关射频接收模组。另外本文阐述的虽是北斗/GPS双模射频接收模组设计,但只需通过SPI总线进行相关寄存器 配 置 , 即 可 实 现 GPS_L1、GLONASS_L1、Galileo_E1、BDII_B1任意两两组合的双模射频接收模组的应用,这也正是本文的实用创新之处。

1 关键技术指标分析

在密集而复杂的电磁环境中,为实现接收机的高灵敏度和大动态范围,射频接收模组的设计中必须认真考虑灵敏度和动态范围问题[3-4]。

1.1 系统噪声系数与灵敏度

不失一般性,假设射频接收模组为一个双端口网络系统,根据噪声系数的定义,系统的噪声系数NF应为:

式中,S、N分别表示系统端口的信号和噪声功率。由于带电粒子的热运动会形成热噪声,输入端口噪声功率Ni可等效为:

式中,K为波耳兹曼常数(1.38×10-23J/K),T为系统绝对温度(290 K),B为系统等效带宽。

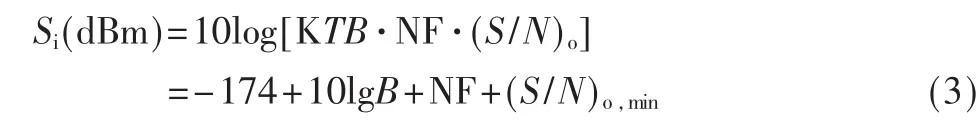

将式(2)代入式(1),整理得:

其中,(S/N)o,min为满足一定误码率条件下解调器所需的最小信噪比,Si(dBm)表示接收机的灵敏度。从式(3)可以看出,接收机的带宽、噪声系数NF和最小信噪比(S/N)o,min均会影响其灵敏度。

本射频接收模组是一个多级系统,系统的噪声系数NFsys定义为:

式中,NFi代表第i级的噪声系数,Gi为第 i级的资用功率增益。对于级联系统而言,NFsys基本取决于第一级的噪声系数和增益,第一级的增益越高,后级的噪声系数对NFsys的影响就越小。

式(3)表明,减小NF可以提高接收机的灵敏度。因此从整机最佳噪声系数设计的角度出发,可将射频接收模组进一步等效为图1所示结构。

图1 射频接收模组等效结构

分析式(4)可知,在满足设计要求的条件下,第一级若采用两级低噪声放大器(LNA)结构,则整机噪声系数会提高很多。

1.2 系统增益与动态范围

卫星导航接口控制文件规定:卫星发射的导航信号到达接收机天线输入口的最小保证电平:GPS_L1为-130 dBm,BDII_B1为-133 dBm[5]。实际应用中,天线口的信号强度还与卫星的高度、仰角以及接收天线的接收面积和接收机所处的工作环境有关,因此接收天线口所接收到的信号强度是一个动态的变化范围。另外,由于接收机射频模组的非线性特性,各级输出会存在大量的杂散分量,这些杂散分量若是落入工作带宽内,将会影响信号的信噪比。因此,业内定义三阶截点来表征这种非线性特性,同时还定义了无杂散动态范围(SFDR)用于比较不同接收机的动态特性[6],SFDR的表达式为:

式中,MDS取决于接收机的灵敏度,IIP3,sys根据级联系统的三阶截点定义,表示为:

其中,n代表第 n级,Gj为第 j级的增益。可以看出,IIP3,sys取决于级联系统中三阶截点最低的那一级。若第j级的增益较大,则第j+1级的三阶截点对系统三阶截点的影响会更大。

接收模组的ADC特性取决于系统设计要求,接收链路的总增益依赖于ADC和天线口热噪声功率。因此在指标分配时,要使链路具有尽可能低的噪声系数和尽可能高的三阶截点。

2 射频模组的具体设计

2.1 总体框图

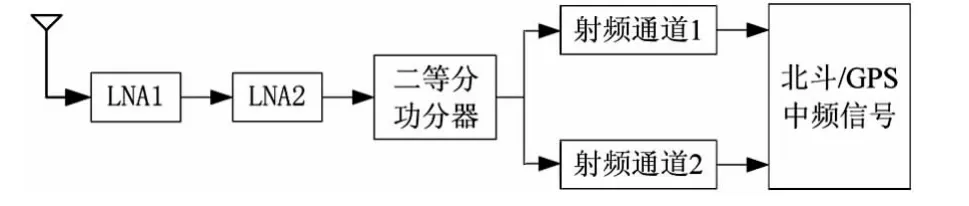

卫星导航信号经过天线、第一级LNA、第二级LNA、二等分功分器后,分别进入射频通道,各射频通道对接收到的卫星信号进行下变频、中频滤波和放大,最后送到模/数转换ADC并输出数字中频信号。模组的总体框图如图2所示。

图2 射频接收模组总体框图

2.2 LNA电路设计

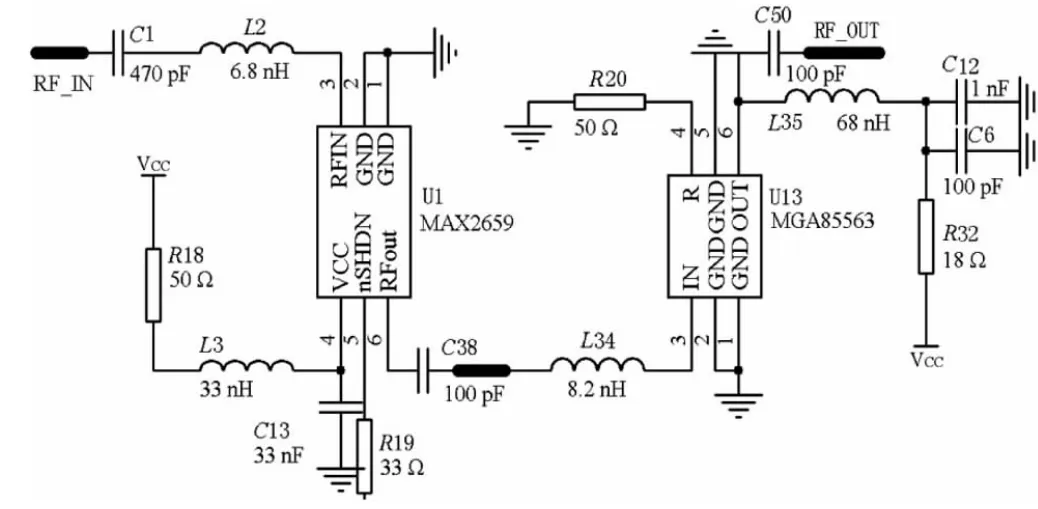

在设计LNA时,主要考虑噪声系数和增益。为了保证接收链路具有尽可能低的噪声系数,同时防止因增益过高而使放大器工作产生自激,本模组采用两级LNA设计结构。另外,由于北斗B1/GPS_L1的载波频率邻近,这里将各通道的LNA级统一处理,设计成一个通道。

LNA1采用美信公司的MAX2659芯片,它是一款专用于导航领域的低噪声放大器,封装尺寸仅为1.5 mm×1.0 mm,在1.5~1.6 GHz频段具有高达20.5 dB的增益,噪声系数低至0.8 dB。LNA2采用安捷伦公司的MGA85563芯片,在1.5~1.6 GHz频段的增益达 18 dB,噪声系数低至1.6 dB,三阶截点 IP3可调范围为 12 dBm~17 dBm。双LNA结构的应用电路如图3所示。

图3 前级LNA设计电路

2.3 射频电源设计

射频接收模组涉及 LNA、混频器、锁相环(PLL)、压控振荡器(VCO)、中频放大器、ADC等电路,这些模拟电路对噪声十分敏感,为它们的正常工作提供的直流电源必须在满足压差的条件下具备低噪声、高电源纹波抑制比(PSRR)和快速瞬态响应特性[7]。LDO(Low Dropout Regulator)是一种微功耗的低压差线性稳压器,其具有较好的输出噪声和较高的电源抑制比,因此特别适用于射频电源的设计。

根据LDO的工作原理,LDO的输出噪声受其内部设计和外部旁路、补偿电路的影响。其中LDO的基准源是其输出噪声的主要来源。为降低基准源的噪声影响,必须使用连接基准源的旁路电容。增大旁路电容能够减少基准源的输出噪声,但旁路电容值的增大,也会导致LDO的输出电压上升速率变慢,影响射频模组的正常供电,使用时需要注意。LDO的输出电容值也必须与负载匹配,这样既有利于提高电源的快速瞬态响应特性,又有利于降低LDO的高频输出噪声。

本文选用TI的TPS793XX系列芯片,它是一款专用于射频领域的LDO,在10 kHz频率处具有高达70 dB的PSRR,输出噪声低至 32 μVRMS,响应时间为 50 μs,压差低至112 mV。以GPS通道为例,其电源电路如图4所示。

图4 GPS通道的电源设计电路

2.4 参考时钟晶振电路设计

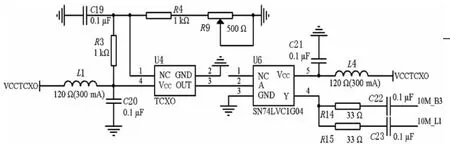

本射频接收模组中ADC采样与下变频器使用的是同一参考时钟,时钟晶振输出的频率偏差会传递给下变频器输出的中频信号,此时再使用带有频偏的采样时钟就会造成数据位的移位、伪码相位偏移、多普勒频移值估算误差增大。因此,保证频率稳定度、减少相位噪声是晶振电路设计的关键。本模组选用了0.5 ppm的TCXO,并经SN74LVC1G04整形输出。晶振的供电部分为防止电源噪声和地电位的跳跃,采用了滤波和去耦电路,这里使用村田公司BLM15系列的铁氧体磁珠,简化供电滤波电路的设计。晶振部分的设计电路如图5所示。

图5 晶振部分的设计电路

2.5 底层驱动设计

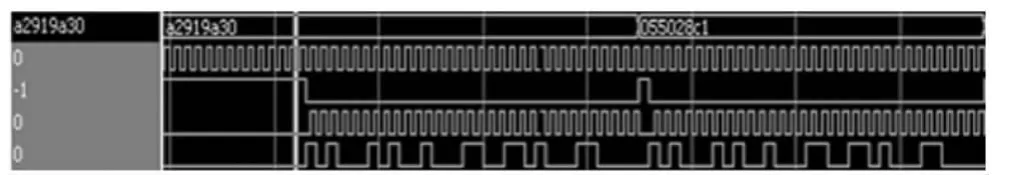

本射频模组采用两片美信的MAX2769B射频芯片,芯片 本 身 支 持 GPS_L1、GLONASS_L1、GALIEO_E1、BDII_B1频段,片内集成 LNA、混频器、镜像抑制滤波器、PGA、VCO、N分频频率合成器、晶体振荡器和多位ADC。在设计时需要根据导航信号的特性设置相应的配置寄存器。本文使用Verilog语言编写了4组与导航系统对应的驱动程序。以北斗B1的驱动程序为例,使用ModelSim对驱动程序进行仿真,如图6所示。

2.6 PCB设计

图6 北斗B1驱动程序的时序仿真

影响射频接收模组灵敏度的因素除了前述内容,PCB设计也不容忽视,如射频路径、射频接地、射频电源PCB、中频输出数据线都需要认真考虑。

由于射频信号的趋肤效应,射频路径及晶振参考时钟路径必须满足3 W原则,同时还要匹配到50 Ω。不良的射频接地也会导致寄生噪声、不期望的耦合和干扰增加,设计时除了正常的接地路径要满足最短原则外,还需要关注各级放大器链上的直流供电和直流偏置端口,这些特殊接地端口的阻抗对交流或射频电流必须接近于零,“零”电容、“无穷大”电感对于这些接地是一种很好的辅助手段。

晶振、电源是射频模组中的两大主要干扰源,电源部分的PCB设计除了前述的内容,还要保证完整的参考电源层和地层,两者之间的间距应尽可能短,以提高电路板噪声耦合性能。本模组采用T-G-P-B板层结构;晶振部分除了要远离射频路径以外,供电端口要增大供电线宽以降低耦合噪声。

3 射频模组的测试分析

3.1 模组的功能指标测试

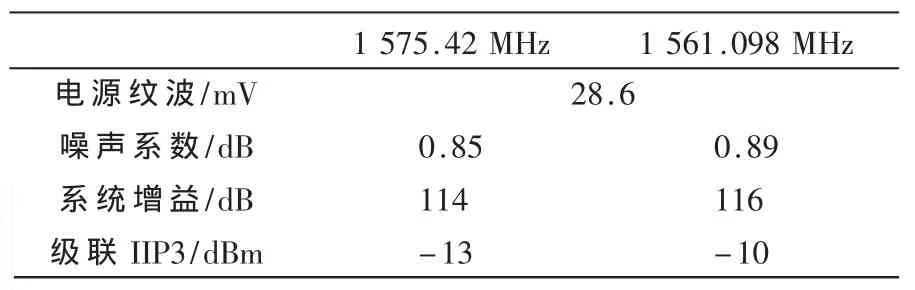

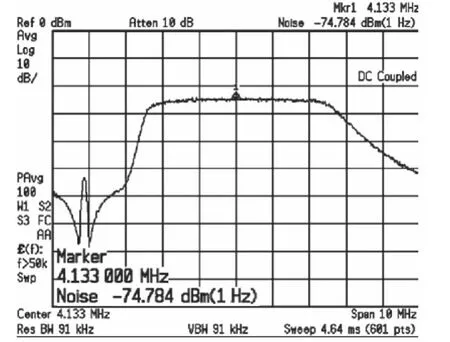

功能指标测试涉及电源纹波、噪声系数、三阶截点和增益,测试结果见表1。天线口噪声功率谱密度的测试结果如图7所示。

表1 射频接收模组功能指标测试结果

图7 模组噪声功率谱密度测试结果

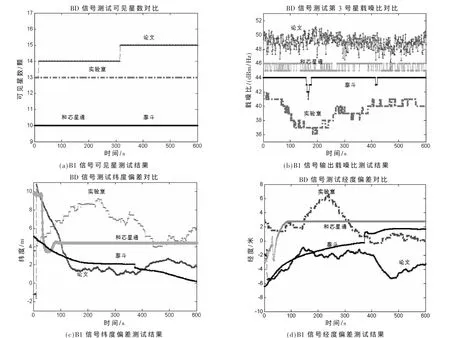

3.2 模组的应用测试

模组的应用测试涉及工作性能和稳定性两方面,测试方法:在同基带程序和基带电路的情况下,比较本模组与商用RX3007模组的工作性能,同时将这两款接收机与商用合芯星通接收机、泰斗微接收机进行定位性能比较。这里以北斗的B1信号测试为例,测试结果如图8所示。

图8 测试结果

测试结果表明,本文设计的射频接收模组捕获的卫星个数比实验室商用RX3007模组多,输出的信号载噪比都比其他商用接收机高一些,定位经纬度与商用RX3007模组差不多,比其他商用接收机的性能稍好。

双模或多模卫星导航接收机可以减少卫星导航信号被干扰或遮挡的可能,同时还能减少卫星分布的几何因子,提高接收机的定位精度。本文设计的北斗和GPS双模兼容射频接收模组有着广阔的应用前景,同时还有利于当前北斗民用市场的推广及应用。本文针对多模导航接收机的应用,提出了射频接收模组的设计方案,详述了具体的设计经验,并进行了功能和应用性能的测试。测试结果表明模组性能良好,工作稳定,可直接应用于当前多模导航接收机的研究中。

[1]李杰,周健军.一种 GPS/Galileo双模双频接收机射频前端芯片设计[J].微电子学与计算机,2009,26(7):88-91.

[2]吴凤柱,何矞,焦旭,等.GPS/SINS紧组合导航系统信息融合技术研究[J].电子技术应用,2013,39(2):67-69,73.

[3]全会阁,刘宏立,童调生.2.4G直接下变频接收机射频前端的设计与研究[J].微计算机信息,2006,22(12-2),118-120.

[4]曹鹏,费元春.射频模拟前端对数字中频接收机动态范围影响的研究[J].电子学报,2007,12(35):2312-2314.

[5]中国卫星导航系统管理办公室.北斗卫星导航系统空间信号接口控制文件公开服务信号B1I(1.0版)[Z].2012.

[6]WANG Q,SOMA M.RF front-end system gain and linearity built-in test[C].VLSI Test Symposium,Proceedings,24th IEEE,2006:228-233.

[7]朱龙飞,莫太山,叶甜春.高电源抑制比低温漂带隙基准源设计[J].电子技术应用,2013,39(5):35-37,40.