小卫星平台某电子设备电磁兼容性设计

2014-03-16张兴国吴一帆

张兴国,李 庆,吴一帆,于 方

(北京控制工程研究所 北京 100190)

随着电子技术应用的日益发展,电子设备越来越复杂,电磁环境日趋恶劣,它影响了电子设备和系统的正常工作和性能。一个性能好的电子产品必须考虑电磁兼容问题,既不能有电磁辐射干扰其他电子设备的正常工作,又要具备较低的敏感度,能抵抗规定的电磁干扰[2]。

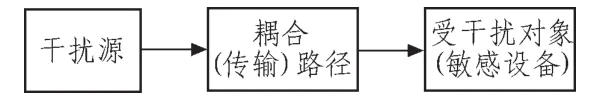

航天器电子设备对体积,质量和功耗的限制是十分苛刻的,而对产品高性能的追求也是不断提高。某电子设备是适应小卫星平台小型化、集成化的需求,将多种功能线路组合在一起,设备内部干扰源和敏感器件多,信号传输线多,空间小,相互间很容易造成干扰。如果干扰效应严重,将导致系统失灵,甚至可能产生严重的故障,所以电磁兼容性是该设备的一项重要指标。型就是这3个因素的串联,如图1所示。

图1 电磁干扰基本模型Fig.1 The basicmodel of EMI

系统或设备内部要发生电磁兼容性问题,必须同时存在以上3个因素,在解决电磁兼容问题时,要从这3个因素入手,消除其中某一个因素,就能解决问题。对新研制的电子设备,应该从设计开始阶段就考虑电磁兼容,进行电磁兼容设计。在设计阶段就考虑电磁兼容,远比制作成型后再试图满足电磁兼容标准要求而采取措施更节省人力和物力。所以电子设备必须在产品设计阶段就要考虑电磁兼容问题。

1 电磁兼容性与电磁干扰

2 某星载电子设备简介

电磁兼容性(EMC)是指电子设备在预期的电磁环境中能够协调、有效地进行工作的能力。其目的是使电子设备既能抑制各种外来的干扰,又能减少其本身对其他电子设备的电磁干扰。电磁干扰(EMI)可理解为一种有损于有用信号的电磁现象,干扰的来源主要有本电子设备内部形成的干扰以及外界耦合到本电子设备形成的干扰。

电磁兼容主要解决的是电子、电气设备或系统间的电磁干扰问题,构成电磁干扰必须具备3个因素[6],即干扰源、受干扰对象(敏感设备)及两者间耦合路径。电磁干扰的基本模

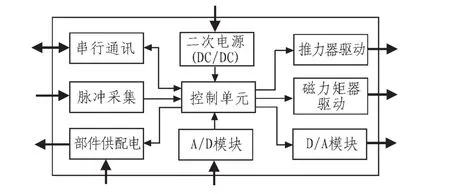

小卫星平台某电子设备是卫星的主要控制器之一,如图2所示。

图2 设备组成框图Fig.2 Equipment composition diagram

以处理器控制单元为中心,外围包括DC/DC模块、串行通讯模块、推力器驱动模块、磁力矩器驱动模块、供配电模块等单元。设备内既有DC/DC、部件供配电、推力器驱动等强干扰源信号,又有A/D和D/A输入输出小信号,同时还存在高速脉冲输入信号,以及控制单元内部的高速时钟信号。因而设备内部的电磁环境很复杂,电磁兼容性成为该设备的一项重要设计内容,结果的好坏直接影响产品的性能。

3 电磁兼容性设计

3.1 结构与地线设计

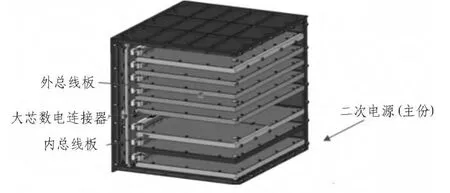

本星载电子设备采用无线缆机箱结构,相对传统电缆结构机箱,无线缆机箱能大大减少电磁干扰,这是因为80%的EMC问题是因电缆造成,电缆是高效的电磁波接收天线和辐射天线,同时也是干扰传导的良好通道[1]。如图3所示,设备采用双总线板结构,通过内总线板实现设备内部各功能板之间的信号传递,通过内总线板与外总线板之间的“大芯数转接内电连接器”以及外总线板上的“焊针型直插印制板电连接器”实现内部信号与设备外部信号之间的传递。

图3 机箱结构图Fig.3 The chassis structure diagram

机箱结构设计时,将强弱信号所在的线路板分开进行合理布局,易产生电磁干扰的线路板设置在机箱的上下侧边,使产生的干扰信号能通过机箱外壳释放,数字等敏感信号处理线路板放置在机箱中部,二次电源模块是主要的干扰源,由主备份两块线路板组成,正常工作时使用主份,所以将主份板放在机箱最外侧,备份二次电源板平常不工作,成为一道屏障阻止主份二次电源板产生的干扰信号向机箱内辐射。

设备内部的地线包括一次地、数字地和模拟地,其中数字地和模拟地属于二次地。设计时将数字地和模拟地分开布线,在设备内进行单点连接,一次地与数字地和模拟地进行严格隔离,避免单机接地故障为一次电源带来致命的危害从而影响整星的正常工作[4]。内外总线板是设备强弱信号输入输出通道,为遏制和减小这些信号之间的干扰,将内外总线板上的强弱信号按区域划分,同时分割相应的地层,由于地线层处处等电位,不会产生共模电阻耦合,也不会经地线形成环流产生天线效应,使电磁干扰能以最短的路径进入地线而消失。

3.2 滤波与屏蔽

滤波的功能是让指定频率范围内的信号通过,而将其他频率信号加以抑制。它是减弱传导干扰和辐射干扰最常用手段之一,特别是对瞬态干扰的抑制更有效。本星载电子设备的滤波设计主要是对DC/DC电源模块滤波和对线路去耦电容滤波。

在DC/DC模块的输入滤波电路主要由一级∏滤波和两级LC滤波电路组成,采用差模和共模组合式滤波措施,能有效阻止来自电源母线的噪声干扰,同时阻止DC/DC电源本身产生的开关噪声反馈到一次母线内阻上,形成公害。

在设计印制电路板时,通过在电路上加去耦电容来满足数字电路工作时要求的电源平稳和洁净度。去耦电容的充放电作用使集成芯片得到的供电电压比较平稳,减小了电压振荡现象,集成芯片可以就近在各自的去耦电容上吸收或释放电流,而不必通过电源线从较远的电源中取得电流。因此不会影响集成芯片的速度,同时去耦电容为集成芯片的瞬态变化电流提供了各自就近的高强通道,从而大大减小了向外的辐射噪声,且相互之间没有公共阻抗,因此抑制了共阻抗耦合。

设计时在每个集成芯片的电源和地脚之间加一个0.01~0.1μF去耦电容,有效去除信号线中的高频噪声。在每块线路板电源输入端接一组5μF电容和一组0.01μF电容,滤除电源线上的高频干扰和低频噪声。

屏蔽是利用屏蔽体对干扰电磁波的吸收、发射来达到阻止或减弱电磁能量传输的一种措施,能有效阻止电磁波从一个空间向另一空间传扬,主要用于抑制辐射干扰。屏蔽用低阻抗材料做壳体,把需要隔离的部件包围起来,被隔离的即可以是干扰源,也可以是防干扰的敏感设备,将屏蔽体和地相连,可以大大减少干扰耦合。

二次电源模块作为设备内部主要干扰源,设计时将其安装在密封屏蔽的金属腔体内,壳体与机箱紧密搭接与地导通,从而隔离了二次电源内部干扰信号对外部的辐射干扰,同时也能很好地提高二次电源的抗干扰能力。为增加机箱的屏蔽效果,箱体各面板间设计成卡槽结构,增加各面板接缝处的重叠尺寸,接缝处两连接面的重叠量与屏蔽效能有关系,增加重叠量相当于增加了缝隙的深度。另外,对机箱壳体的接缝处尽可能增加固定螺钉数量,减少螺钉间距,使得缝隙长度响应减小,使屏蔽效能提高。机箱的表面采用导电阳极化处理,机箱内的各印制板组件也都经过导电阳极化处理,使所有连接面保持导电,最终通过箱体上的接地址与系统壳地相连。

3.3 PCB布局布线设计

印制电路板中的电磁干扰问题包括公共阻抗耦合和串扰,高频载流导线产生的辐射,印制线条对高频辐射的感应等。其中以高频辐射问题最为严重,这是因为电源线、接地线及信号线的阻抗会随着频率的增高而增大,故较易通过公共阻抗耦合产生干扰,同时频率增高使得线路间寄生电容的容抗减小,因而串扰更易发生。

在设备内部,布局或布线不当是造成干扰的首要原因,大多数的干扰是发生在模拟数字混排的布局网或布线不当的印制线之间,所以正确的布局和布线是设备可靠运行的基本保证之一。

本星载电子设备内包含低电平模拟电路和数字逻辑电路,PCB设计时将二者分开布局,使得数字电路高频电流在印制板上的走线路径变短,有助于降低线路板内部的串扰、公共阻抗藕合和辐射发射。元器件的布局首先要考虑的一个因素就是电性能,把连线关系密切的元器件尽量放在一起,高速线走线尽可能短。功率信号和小信号器件分开,这样可减少组件之间的电磁干扰。

在数字电路设计中,不能忽略的是存在于器件、导线、印制线和插头上的寄生电感、电容和导纳,为此在布线时采取以下几条措施:

1)所有平行信号线之间要尽量留有较大的间隔,以减少串扰。如果有两条相距较近的信号线,最好在两线之间走一条接地线,可以起到屏蔽作用。设计信号传输线时要避免急拐弯,以防传输线特性阻抗的突变而产生反射和振铃,要尽量设计成具有一定尺寸的均匀的圆弧线。

2)印制板上若装有大电流器件,如继电器,它们的地线单独走线,以减少地线上的噪声。时钟信号和高速信号尽量避免换走线层,少用过孔,以减小过孔的寄生电容和寄生电感带来危害。

3)电源平面靠近接地平面,并且安排在接地平面之下。这样可以利用两金属平板间的电容作电源的平滑电容,同时接地平面还对电源平面上分布的辐射电流起到屏蔽作用。

(4)特别注意电流流过电路中的导线环路尺寸,因为这些回路就相当于正在工作中的小天线,随时随地向空间进行辐射。

4 试验验证

电磁兼容性测试包括电磁干扰发射(EMI)和电磁敏感度(EMS)测量。本星载电子设备根据国军标GJB151A-97《军用设备和分系统电磁发射和敏感度要求》试验要求,进行了以下 EMC试验项目:RE102:10 kHz~18 GHz电场辐射发射;RSl03:10 kHz~40GHz电场辐射敏感度;CE102:10 kHz~10MHz电源线传导发射;CS101:25 Hz~50 kHz电源线的传导敏感度;CS114:10 kHz~200 MHz 电缆束注入传导敏感度;CSll5:电缆束注入脉冲激励传导敏感度;CS116:10 kHz~100 MHz电缆和电源线阻尼正弦瞬变传导敏感度。其中,RE102、CE102 属于 EMI(电磁干扰) 的测量,RS103、CSl01、CS114、CS115、CS116属于 EMS(电磁敏感度)的测量。

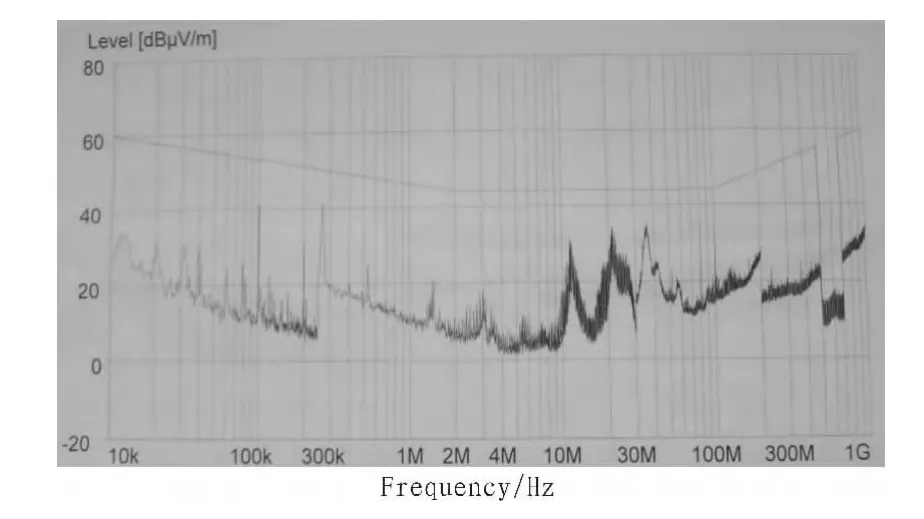

对设备进行以上7项EMC试验项目检测,结果7项检测项目都合格,产品的传导敏感度和辐射发射测试数据都符合GJB151A-97要求(RE102试验曲线如图4所示),证明本电子设备电磁兼容性设计有效,性能满足要求。

5 结论

图4 RE102曲线Fig.4 Curve of RE102

电磁兼容性问题在航天器电子产品的性能中起着至关重要的作用,本文针对小卫星平台某电子设备的电磁环境特点,结合实际工程经验,在设计实现上采取了多种技术的有效措施,使设计效果达到最优化,通过了相关的电磁兼容试验检测,收到了事半功倍的效果。这对同类电子产品设计具有很好的参考价值。

[1]郑军奇.EMC电磁兼容设计与测试案例分析[M].2版.北京:电子工业出版社,2010.

[2]王艳春,祖静,崔春生.印制电路板的电磁兼容性设计[J].计量与测试技术,2011,38(1):47-50.WANG Yan-chun,ZU Jing,CUI Chun-sheng.The EMC Design of Printed circuit Board[J].Metrology&Measurement Technique,2011,38(1):47-50.

[3]张金祥,张佳莺,王庆成.小卫星总体电路电磁兼容性设计[J].哈尔滨工业大学学报,2003,35(2):106-108.ZHANG Jin-xiang,ZHANG Jia-ying,WANG Qing-cheng.Design of electromagnetic compatibility for overall circuits of small satellite[J].Journal of Harbin Institute of Technology,2003,35(2):106-108.

[4]王志成,魏瑞刚,孙艳红.星载电子设备电磁兼容接地设计[J].无线电工程,2010,40(11):49-51.WANG Zhi-cheng,WEI Rui-gang,SUN Yan-hong.GND design for a spaceborne electronic equipment in EMC[J].Radio Engineering,2010,40(11):49-51.

[5]潘宇倩,白东炜.电磁干扰的产生及PCB设计中的抑制方案[J].航天器工程,2007,16(3):125-129.PAN Yu-qian,BAI Dong-wei.Cause of EMI and Restraining Scheme in PCB Design [J]. Spacecraft Engineering,2007,16(3):125-129.

[6]王志成.星载电子设备试验的电磁干扰三要素分析[J].无线电工程,2009,39(6):49-54.WANG Zhi-cheng.The three elements of eMI Tests for a spaceborne electronics[J].Radio Engineering,2003,39(6):49-54.