基于FPGA的RS485-USB转换器设计与实现

2014-03-12刘文怡

李 勋 ,刘文怡

(1.中北大学 电子测试技术国家重点实验室,太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

USB接口传输速率快并且性能优良,它支持3种信道速率:低速为1.5 Mb/s、全速为12 Mb/s以及高速为480 Mb/s[1]。但是USB传输距离也不能超过30 m,这就使USB在工业应用领域中受到传输距离的限制。RS485总线采用平衡驱动、差分接收结构,具有抗共模干扰能力强,灵敏度高,驱动能力强等特点[2],同时其显著优势是传输距离可达1200 m以上,但是RS485传输速度低,可靠性差。

将RS485、USB两者结合起来,优势互补,就能够产生一种快速、可靠、低成本的远程数据通信转换接口。目前,FPGA集成度高和工作频率、稳定性良好,抗干扰能力强,编写程序易于模块化控制,易于配置等优点,逐步成为各领域数字电路的首选。设计一种基于FPGA的RS485-USB转换器就可以有效应用到各种速率的数据处理、采集、在线检测场合。本文主要从系统总体设计方案、硬件设计和软件设计方面介绍一种基于FPGA的RS485-USB的转换器的设计与实现。

1 系统总体设计

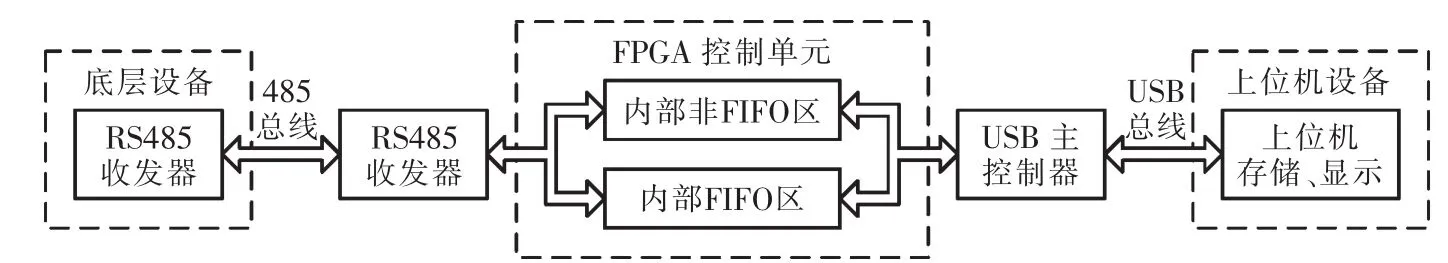

本文介绍的RS485-USB转换器主要是通过灵活配置FPGA实现RS485接口和USB接口实现通信速率可调的远距离数据通信,同时通过更改USB主控芯片的固件程序可以切换转换器数据立即串行传输通信和数据内部FIFO缓存并行传输通信两种模式,本文设计的固件程序选择第二种并行传输通信模式。系统的总体设计方案如图1所示。

该RS485-USB转换器主要包括RS485收发器、FPGA控制单元、USB控制单元3部分。系统工作原理如下:底层设备信号经485接口芯片转换为485电平,通过485总线传输至FPGA控制单元;FPGA单元主要负责接收485总线传输过来的信号,通过改变程序调节信号传输速率,对信号进行FPGA内部FIFO缓存,FPGA通过USB主控芯片对FIFO内部空、半满、满输出的3种存储状态进行判定。该设计中固件程序主要是对CY7C68013A接收到FIFO半满信号上升沿进行判定。若为上升沿,则FPGA将数据并行上传;反之监测等待。USB控制器就是上位机与FPGA控制单元的通信接口,用于双向传输信号;上位机设备主要负责数据存储、采集和在线检测并进行数据通道、波形显示。

2 RS485-USB转换器硬件设计

图1 系统总体设计框图Fig.1 System block diagram of the overall design

图2 硬件设计原理示意图Fig.2 Schematic diagram of the hardware design

本文硬件部分主要负责完成RS485与USB总线转换中的各控制模块的硬件电路设计,其满足了RS485与USB双向通信,保证了数据的准确性和抗干扰能力。硬件设计主要的原理示意图如图2所示。

本文设计的RS485-USB转换器中的硬件部分主要包括以下4个模块:

电源转换模块所选的FPGA芯片需要1.8 V供电,USB主控芯片和RS485协议芯片需要3.3 V供电,故设计选用具有高准确度、快速瞬态响应等优点的TPS70351芯片实现电平转换,满足设计中供电要求。

RS485总线接口模块RS485采用平衡发送和差分接收方式来实现通信,设计选用ADM3076E作为485接口芯片。在某些工业控制领域中,工作现场情况复杂,各节点之间存在很大的共模电压,虽然RS485接口采用的是差分传输方式,但当共模电压超过RS485接收器的极限电压,接收器就无法正常工作,严重时会烧毁芯片和仪器设备。为解决这一问题,该转换器设计中通过加入RS485将电源和RS485收发器的电源隔离,在信号输人和输出中均采用了光电耦合器HCPL-2631,其开关频率高达 10 MHz,完全满足数据传输要求,实现数据的长线传输。

FPGA控制模块主要负责整个电路中逻辑控制,其工作模式主要有系统复位模式、数据存储模式和数据转换模式。本设计选用的FPGA芯片是Xilinx公司生产的Spartan-2E系列XC2S50E,该芯片具有很高的逻辑资源,易于配置等综合性能;其程序下载PROM模块选用的是与FPGA相对应的XCF01SV020芯片,该芯片使用方便,能够为FPGA提供快速的再编程位流[3]。

USB总线控制模块主要负责控制连接FPGA与上位机的通信,本设计选用赛普拉斯研发出的芯片CY7C68013A作为USB接口电路核心芯片。CY7C68013A支持12 Mb/s的全速以及480 Mb/s高速传输,除集成了超强的USB2.0引擎SIE外,还集成了改进的增强型8051内核[4]。USB主控芯片CY7C68013A选用ATMEL公司的24C64芯片下载固件程序,该芯片具有很快的读写速度、低功耗,是现在使用的非易失性存储芯片中灵活性高的类型之一。

3 RS485-USB转换器软件设计方案

本文设计的RS485-USB转换器中的软件设计部分主要包括FPGA控制模块、CY7C68013A固件程序控制模块、设备驱动程序控制模块。

(1)FPGA 控制模块

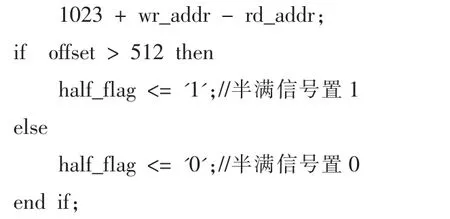

FPGA的功能控制程序是通过Xilinx ISE12.1软件平台实现,控制程序选用硬件描述语言VHDL语言进行功能模块化编写的。为了匹配FPGA和CY7C68013A之间的数据传输速率,提高数据的传输效率和准确性,在FPGA内部开辟了1 KB的FIFO缓存器。FPGA接收到RS485串口数据后,对其进行消抖、数据传输速率调整及波特率检测、串并转化处理,进行内部FIFO缓存时将写信号电平拉高,数据在写信号上升沿被写入到FIFO,同时写地址加1;当FIFO内部数据达到半满时,半满标志(half_flag)变为1,半满信号上升沿的跳变触发USB主控芯片CY7C68013A中的CTL控制信号将FPGA读信号拉高,同时在读信号上升沿将数据读出,通过USB接口传输给上位机,读地址加1。半满标志位通过读地址和写地址在FPGA内存中的相对位置进行计算,部分程序代码如下:

FPGA配置程序主要通过倍频、分频晶振基准频率和控制读写数据状态机来实现传输速率的可调,程序中按功能需求将各模块进行连接、通信。为了便于应用和检测,FPGA通过主程序控制MEN(2:0)信号选择底层设备,指示灯 LED(2:0)信号实时显示转换器与上位机在线检测时复位、设备连接、读数指示。

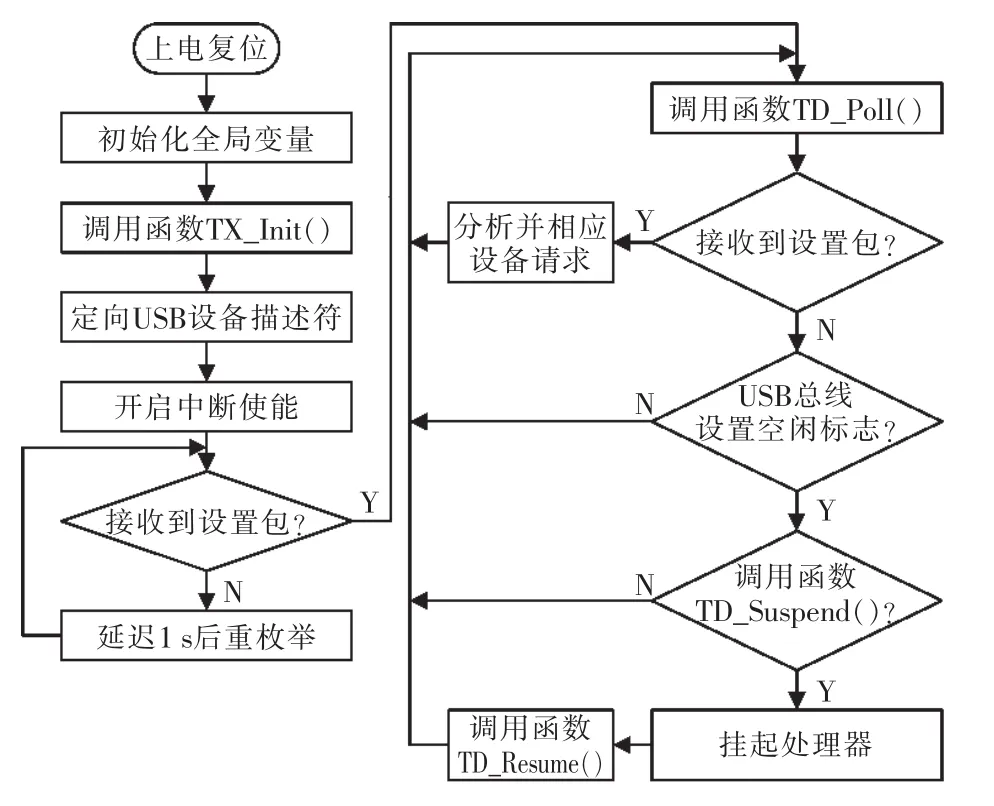

(2)CY7C68013A固件程序控制模块

USB通信数据、指令是通过CY7C68013A端点连接上位机与外部逻辑处理器FPGA。CY7C68013A的固件程序下载方式有两种:一种是固件程序下载存储到片外E2PROM中,上电后自动将固件程序加载到CY7C68013芯片RAM中;另一种是在线加载方式,计算机需要编写、存储固件下载驱动程序,当CY7C68013A连接到计算机后,由驱动程序下载固件[5]。由于第一种固件程序加载方式便于扩展、操作简单,本文选用第一种方式。CY7C68013A固件功能的实现主要集中在三个模块:调用TD_Init()函数完成CY7C68013A的初始化模块;设备请求模块,对应固件编程框图中的设备请求部分;重复调用函数TD_Poll()实现用户所需的功能模块,完成底层串口设备与USB通信数据之间的转化。在本设计转换器应用的固件程序流程框图如图3所示。

图3 CY7C68013A固件编写流程框图Fig.3 Flow diagram of CY7C68013A firmware preparation

(3)设备驱动程序控制模块

设备驱动程序主要实现主机与底层设备端口之间连接的功能,本文采用CYPRESS公司EZ-USB开发系统提供的全新驱动程序CYUSB.SYS。安装驱动时,需找到与用户编写的PID/VID代码、设备描述相匹配的CYUSB.INF文件,驱动即可被正确安装,此时设备才可以正常使用[6]。

4 功能测试

功能测试模块主要包括底层信号源设备、RS485-USB转换器、上位机3部分,其关系框图如图4所示。上位机软件主要采用VB进行编程,实现对底层信号源设备上传数据检测、实时显示的可视化界面操作。

图4 功能测试系统连接框图Fig.4 Connection diagram of functional test system

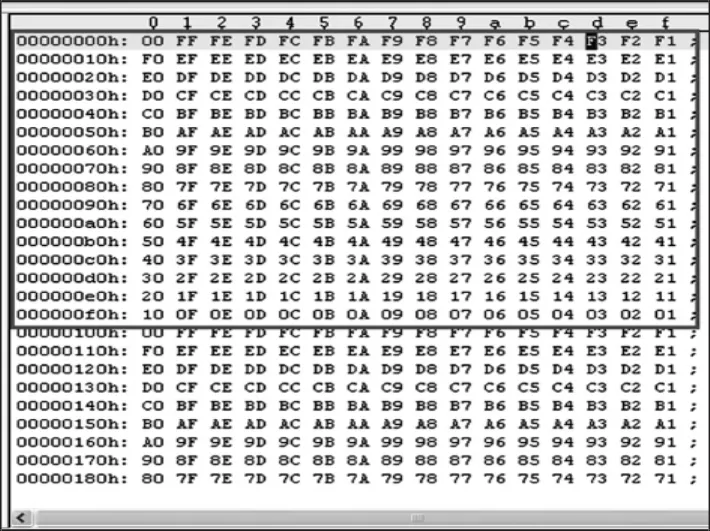

通过程序下载盒将FPGA各功能模块程序下载到该转换器XCF01SV020芯片中。转换器利用RS485接口接收信号源产生的递减数据,经过接口芯片转化,将差分信号转换成串行数据输入,图5为利用示波器测出的转换器RS485接口电路转换后RX端的信号波形。图5中截取了三组串行信号的波形,信号源设定串行信号第一位为起始位“0”,后八位为串行数据,最后三位为空闲信号“1”组成的十二位串行数据,并且先发低位再发高位。

从图中可读出三组信号为“000010110111”、“011100110111”、“001100110111”, 去掉起始位和空闲位,调整高低位顺序分析得出转换器接收到的信号源发出的三组递减数据位“01101000”、“01100111”、“01100110”。

本设计中递减数据实时采集图如图6所示。上位机界面显示递减数据结果与示波器测试转换器RS485接收底层信号源递减数据波形图结果一致,转换器实现了RS485总线转换到USB2.0总线接口的数据通信功能。

图6 上位机数据采集图Fig.6 PC data acquisition diagram

5 结语

本文介绍了一种基于FPGA的RS485-USB转换器设计方案,并进行了实验验证,其特点在于充分利用了FPGA易于编程和配置,以实现特定模块化功能,数据传输速率可调;同时结合了RS485接口具有长线远程传输特性,USB接口高速率传输、热插热拔优良特性,实现了快速、可靠、低成本的RS485-USB转换器转换功能。该设计转换器具有硬件电路简单、软件设计灵活、体积小、功耗低、可在线更新等特点,可以应用到工业数据采集、检测等领域,其传输速率范围可控制在9.6 kb/s~72 Mb/s,具有很高的实用性。

[1] 王宝珠,杨永,林永峰,等.基于USB接口的数据采集系统设计[J].电子技术应用,2010,36(1):67-70.

[2] 孙东,韩绍坤,邢怀飞.自制RS-232/RS-485转换器应用[J].电子测量技术,2005,48(3):17-18.

[3] 刘福奇.FPGA嵌入式项目开发实战[M].北京:电子工业出版社,2009.

[4] 马俊涛,李振字.S1aveFIF0模式下CY7C68013和FPGA的数据通信[J].中国传媒大学学报:自然科学版,2009,16(2):38-44.

[5] 呼媛,李白田,胡炳檬,等.EZ-USBFX2固件与设备驱动开发[J].微计算机信息,2010,26(7):162-164.

[6] CypressSemiconductorCorporation.EZ-USB FX2 Technical Reference Manual Version 2.2[Z],2003. ■