I2C串行接口数字芯片SCG103测试方法

2014-02-20赵影,高剑

赵 影,高 剑

(北京自动测试技术研究所,北京,100088)

I2C串行接口数字芯片SCG103测试方法

赵 影,高 剑

(北京自动测试技术研究所,北京,100088)

本文概述了I2C串行总线协议原理,研究了采用I2C串行接口的数字芯片的测试方法。在此基础上,研究了I2C串行接口时钟/日历芯片SCG103的测试方案,并在BC3192测试系统中开发了测试程序,成功实现了测试。该测试方法同样适用于类似的I2C串行接口数字芯片。

ATE;串行总线;串行接口;I2C;数字芯片;IC测试;BC3192

0 引言

串行总线是工业上大量应用的一种通信协议。随着集成电路产业和数字芯片的高速发展,串行总线协议也广泛应用于各类数字芯片。常见的串行总线协议如I2C总线、Microwire总线、SPI总线。与并行接口相较,采用串行接口的数字芯片具有较少的I/ O管脚、信号线和布局通路,能够明显减小芯片体积和封装体积,降低成本。串行总线一般采用打包数据的通信方式,使得数据的字符长度可随系统要求呈动态变化,适应性更强。

串行输入/输出的特点,使得采用串行接口的数字芯片往往具有较复杂的指令集,由此增加了测试向量的编写难度。同时,芯片本身的规模和逻辑复杂度,也决定了测试的复杂性。在测试中,既要考虑串行总线通信的时序特点,又要有效测试芯片的逻辑功能和电学性能。如何充分利用测试系统,以较低的成本、较大的故障覆盖率实现高效测试,是串行接口数字芯片测试面临的挑战。

I2C总线协议是一种典型的串行总线协议,最早由Philips公司推出。它是用于集成电路芯片间通信的二线制总线协议,电路结构简单,程序编写方便,易于实现系统软硬件的模块化、标准化,且性能稳定、价格较低,目前已得到广泛应用。本文针对I2C总线的工作原理,提出了采用此种接口的数字芯片的测试方法,并在BC3192系统中成功实现了I2C接口芯片SCG103的测试。

1 I2C串行接口数字芯片测试方法

1.1 I2C总线协议原理

I2C总线协议采用串行通信,主控器与各外围器件之间通过时钟线(SCL)与数据线(SDA)两条信号线传输信息,并根据唯一的地址识别各个器件。每一个连接在I2C总线上的芯片都可以作为发送器或接收器,在执行数据传输时,也可以被看做主机或从机,其含义如表1所示。

表1 I2C总线术语定义

另外,I2C总线协议具有一些时序特点,是在生成测试向量时需要特殊注意的:

1.1.1 位传输

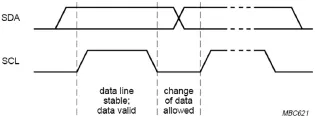

图1 I2C总线协议 位传输

每个时钟周期传输一位数据。SDA数据线的电平在SCL时钟高电平期间要保持稳定,此期间的SDA信号变化会被理解为控制信号。见图1。

1.1.2 开始/停止

SCL高电平,SDA由高到低跳变,表示数据传输开始。SCL高电平,SDA由低到高跳变,表示数据传输停止。见图2。

图2 I2C总线协议 起始/停止

1.1.3 字节格式与应答位

在开始、停止位之间发送的数据字节数目不限,每个字节后要跟随一个应答位。在主机生成一个额外时钟信号的同时,从机发出一个高电平信号,这就是应答位。从机在接收每个字节后,必须生成一个应答位。主机在接收每个字节后,也必须产生一个应答位。见图3。

图3 I2C总线协议 字节格式与应答位

1.2 I2C串行接口芯片测试模型

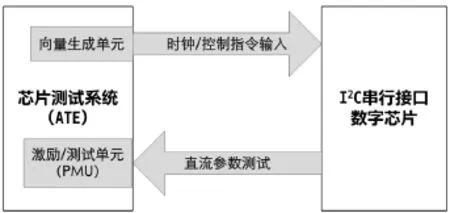

同大多数集成电路测试一样,I2C串行接口芯片测试主要包括功能测试和直流参数测试两项内容。由于I2C串行接口的特点,这种芯片一般具有较复杂的指令集,不同芯片需要测试的参数、功能也不尽相同。为了简明描述I2C串行接口芯片的测试方法,根据I2C串行总线的特点,我们建立如图4所示的通用测试模型。

在I2C串行接口芯片测试中,测试系统作为主机,被测芯片作为从机。测试系统为被测芯片提供电源,通过SCL发送时钟信号,通过SDA发送控制指令,接收数据信号。

图4 I2C串行接口数字芯片测试模型

I2C数字芯片测试一般分为直流参数测试与功能测试。对于直流参数测试,一般需要在测试某参数前,对被测器件输入一段控制指令,使其进入期望的状态。因此测试系统须通过向量生成单元向被测器件输入激励向量,然后通过激励/测试单元(PMU)测试相应管脚的直流参数。其测试模型如图5。

图5 I2C串行接口数字芯片 直流参数测试模型

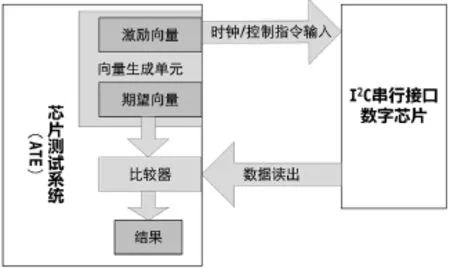

对于功能测试,测试系统须根据要求生成测试向量。将时钟和控制指令等激励向量发送给被测芯片,接收被测芯片输出的数据,并通过接收数据与期望向量的比较,进行失效判断。其测试模型如图6。

图6 I2C串行接口数字芯片 功能测试模型

2 SCG103的测试

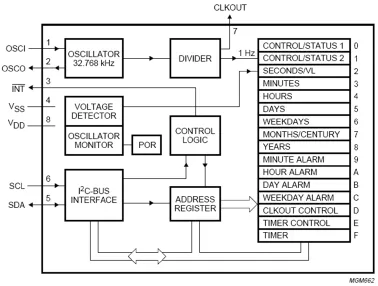

2.1 SCG103简介

SCG103是一种采用I2C串行接口的实时时钟/日历芯片,提供以下功能:

图7 SCG103内部框图

- 以32.768kHz石英晶振为基础,实现年、月、周、日、时、分、秒计时。

- 提供时钟、闹钟功能,通过SDA端口输出实时时钟/日历。

- 通过CLKOUT端口向外围设备提供可编程时钟信号,支持频率:32.768kHz,1024Hz,32Hz,1Hz。

SCG103的I2C接口读写频率可达400kHz,读写指令:读A3h,写A2h。读写地址自动增益。图7为SCG103的内部框图。

2.2 测试方案与实现

SCG103的测试分为直流参数测试和功能测试两部分。直流参数主要是测试不同状态下芯片电源端的静态电流,其具体测试流程如图8。

图8 SCG103直流参数测试流程

需要注意的是,各测试步骤必须按照图中顺序进行,且中间不能断电,以确保参数是在正确状态下被测试的。

SCG103的功能测试主要包括:复位值验证(RESET),频率验证(FREQ)和时钟走时验证(RUNTIME),其具体测试流程如表2。

如前所述,为满足SCG103的测试需求,ATE系统需具备向量生成单元,能够编写、产生激励向量、期望结果向量。须具备比较器,进行读回数据的失效判断。须具备激励/测试单元(PMU),以测试直流参数。其模型如图9所示。

BC3192系统满足上诉要求。在该系统的开发环境下建立测试程序:设置时间参数、编写测试向量、设置直流参数测试项,能够完成SCG103要求的所有测试项目。该测试程序已经成功用于产线批量测试。

在SCG103测试程序开发中,编写测试向量是关键点。由于指令/数据向量的串行格式,字节不易分辨,手动编写、修改比较困难。可对软件工具做出改进,在向量编写时仍用并行格式,如下面一段向量:

SCL SDA

01010101 11001100

01010101 00001100

再通过软件工具转化为如下的串行格式,可以使向量编写更加便捷:

SCL SDA

表2 SCG103功能测试流程

图9 I2C串行接口数字芯片 测试系统模型

3 结论

本文通过分析I2C串行总线协议原理,讨论了I2C串行接口数字芯片的测试方法。在此基础上以实时时钟/日历芯片SCG103为例,研究了I2C串行接口数字芯片的测试方案,并利用BC3192测试系统开发了测试程序,实现了参数、功能测试。该测试程序已成功用于产线批量测试。本文所述方法同样适用于其他I2C串行接口数字芯片的测试。

[1] 韩红星. PCF8563芯片的测试程序开发研究[C].中国苏州:第五届中国测试学术会议论文集,2008:426.

[2] THE I2C-BUS SPECIFICATION Version2.1[M].Philips Semiconductors.2000:8-11.

[3] PCF8563 Production Specifications[M].Philips Semiconductors.1999:4-16.

[4] 应建华,陈艳,郭艳.一种I2C总线接口的串行时钟芯片[J].华中科技大学学报(自然科学版),2006,34(5): 61-64.

[5] 蒋长斌,生晓坤,李杰,宋泽明.ARM Cortex-M3微处理器测试方法[J].电子测试,2013,07(4): 48-51.

赵影:女,硕士,北京自动测试技术研究所助理工程师,主要从事集成电路测试方法研究及测试系统研发工作。

Test Method for I2C Serial Interface Digital IC SCG103

Zhao Ying,Gao Jian

(Beijing Institute of Auto-Testing Technology,Beijing,100088)

This article discusses the principle of I2C serial bus protocol,and researched the test method for digital IC with I2C serial interface. Based on that,researched the test solution for SCG103,a real time clock/calendar IC with I2C serial interface.Test procedures are developed and successfully performed in BC3192 system.This test method is also applicable to similar IC with I2C serial interface.

ATE;Serial Bus;Serial Interface;I2C;Digital IC;IC Test;BC3192

TN40

A