基于NiosII的液晶屏控制器SOPC设计

2014-02-01卢俊平雷瑞庭

宋 跃,卢俊平,雷瑞庭,陈 卫,程 博

(1.东莞理工学院 电子工程学院,广东 东莞523808;2.华南理工大学 电子与信息学院,广东 广州510640)

基于NiosII的液晶屏控制器SOPC设计

宋 跃1*,卢俊平1,2,雷瑞庭1,陈 卫1,程 博1,2

(1.东莞理工学院 电子工程学院,广东 东莞523808;2.华南理工大学 电子与信息学院,广东 广州510640)

为实现TFT-LCD显示控制器的SOPC-IP设计,选择FPGA-EP4CE6F17C8作为设计验证平台,采用verilog语言,针对全彩AT070TN84TFT-LCD,由Nios II软核处理器、SDRAM控制器、JTAG UART、LCD控制器、Avalon总线等组成TFT-LCD控制器。以Nios II软核处理器为核心,各IP核(如SDRAM控制器、TFT-LCD控制器等)通过Avalon总线相连接到Nios II上,并通过Avalon总线接口模块、DMA模块、FIFO模块和时序产生模块完成了TFT-LCD控制器IP核设计,实现800×480分辨率,16bit颜色深度的彩色图形显示控制。显示实验运行稳定,图像清晰,色彩丰富,无闪屏、错行等现象,视觉效果良好,设计具有良好的可配置性、复用性和移植性。实践证明该设计行之有效。文中给出了控制器的设计原理、实现方法、仿真与实验过程的同时,重点讲述与控制器IP核相关的各设计环节。

Nios II;SOPC-IP;液晶屏控制器;直接存储器存取

1 引 言

在二维位置灵敏涂硼GEM中子探测器研制中,包含了大面积多层GEM探测器的制作、二维读出条的设计、信号与高压线的引出以及高速读出电子学的设计等关键技术,需要对一些参数加中子探测位置分辨、信号与高压线的监控读数以及各个参数的时间曲线图进行本地显示,便于对设备进行本地监控和维护。液晶显示器以其平板化、高分辨率、高对比度、无电磁辐射、低电压、低功耗、数字式接口、易集成和轻薄便携等优点已成为人机界面的主流器件之一,我们拟采用全彩AT070TN84TFT-LCD屏幕作为本地显示终端。利用液晶显示器关键是其LCD控制器及显示存储器设计,常规开发LCD驱动电路的方法不具通用性[1],本文运用EDA技术,实现了基于NIOS II的SOPC的LCD控制器IP核设计,得到了较好的显示效果,同时又提升了系统现有FPGA的利用率,提高了系统的集成度。

2 系统设计

图1是TFT-LCD控制器显示方案结构图。主要由Nios II软核处理器、SDRAM控制器、JTAG UART、LCD控制器、Avalon总线等组成[2-3]。以 Nios II软核处理器为核心,各种IP核(如SDRAM控制器、TFT-LCD控制器等)通过Avalon总线相连接到Nios II上。TFT-LCD控制器主要由Avalon总线接口模块、DMA模块、FIFO模块和时序产生模块组成。TFT-LCD控制器的作用是将SDRAM中的图像数据经过合适的格式转换后送给LCD使其按照正确的显示时序显示。采用PWM驱动方式来驱动背光电路的显示,PWM驱动方式的优点是利用其占空比可调的性质来调节屏幕的亮度。系统上电后,Nios II进行硬件初始化,将SDRAM帧缓冲区的首地址、LCD控制器地址、帧缓冲区大小写入到DMA控制器,同时写入LCD控制器的时序配置参数,以产生对应的LCD控制时序,启动DMA控制器。DMA控制器自动从传来的首地址处开始读取数据,并输出给LCD控制器。整个数据读取过程不需要CPU干预。本文在FPGA内部运用SOPC技术把CPU和LCD控制器整合到一块,并通过设置相应时序参数实现具有一定通用性的LCD IP核设计。本设计采用AT070TN84 TFT 液晶屏[4]。

图1 TFT-LCD控制器显示方案结构图Fig.1 Structure of TFT-LCD controller

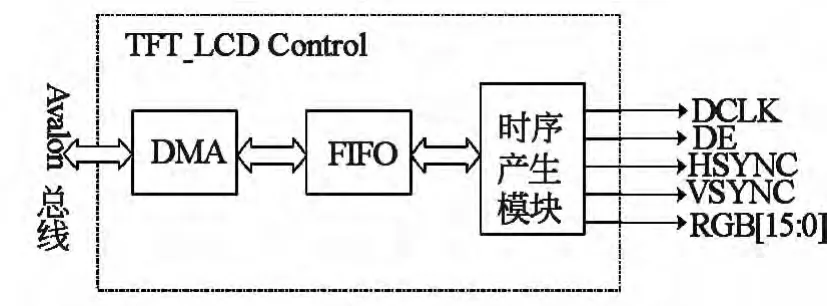

图2是TFT-LCD控制器结构图。LCD控制器启动后,DMA通过Avalon总线流模式读取传输的数据,然后存入FIFO模块中。时序产生模块根据LCD屏的时序规范生成行同步信号和场同步信号来判断是否从FIFO模块中读取数据,然后送出去显示。DMA自动从传来的首地址处开始读取数据,并输出给LCD显示。整个数据读取过程不需要CPU干预,从而提高了芯片的工作效率。FIFO模块主要缓存数据来匹配DMA读取的速度和TFT-LCD时序发生器输出的速度,以保证LCD工作在像素时钟域内,显示的画面连续稳定。该控制器可实现分辨率为800×480,颜色深度为16bit的彩色图形显示。

图2 TFT-LCD控制器结构Fig.2 Structure of TFT-LCD controller

3 液晶屏控制器SOPC-IP核设计

3.1 DMA模块

运用DMA模块,CPU只须向DMA控制器发送指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈给CPU,这样在很大程度上减轻了CPU资源占有率,从而提高了数据的读取速度。一个DMA控制器具有3个Avalon总线端口,包括1个Avalon从端口和2个Avalon主端口。2个主端口都是用于DMA传输通道,负责按照控制模块的指令,读取SDRAM中的数据并写入到FIFO中。而从端口用于DMA控制相关寄存器的读写,负责处理器与控制器的接口控制。

Avalon总线支持多个主外设,任何一个主外设都可以进行存储器访问(DMA),而无须Nios II处理器的干预。Nios II通过Avalon总线与外设进行数据交换。Avalon规定了各种传输模式,本IP核使用流传输模式(最适合DMA传输),图3显示了Avalon总线的流模式从端口写传输时序[5]。除了基本从端口传输中使用的信号外,流模式外设接口中还需引入readyfordata、dataavailable和endofpacket 3个信号。当readyfordata有效表示外设准备好接收Avalon总线模块的写传输,在下一个时钟的上升沿,来自具有流控制的主端口的传输开始;在写传输结束的时候,从端口必须将readyfordata置为低电平,这样该信号能立即对随后的传输起作用。反之当readyfordata失效时会迫使Avalon总线模块将送到这一端口的chipselect、write置为无效。故在readyfordata再次有效之前,Avalon总线模块不会对该从端口发起另一次写传输。本设计endofpacket置为低电平。Dataavailable有效来表示它能够为来自Avalon总线模块的读传输提供数据,本设计只进行写传输,故弃用。

图3 流模式从端口写传输时序Fig.3 Transmission timing write from port

3.2 先入先出缓冲模块

FIFO一般用于不同时钟域间的数据传输[6],它实现对DMA输出的图像数据进行缓存来匹配时序控制模块的传输速度,以达到TFT_LCD的稳定显示的要求。本设计采用Quartus II 11.0自带的FIFO宏模块,通过向导生成所需的模块供调用。大小为2 048×16bit。FIFO由DMA控制器写入数据,写入时钟为80M;由LCD控制器的时序发生模块读出数据,读出时钟为40M,即LCD的像素点扫描频率。wrusedw[10∶0]信号通过wrclk上升沿来记录存入到FIFO中数据个数,当wrusedw大于2 000时,置readyfordata无效,暂停DMA传输数据,否则置readyfordata有效,启动DMA开始传输数据,来保证系统的性能。rdempty用来判断FIFO中缓存数据是否全部读出,全部读完置为1。data接Avalon从端口的writedata,进行数据的传输;aclr接Avalon从端口的复位信号~rst_n。总之,FIFO模块起到缓存数据的作用保证了显示屏稳定高速的显示图像。调用FIFO模块的部分代码如下:

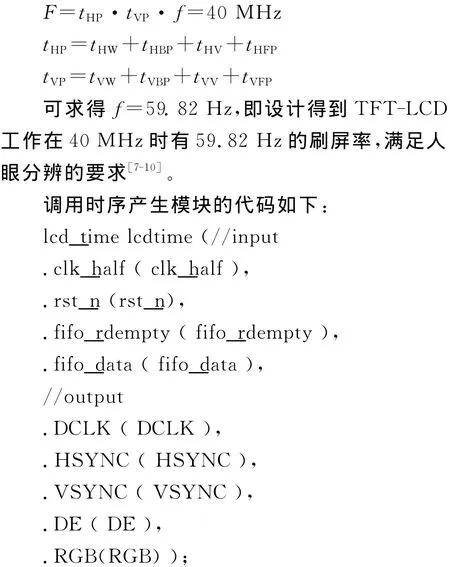

3.3 时序产生模块

LCD时序产生模块根据输入时钟和TFT_LCD的时序参数产生LCD显示所需要的行同步信号HSYNC、帧同步信号VSYNC、输出像素时钟信号DCLK、复位信号rst_n、数据使能端控制信号 DE[7-8],如图4所示。LCD 的显示驱动原理是采用逐行顺序扫描方式进行的,这种扫描方式循环周期很短,使得液晶显示屏上呈现稳定的图像效果。在行场时序的控制下屏幕从左到右(受行同步信号HSYNC控制),从上到下(受帧同步信号VSYNC控制)开始逐行显示。本设计所用AT070TN84TFT液晶屏采用DE模式显示。

图4 TFT-LCD控制器IP核Fig.4 IP core of TFT-LCD controller

下面主要介绍一下上述的几个信号:

(1)输出像素时钟信号DCLK:在一个DCLK周期中完成一个像素点的显示,在DCLK的高电平时读入像素数据,在其上升沿时将数据写到TFT LCD上显示。驱动每个像素点的数据进入LCD。同时作为其他信号的基准时钟。

(2)行同步信号HSYNC:它的一个周期tHP包括4个时间段:行同步低电平tHW、行消隐后肩tHBP、行有效显示tHV、行消隐前肩tHFP。行消隐后肩、行消隐前肩保证了行扫描的同步性。在每个HSYNC行有效显示tHV高电平时完成一行共800个像素的显示,DCLK产生800个周期。在HSYNC有效之前插入tHFP为210个DCLK,有效之后插入tHBP为45个DCLK,然后再开始下一行的扫描。

(3)帧同步信号VSYNC:它的一个周期tVP也包括4时间段:帧同步低电平tVW、帧消隐后肩tVBP、帧有效显示tVV、帧消隐前肩tVFP。每扫描完一帧(480行)后,立即插入1个VSYNC信号,该信号告诉LCD屏,新的一帧开始。同样,在VSYNC有效之前插入tVFP为132个HSYNC,有效之后插入tVBP为22个HSYNC。

(4)数据使能端控制信号DE:它控制显示数据的传输,只有当DE为高电平时,显示数据才能传输到LCD内显示,其有效宽度为800个DCLK。

设计TFT-LCD的像素时钟为40MHz,设f为刷新率,则有:

将上述各模块进行封装,生成图4TFT-LCD控制器IP核元件符号。

3.4 Nios II调试

采用 Nios II 11.0Software Build Tools for Eclipse(32bite)开发工具,进行软件测试。软件测试主要是测试LCD控制器是否能正确工作。首先往SDRAM中写入预定的图片数据来初始化显存,然后通过编程将相应的时序配置参数(HP=1 056;HW=1;HBP =45;HV =800;HFP=210;VP=635;VW=1;VBP=22;VV=480;VFP=132)写入LCD控制器中,同时将SDRAM帧缓冲区的首地址、LCD控制器地址、帧缓冲区大小写入到DMA控制器,启动DMA控制器观察显示屏的显示输出是否正确。Nios II中部分代码如下:

4 仿真与实验

TFT-LCD控制器设计过程中,采用 Modelsim SE10.0c软件仿真,仿真结果如图5,结果表明显示控制器显示时序正确。(为了显示清晰,在仿真时将TFT-LCD控制器的时序参数进行了一定比例的缩放。)

图5 仿真图形Fig.5 Simulation graphics

在硬件测试平台上,使用Quartus II 11.0软件完成硬件设计[10]。调试IP核时,采用Quartus II自带的SignalTap II Logic Analyzer进行逻辑分析,分析结果如图6。表明该控制器可正常工作。SignalTap II与Modelsim软件仿真不同,利用JTAG在线仿真,更准确的观察数据的变化,方便调试。

图6 逻辑分析仪显示图Fig.6 Graphic from Logic Analyzer

实验测试显示效果如图7所示,表明图像显示清晰,色彩丰富,没有闪屏、错行等现象,视觉效果良好,达到了预期的目标。

图7 实验结果显示Fig.7 Experimental results display

5 结 论

具有参数化组件的SOPC-IP核设计可以有效地实现了800×480分辨率,16bit颜色深度的AT070TN84彩色图形显示控制,具有良好的可配置性、复用性和移植性。

设计中若使用乒乓显存作为数据缓存模块,CPU和LCD控制器在Avalon总线上不会因为竞争带宽而影响性能,会显著提高系统的性能,但是成本太大。本设计使用Quartus II自带的FIFO宏模块,再配合DMA在很大程度上减轻了CPU资源占有率,与乒乓显存就“性价比”方面比较,FIFO较优。若要实现一些高端的应用,再考虑乒乓显存。

本设计触摸输入与显示的功能还未考虑进去,这也是液晶屏控制器需要设计不足之处,这部分的完善设计有待下一步研究。

[1]宋敏,应建华,刘艳丽,等.动态驱动LCD视频控制芯片的设计[J].华中科技大学学报:自然科学版,2004,32(1):82-86.

Song M,Ying J H,Liu Y L,etal.Design of dynamic driving LCD controller chip [J].JournalofHuazhongUniversityofScienceandTechnology:NaturalScienceEdition,2004,32(1):82-86.(in Chinese)

[2]苏维嘉,张澎.基于FPGA的 TFT LCD控制器的设计和实现[J].液晶与显示,2010,25(1):75-78.(in Chinese)

Su W J,Zhang P.Design and realization of the TFT-LCD controller based on FPGA [J].ChineseJournalofLiquid CrystalsandDisplays,2010,25(1):75-78.(in Chinese)

[3]白宗元,胡宝霞.基于 Nios II的SPOC中TFT LCD控制核的设计[J].计算机应用,2008,2(2):61-63.

Bai Z Y,Hu B X.Design of a TFT LCD controller core based on the SOPC of NiosII[J].ComputerApplications,2008,2(2):61-63.

[4]张燕忠,蔡妍艳.嵌入式Linux系统构建和移植若干共性技术研究[J].计算机测量与控制,2005,13(2):162-164.

Zhang Y Z,Cai Y Y.Study of some common technology on the design and transplantation of embed ded linux operating system [J].TransplantationofEmbeddedLinuxOperatingSystemComputerAutomatedMeasurement&Control,2005,13(2):162-164.(in Chinese)

[5]褚文奎,张凤鸣,樊晓光.嵌入式Linux系统实时性能测试研究[J].系统工程与电子技术,2007:29(8):1385-1388

Chu W K,Zhang F M,Fan X G.Measurement of real time performance of embedded Linux systems[J].Systems EngineeringandElectronics,2007:29(8):1385-1388.(in Chinese)

[6]付先成,邹雪城,雷鑑铭.FIFO电路在液晶显示控制器中的应用[J].华中科技大学学报:自然科学版,2006,34(4):8-10.

Fu X C,Zou X C,Lei J M.Application of FIFO circuit to liquid crystal display cont rollers[J].JournalofHuazhongUniversityofScienceandTechnology:NatureScienceEdition,2006,34(4):8-10.(in Chinese)

[7]向荣,陈祖希.基于 Nios II的LCD驱动IP核的设计[J].计算机工程,2008,34(5):246-247,259.

Xiang R,Chen Z X.Design of IP core for LCD driver based on Nios II[J].ComputerEngineering,2008,34(5):246-247,259.

[8]黄燕群,李利品,王爽英.基于FPGA的 OSD设计[J].液晶与显示,2010,25(3):429-433.

Huang Y Q,Li L P,Wang S Y.OSD design based on FPGA [J].ChineseJournalofLiquidCrystalsandDisplays,2010,25(3):429-433.(in Chinese)

[9]张雷,吴华夏,胡俊涛,等.一种基于FPGA的 OLED显示系统[J].液晶与显示,2011,26(4):538-543.

Zhang L,Wu H X,HU Jun-tao,etal.Display system of OLED based on FPGA [J].ChineseJournalofLiquid CrystalsandDisplays,2011,26(4):538-54.(in Chinese)

[10]王栩,李建中,王伟平.基于滑动窗口的数据流压缩技术及连续查询处理方法[J].计算机研究与发展,2004,41(10):1639-1644.

Wang X,Li J Z,Wang W P.Processing compressed sliding window continuous queries over data streams[J].JournalofComputerResearchandDevelopment,2004,41(10):1639-1644.(in Chinese)

SOPC design on LCD controller based on NiosII

SONG Yue1*,LU Jun-ping1,2,LEI Rui-ting1,CHEN Wei1,CHENG Bo1,2

(1.CollegeofElectronicsEngineering,DongguanUniversityofTechnology,Dongguan523808,China;2.SchoolofElectronicandInformationEngineering,SouthChinaUniversityof Technology,Guangzhou510640,China)

In order to realize SOPC controller design on TFT-LCD,IP core of TFT-LCD controller based on Nios II was designed by FPGA-EP4CE6F17C8and Verilog language.TFT-LCD controller was consisted of the Nios II soft-core processor,SDRAM controller,JTAG UART,LCD controller,Avalon bus for a full-color AT070TN84 TFT-LCD.Nios II soft-core processor was designed as core,IP cores such as SDRAM controller,TFT-LCD controller were connected to Nios II by Avalon bus,IP core design of TFT-LCD controller was mainly completed by such modules as the Avalon bus interface module,DMA module,FIFO module and the timing generator module.The color graphics display control wtih 800×480resolution,16bit color depth was achieved.Display experiment showed it was of stable,clear images,rich colors,no splash screen,wrong line and other phenomena,good visual effect.Design was of good configurability,reusability and portability.Practice proved that the SOPC design was effective.The design principle,control system simulation and experiment method,process were presented in the paper,relevant links of IP controller core design was mainly focused on at the same time.

Nios II;SOPC-IP;LCD controller;DMA

*通信联系人,E-mail:eda815@163.com

TP274;TM935

A

10.3788/YJYXS20142901.0048

2013-06-17;

2013-07-19.

国家自然科学重大基金项目 (No.10890095);国家自然科学基金科学仪器基础研究专款项目(No.11127508);东莞市2012年科技计划项目(No.2012108102040);东莞市2010年科技计划重点项目(No.201010814001)

宋跃 (1963-),男,湖南邵阳人,教授,研究方向为电路与系统、电子测量与仪器、嵌入式系统。E-mail:eda815@163.com