基于VHDL 实现的自动售货机芯片设计

2014-01-16刘锡锋朱刘宁

刘锡锋,朱刘宁

(1.江苏信息职业技术学院 江苏 无锡 214153;2.马鞍山职业技术学院 安徽 马鞍山 243031)

随着集成电路产业的迅速发展,集成电路芯片的规模越来越大,集成度越来越高,一块芯片上所实现的功能也越来越多,集成的元器件也动辄百万、千万计。对于这种大规模、超大规模集成电路的芯片设计,特别是在数字集成电路方面,采用计算机辅助设计和电子设计的智能自动化来进行集成电路设计已经是一种趋势[1]。VHDL、Verilog等硬件描述语言近年由于其在芯片设计自动化方面出色的表现被越来越多地应用在超大规模集成电路设计领域。用VHDL硬件描述语言进行芯片设计并不涉及底层电路具体电路结构,而只需要给出各单元功能描述和单元电路之间的连接关系,这种设计方法一方面使得设计者能够专注于顶层结构设计从而使芯片整体性能更优,另一方面由于通过语句描述来自动实现具体电路结构节省了电路设计的时间提高了设计效率[4]。同时由于生成的电路是自动生成的标准化电路,也提高了电路设计的正确性。

自动售货机是常用的街头自动贩卖设备,它的核心运作部件是一块集成电路控制芯片,由这块芯片来控制、判断商品的选择、买卖,货币辨别、交易和找零等工作。以往的自动售货机芯片对售卖商品的类型选择偏少,对投入货币的限制也较多,很多自动售货机仅仅能允许投入1元硬币。此外受芯片设计限制,相应的找零环节也不完善,有的甚至没有,这些问题对商品的售卖交易和商品价格的合理定位产生了一定的影响[5]。在做了需求分析的基础上,提出并设计了一种基于VHDL实现的自动售货机芯片设计。该芯片能够完成多种商品的售卖,允许多种纸质和硬币现金使用,能够完成多种货币的找零,对价格控制更加合理精确,各种售卖中可能发生的情况也考虑周全,并做了相应设计[6]。

1 总体设计

该售货机的主要要求是:投币可投10元、5元纸币和1元硬币。出售百事可乐、话梅、瓜子三种商品,可乐售价2元每瓶,话梅售价1元每包,瓜子2元5角(投币种类数目和出售商品数目可继续在程序中添加,这里只各以3种为例)。

整个程序总的输入有:投币(3输入端)、选择商品(3输入端)、时钟、执行按键一共8端输入。

总的输出有:总投入货币显示、选择商品现实(3端)、退币(1元硬币、5角硬币两端)、商品输出(三端)一共9端。

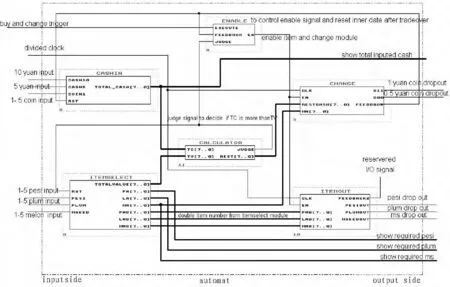

根据以上要求,整体设计共由6个子模块(6进程)和一个与非门构成。总体设计如图1所示。

2 各子模块设计

图1 设计总体结构图Fig.1 Structure diagram of the automat

1)货币投入和计算进程:该模块允许投入10元5元纸币,纸币上限为1,超过部分不计,(此外可以设定超过1给出1个讯号来关闭投币口来防止继续投币,本程序中未给出此讯号),1元硬币的上限为5个,超出部分不计。经过该模块处理,输出投入总货币数(以5角为一个单位)到下一进程。该模块有一个reset讯号,如reset为高电平则所有输入输出清零。以下为该子模块部分程序(总体程序较长,由于篇幅原因,下面只给出第一第二子程序的部分主要程序,如需要全部程序可向作者咨询)。

cashin:process(cash10,cash5,coin1,feedback)

variable c10t,c5t,c1t:integer range 0 to 255;

variable total_cash:integer range 0 to 255;

begin

if(cash10'event and cash10='1')then

if feedback='0'then

c10t:=c10t+20;

if(c10t>=20)then

c10t:=20;

end if;

else

c10t:=0;

end if;

end if;

。。。

2)物品选择进程:该模块输入部分为3个按钮,每按一次相应商品的按钮即选择商品数目加一,每种商品选择上限都是5,超过5将按5计算。输出7个讯号,3种商品各有1个显示输出,以显示给顾客选择的商品总数,3条按5角为一单位的商品讯号输出给物品送出进程使用。还有1个选购商品总价值输出。此模块也有1个reset讯号,如reset为高电平则所有输入输出清零。

itemselect:process(judge,pesi,plum,mseed)

variable pnumber,lnumber,mnumber:integer range 0 to 255;

variable pnumber2,lnumber2,mnumber2:integer range 0 to 255;

variable pc,lc,mc:integer range 0 to 255;

variable tv:integer range 0 to 255;

begin

if(pesi'event and pesi='1')then

if judge='0'then

pnumber:=pnumber+1;pnumber2:=pnumber2+2;pc:=pc+4;

if(pc>=20)then

pnumber:=5;pnumber2:=10;pc:=20;

end if;

else

pnumber:=0;pnumber2:=0;pc:=0;

end if;

end if;

。。。

3)剩余货币计算进程:该模块将上2个进程的总货币数和总商品价值数相减计算出剩余货币数输出给找零进程使用,同时判断总货币数是否小于总商品价值,如果是给出高电平讯号,如果否则给出低电平讯号。该讯号送给执行使能进程使用同时作为物品选择进程的复位端使用。

4)执行使能进程:该进程有3个输入,如果剩余货币判断讯号为低电平同时找零进程给出的反馈讯号也为低电平,此时如果执行按键按动一下,则输出高电平使能讯号,且只要剩余货币判断讯号和反馈讯号不变,则一直输出高电平。如上述2个讯号有任意一个为低电平,则输出改为低电平。

5)找零进程:该进程只有在使能讯号为高电平时方有效,如使能讯号为低电平,则所有输出清零。该进程将输入的剩余货币转化成1元的硬币的脉冲讯号输出,每次脉冲对应找出1个1元硬币,同时根据是否输入单数的瓜子来判断是否需要找出5角硬币。在找零完成后,同时大于5个脉冲时间 (为了保证在找零脉冲小于5个脉冲时间时商品输出时间足够)后给出高电平反馈讯号。该讯号供给剩余货币计算进程使用,同时作为货币投入和计算进程的复位端使用。

6)商品输出进程:该进程只有在使能讯号为高电平时方有效,如使能讯号为低电平,则所有输出清零。该进程将物品选择进程给出的商品数目按脉冲输出。每次脉冲对应出1件商品。同时当所有商品输出完成后给出高电平反馈讯号(此讯号在本程序中保留,不起作用)。

3 系统仿真

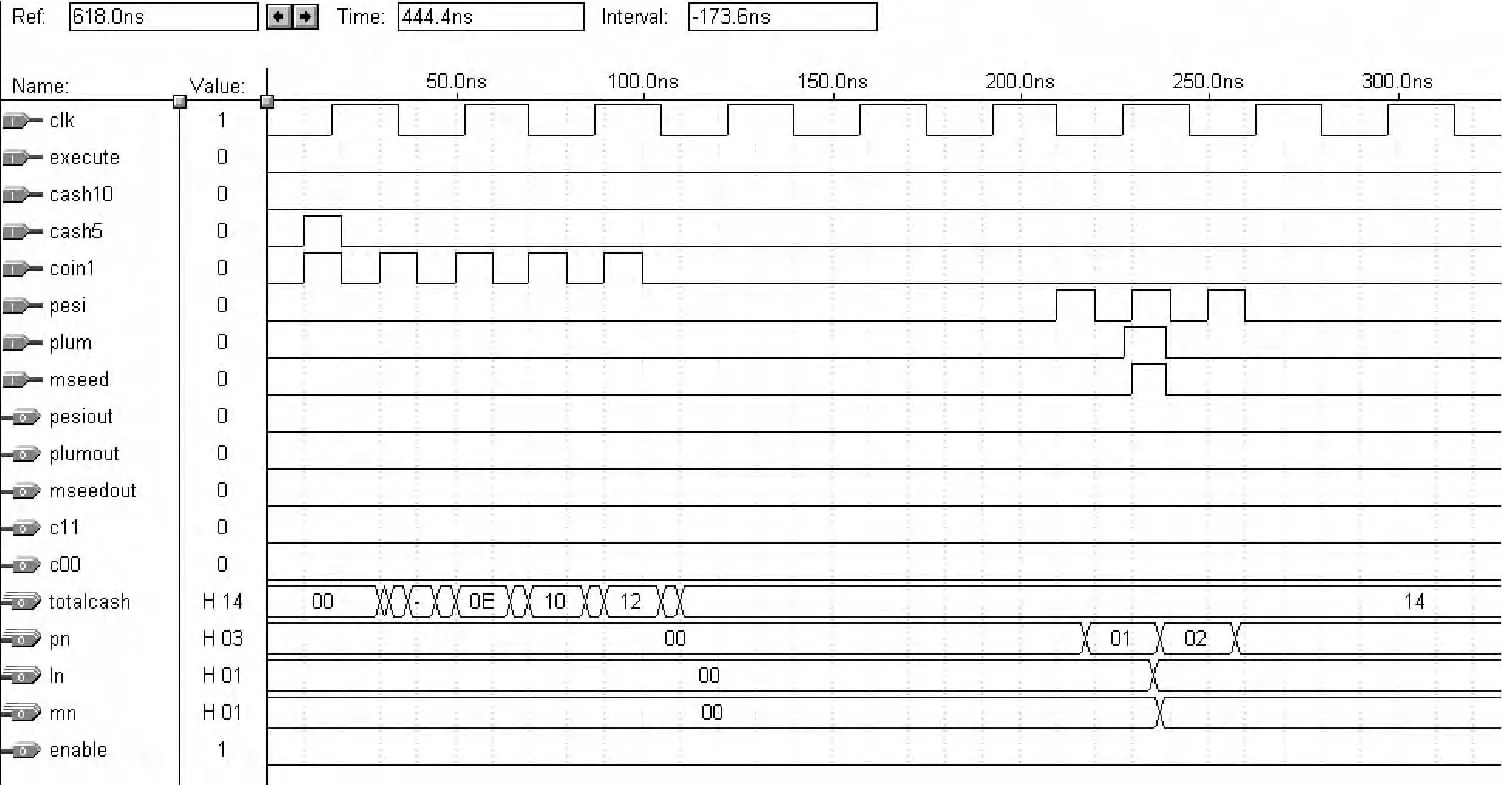

为了验证该设计的功能,对该设计进行了仿真分析。图2是该设计在MAXPLUS II下进行仿真的波形图,该仿真中采用周期为35 ns的时钟。

图2 仿真测试结果图Fig.2 Result chart of simulation of automat

上图中c11为1元硬币输出,c00为5毛硬币输出。可以看到当输入商品、1元硬币超过5个时仍以5计算。当总选择商品价值超过投入的总货币数时,程序自动将选择商品数目清零,但输入的货币不变,只有选择商品正确以后按了执行键,机器才按照给定数目输出商品和找零,当全部完成后将货币和商品清零。

4 结论

由仿真结果分析,设计满足要求,能够完成多种商品的售卖,允许多种纸质和硬币现金使用,能够完成多种货币的找零,对价格控制更加合理精确,执行售卖功能全面,可以满足实际生产使用。

[1]夏宇闻.Verilog数字系统设计教程[M].3版,北京:北京航空航天大学出版社,2013.

[2]杨志忠.数字电子技术[M].北京:高等教育出版社,2008.

[3]阎石.数字电子技术基础 [M].北京:高等教育出版社,2006.

[4]韩雁,洪慧.集成电路设计制造中EDA工具实用教程[M].杭州:浙江大学出版社,2007.

[5]刘明业.集成电路/计算机硬件描述语言VHDL高等教材[M].北京:清华大学出版社,2003.

[6]姜雪松.硬件描述语言VHDL教程[M].西安:西安交通大学出版社,2004.