基于FPGA IEC61850-9-2硬件解码器设计

2014-01-15黄其培李兴武

黄其培,匡 彪,李兴武

(昆明船舶设备研究中心 云南 昆明 650051)

而今互联网时代,随着社会经济的不断发展,新技术不断涌现,电力已经成为人们的必需品,变电站的数字化已成为变电站发展的趋势。数字化变电站采用IEC61850标准进行建模,在IEC61850标准的统一规约下,站内设备间传送的信息必须按该标准所规定的相关协议进行编解码[1]。由此可知,依据IEC61850标准对站内流动信息的编解码在数字变电站建设中有着不可替代的地位。研究编解码的快速实现方法具有较高应用、学术价值。

目前国内数字站数据采集与传输中,IEC61850-9-1、9-2都有一定的应用,由9-1帧格式固定,编解码方面软硬件都有实现,对于9-2帧结构的不确定性,其编解码实现较为复杂,目前主要是采用软件形式实现。随着网络管理功能,交换机技术的迅速发展和其成本的降低,9-2相对于9-1在安装灵活、便于实现跨间隔保护及光纤连接简洁等方面的优势越发突出,势必9-2将得到更多的应用,当前关于9-2的研究,主要是通过ARM芯片和软件来实现,由于该方法处理速度较慢,当随着采样率的提高,其性能未能改善,不能很好的满足系统实时性要求,不利于系统工作的稳定性,因此,对一种更快速的实现方法的研究迫在眉睫。

基于速度、实时性的考虑,本文提出了采用FPGA实现9-2数据帧快速解码的设计方案,通过软件仿真和在线数据测试,满足了设计要求,为后期的进一步数据处理提供了可靠保证。

1 IEC61850-9-2标准

IEC61850-9-2标准采用以太网模式,面向任意间隔,通信通道的采样数据传输形式可任意组合,便于实现跨间隔的二次功能的采样值的数据传送[2]。9-2采样值应用协议数据单元(APDU)采用与基本编码规则(BER)相关的ASN.1语法对通过ISO/IEC8802-3传输的采样值信息进行编码,则基于IEC61850-9-2标准的APDU帧格式如图1所示[3]。

2 设计的功能划分和实现方案

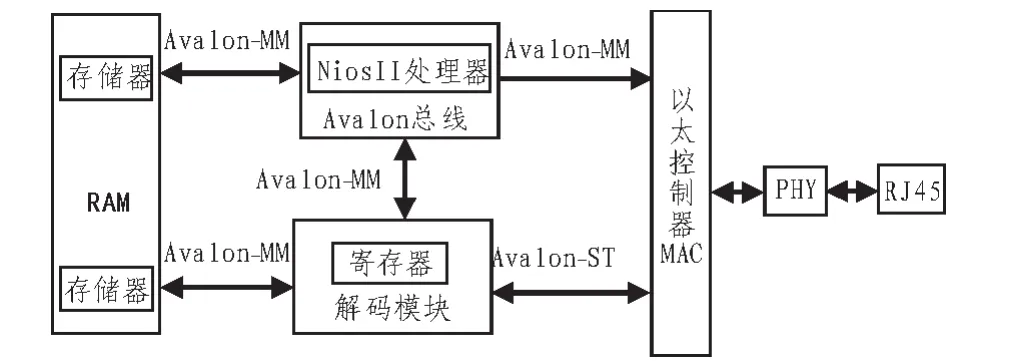

本文设计主要分为数据解码和网络传输两个部分实现,实现过程采用模块化设计,其功能模块包括存储器、解码模块、网络传输模块。其中解码模块中设有寄存器,CPU可以通过访问相应的寄存器实现对解码模块的设置和状态信息的读取。功能模块框图如图2所示。

由图可知,当系统开始工作时,CPU通过Avalon总线接口对存储器、解码模块和以太控制器进行初始化设置,解码模块与网络传输模块之间采用流控制模式传输,使得解码模块可以在不受CPU干预的情况下进行解码[4]。在解码过程中,解码模块从网络上获取数据,进行实时解码,以实现帧结构数据类分离,并对数据进行分类存储,用户可以随时访问解码模块寄存器和存储器,以获取自己关心的信息内容(如解码状态、APDU配置信息、采样速率、采样值序列等)。

图1 基于IEC61850-9-2的APDU帧格式Fig.1 The form of APDU of IEC61850-9-2

图2 系统功能框图Fig.2 Function diagram of system

研究工作的实现分两个阶段:1)针对具体的9-2数据帧的结构特点进行了解码模块设计和仿真,解码模块仿真采用离线形式,即仿真时所解码的数据帧源于FPGA片上RAM(由CPU初始化)。通过对解码模块的仿真,验证了其功能上的正确性。2)在实现解码功能的基础上,对解码模块进行了连网测试,验证了整个解码系统的正确性和实用性。

3 解码模块

解码模块运用Verilog HDL进行代码编写,其设计的重、难点在于Decode_FSM和TLV_FSM状态机的编写。状态机采用Mealy型设计;对于状态常量,Decode_FSM采用独热码,TLV_FSM采用二进制编码[5]。

3.1 Decode_FSM状态机

Decode_FSM状态机由14个状态常量构成,其状态转移图如图3所示。其中IDLE状态是状态机处于等待解码状态;READ状态是状态机使能Avalon主端口读操作状态;在WAIT_READ状态,状态机将从Avalon总线捕获读返回的数据,并对数据进行过滤条件的判断;在TLV_TAG状态,主要实现对APDU中所包含的数据类型进行解码,并对APDU完整性进行判断,有误则终止解码,同时转入IDLE状态;DATA_CLASSIFICATION状态下,依据Flag_gen输出标志位来完成下一个状态的转移;WRITE_ETH和WAIT_WRITE_ETH状态用于实现以太配置信息的存储;WRITE_APDU和WAIT_WRITE_APDU用于实现APDU配置信息的存储;WRITE_ASDU和WAIT_WRITE_ASDU状态用于实现ASDU配置信息的存储;WRITE_SAMPDATA和WAIT_WRITE_SAMPDATA用于实现采样值序列的存储;当完成一帧数据的解码,进入DONE。

3.2 TLV_FSM状态机

TLV_FSM状态机共包括5个状态常量,其状态转移图如图4所示。TLV_IDLE状态是等待TLV编码的长度域(L域)解码,没有进行解码将一直处于该状态;TLV_STRUCT_LENGTH状态主要是对APDU中结构类型数据的L域进行解码;TLV_N_STRUCT_LENGTH_JUDGE状态用于实现对基本类型数据的L域编码进行类型判断;TLV_N_STRUCT_DEFINITE_LONG用于实现基本类型数据的L域编码为长定长型的解码;TLV_INDEFINITE用于实现L域编码为非定长型的解析。

3.3 软件仿真

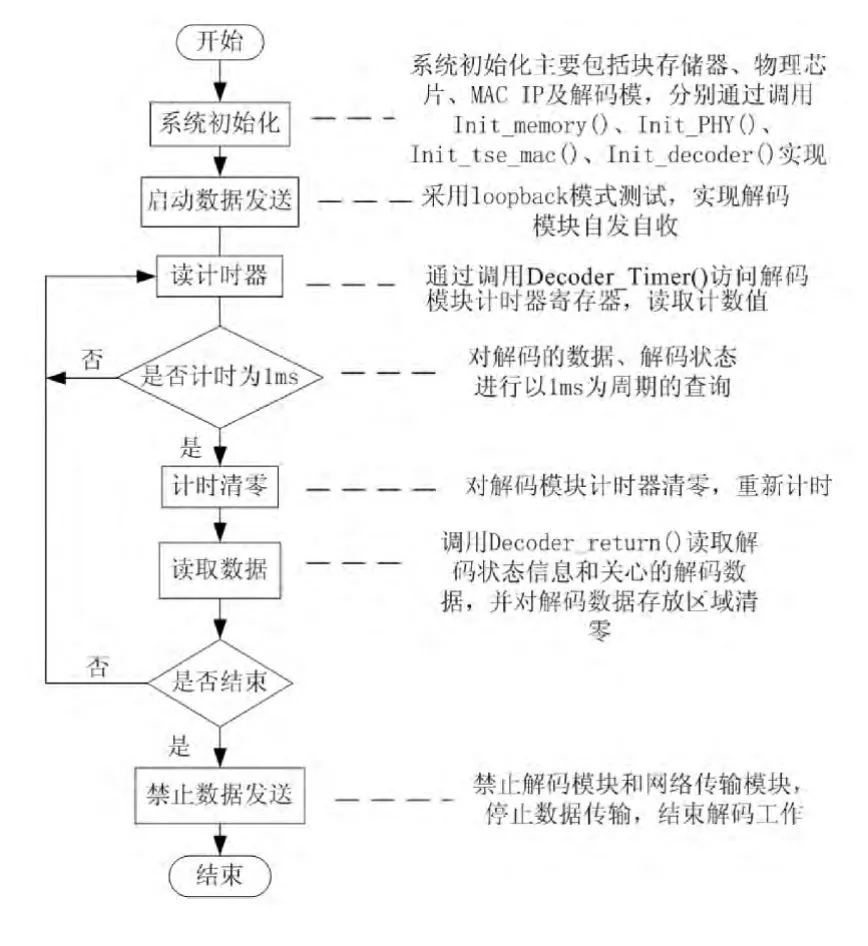

通过SOPC builder[6]构建Nios系统,对解码模块进行软件仿真,软件仿真流程如图5所示。图6为存放于RAM中用于仿真的待解码的一帧数据,仿真结果如图7。通过两图对比可知,解码模块很好的实现了数据帧的分离解析,表明了解码的正确性,并在CPU工作频率为50 MHz时,解码一帧557 Bytes的9-2数据帧所花费的时间约为54 μs。

4 网络传输模块

运用SOPC builder构建了网络传输模块,解码模块与网络模块采用Avalon-ST接口连接,在LOOPBACK模式下,对解码模块进行了连网测试,测试数据流向图如图8所示。仿真测试数据源来自FPGA片上RAM,其中包括完整的且符合过滤条件的数据帧(下面称为正确的数据帧)、不完整的数据帧以及不符合过滤条件的数据帧。图9为RAM中用于仿真测试的数据源。在测试过程中,为了对解码模块在数据过滤和解码方面的性能进行测试,这里采用具有不同过滤条件的20帧数据用于测试,软件测试流程图如图10所示。

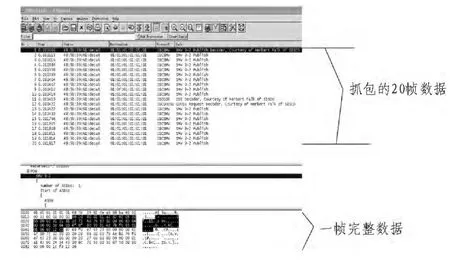

在测试过程中,从数据发送情况看,这里利用MMS Ethernet抓包软件在PC机端对发送的数据进行抓包,抓包结果如图11所示。由抓包结果表明了网络模块成功发送了20帧数据。

图3 Decode_FSM状态机状态转移图Fig.3 Status tranfer diagram of Decode_FSM

图4 TLV_FSM状态机状态转移图Fig.4 Status tranfer diagram of TLV_FSM

图5 解码模块的软件验证流程图Fig.5 Flow chart of software checking of decoding module

在loopback模式下,发送的数据从网络(dp83848网络芯片)环回到网络模块接收端,同时解码模块将对接收到得数据进行检测分析。解码测试结果通过在Nios II IDE中查看变量值,清楚的反应了整个解码过程。测试结果如图12所示。

图6 待解码9-2数据帧Fig.6 Encoded data of 9-2 frame

从变量查看结果可知,网络接收端收到了来自网络的20帧数据,并传送给了解码模块进行检测,其中有8帧正确的数据帧、2帧非9-2数据帧及10帧错误的数据帧。这里对非9-2数据帧不做分析且丢弃;对于错误的数据帧(1帧MAC地址不符合过滤条件、1帧不符合APPID过滤条件、1帧APDU配置信息有误以及7帧ASDU出错)分析后,也选择丢弃;而对于正确的数据,给出了每一帧数据解码情况,变量数组中每一个组元对应一个数据帧,其中包括:帧长度、一帧数据所含ASDU数、各字段数据存放的基地址以及各字段数据的长度值。

最后,对解码模块进行了589815帧数据的测试,测试结果如图13,从结果可知,解码系统能够稳定可靠的工作,并能给出正确的结果,满足设计要求。

5 结 论

图7 9-2数据帧解码信息Fig.7 Decoding data of 9-2 frame

图8 Loopback测试数据流向图Fig.8 The direction diagram of shift tested data under loopback mode

图9 数据发送区待解码的数据帧Fig.9 Encoding data frame in sending area of storage

图10 解码系统验证流程Fig.10 Flow chart of checking of decoding system

图11 发送数据抓包结果Fig.11 The case of intercpeting frame for sending data

图12 20帧数据解码结果Fig.12 The decoding result of 20 frame

图13 在线测试结果Fig.13 The decoding result of online data

基于IEC6150-9-2数据帧解码实时性考虑,本设计采用FPGA实现了快速解码。通过解码模块嵌入Nios II的SOPC系统,对模块进行了软件仿真和在线数据测试,验证了方案的正确性和实用性,很好的实现了对9-2数据帧的筛选检测与帧结构数据类分离存储,为后期进一步数据处理提供可靠保证,满足了实时性的要求,并在系统工作时钟为50 MHz,测得解码一帧557 Bytes的9-2数据帧的时间约为54 μs。本设计所研究的IEC61850-9-2数据帧解码模块,主要是为了能够很方便的集成在数字化变电站的IED中,成为其设备的一部分,以此实现设备间实时通信。

[1]刘东,张沛超,李晓露.面向对象的电力系统自动化[M].北京:中国电力出版社,2009.

[2]IEC.Communication networks and systems in substations,Part 9-2:Specific Communication Service Mapping(SCSM)Sample values over ISO/IEC 8802-3 link[S].2006.

[3]朱超,黄灿,梅军,等.基于FPGA与ARM的智能合并单元设计[J].电网技术,2011(6):13.ZHU Chao,HUANG Can,MEI Jun,et al.Design of smart merging unit based on FPGA and ARM[J].Power System Technology,2011(6):13.

[4]徐欣,于红旗,易凡,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2004.

[5]夏宇闻.Verilog数字信号系统设计教程[M].北京:北京航空航天大学出版社,2003.

[6]Altera Corporation.Nios II Software Developer’s Handbook[EB/OL].[2013-11-08].http://wenku.baidu.com/link?url=519 Qb6uLjyOmo-MlVkrqIYzVqsjy2b0uR-KJp7JwErW_ycQG pbpSI8pjYmFUWDmkD5rhSE4x4VeuyHYtV-wbj89erko_0Kt_wTg4zrPpKmS.