在数字逻辑课程教学中引入VHDL的方法

2014-01-07沈祖斌邹光毅

沈祖斌 邹光毅

(江汉大学数学与计算机科学学院,湖北 武汉430056)

1 存在的问题

目前国内数字逻辑课程的教学内容多是基于SSI、MSI等器件进行分析和设计,采用的是经典的数字逻辑设计方法,即用真值表、卡诺图、状态转换图、状态转换表、状态方程、时序图、逻辑图和逻辑函数表达式等方法,来分析和设计数字逻辑系统。显然,对于较复杂的数字系统,因其输入变量数、输出函数变量数和状态数的急剧增加,再使用上述这种传统方法进行分析和设计难以适用,甚至根本无法进行。数字逻辑课程的实验环节也是基于标准SSI,MSI芯片的所谓硬实验台实验室(Hardware-based Laboratory),这种实现台不易做成开放性,实验准备,实验内容和实验课安排都不灵活,实验内容和效果也受到所供SSI,MSI芯片的限制。如今,数字化的概念已深入到各个领域,几乎绝大多数系统已不是简单几个逻辑变量就能完全描述的。然而目前在专门讲授数字系统设计基础理论和方法的数字逻辑课程中,绝大多数高校仍然是沿用了几十年不变的老方法,显然已远远落后于时代的要求,必须加以改革创新。

2 引进VHDL语言的方法

VHDL的方法克服了传统方法的弱点,与传统方法相比有几处根本优点,设计者可以在VHDL描述模型建立之后马上用仿真手段来验证系统功能是否满足要求。这种方法还可以免去传统方法的许多繁杂的试凑等耗时劳动(设计瓶颈),因而减少设计时间,降低设计难度,避免了由于人工试凑设计常容易发生的错误。利用各种EDA工具,可自动的将一个可综合的设计在给定的具体器件上进行门级实现。而且,用这种方法系统整体指标往往容易实现,而传统的方法则不然。这种方法其主要设计文件是用VHDL语言编写的源程序,而不是电路原理图,显然传统硬件电路设计最后形成的主要文件是电路原理图,它与设计的器件和技术有关,不易设计文档的复用。用VHDL语言设计系统硬件电路,主要设计文件是用VHDL语言编写的源程序,以此作为归纳文件有很多好处:首先,资料量小,便于保存;其次是可继承性好,即设计其它硬件电路时可以调用文件中的某些库、进程和过程等描述某些局部硬件电路的程序;第三是阅读方便,很容易在程序中看出某一硬件电路的工作原理和逻辑关系,而阅读电路原理图,推知其工作原理都需要较多的硬件知识和经验,而且看起来也不够一目了然。VHDL还有一个重要的特点就是设计描述与器件无关(without referenec to specific hardware),显然这是基于SSI、MSI等器件进行分析和设计无法做到的,设计者能专注其设计,而且在EDA综合工具的配合下支持自顶向下的设计。

采用VHDL的方法,在实验环境上也把基于硬件的实验室改变成基于软件的实验室(Software-based Laboratory)即软实验台,直接在VHDL仿真器中验证实验结果的正确性,根本克服了硬实验台的不足,易于实现实验的开放性和网络教学模式。

VHDL的方法是顺应迅速发展的通讯技术、电子测量技术、自动化控制等技术的需要而发展起来的,它使硬件软件化变为现实,使大规模和超大规模集成电路的设计向标准化、自动化的方向迈进了一大步。无疑,传统的设计方法已经远远落后,国内电子行业已逐渐将VHDL硬件描述语言应用于电子系统设计中。为了避免我们的教学内容与电子技术发展脱节,增强人才的竞争能力,适应市场需要,将VHDL硬件描述语言引入数字逻辑的教学和实验中,逐步对旧的教学模式和教学内容加以改革,势在必行,也是时代的要求和科技发展的必然结果。

3 举例说明采用VHDL方法的风格和特点

VHDL语言是目前广泛流行的硬件描述语言之一,它起源于美国国防部超高速集成电路计划,计划公布后受到业界的普遍欢迎。1987年12月被IEEE正式批准为标准的硬件描述语言,并于1993年公布了修改后的IEEE最新标准。VHDL支持结构化的开发设计,因此一个大型的数字系统可以分成较小的子系统,许多人可在不同的子系统中同时进行开发工作。VHDL是通过元件例化语句来实现这一功能的。和其它高级语言一样,VHDL是一种强类型语言,这使设计中的许多错误易于发现。VHDL允许设计者在不同的抽象层次里对系统进行行为描述及结构描述。VHDL有三种主要的建模描述风格:

算法描述(Algorithmic):即用顺序语句来描述输入输出对应关系的算法,这种描述方式最初往往与实现硬件无关。

数据流描述(Dataflow):即用一组并行语句来描述数据在寄存器之间流动的建模方式。这种方式与实际硬件实际存在某种对应关系。

结构描述风格 (Structural):这是一种与硬件结构最近的描述方式,它通过文件的例化语句来实现。

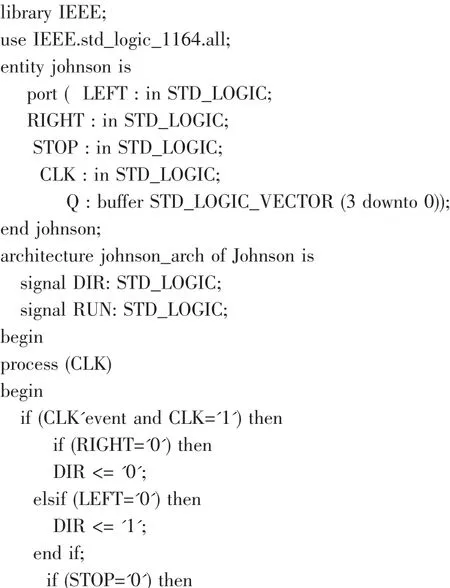

下面用一个实例来说明采用VHDL语言设计一个四位可控的Johnson计数器,从中可以领略一下采用VHDL方法的风格和特点,此例所反映的设计过程也是笔者所指的软实验台所包含的具体内容。设计模块端口信号有:LEPT,左移控制;RIGHT,右移控制;STOP,停止计数控制;CLK,时钟输入端,Q3-Q0,计数器输出端。设计采用VHDL输入方式。该设计的VHDL代码如下:

从上面的VHDL的设计代码可见:VHDL的设计文档由三大部分组成,即库的声明,端口说明和结构体设计描述。其中端口说明清晰的反映了所设计器件的输入输出性质,在结构体设计描述中也清楚的描述了器件所完成的逻辑功能。这是传统的采用SSI,MSI等标准规格器件设计所没有的优点。

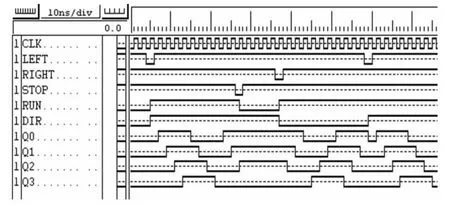

图1 设计实例功能仿真图

用VHDL仿真器验证设计的正确性。参见图1:设计实例功能仿真图。

4 结论

随着CMOS技术的日趋成熟和EDA技术的产生和逐步完善,给数字系统的分析和设计方法带来巨大的变革,EDA业界出现了将整个系统集成一个片IC芯片上的系统芯片 (System on a Chip,简称SOC)或称片上系统的概念。系统芯片SOC与传统集成电路IC芯片的设计思想是不同的,SOC是微电子设计领域的一场革命。它和集成电路的关系与当时集成电路与分离元器件的关系类似,其对微电子技术的推动作用不亚于自50年代末快速发展起来的集成电路技术。SOC是从整个系统的角度出发,把处理机制、模型算法、芯片结构、各层次电路直至器件的设计紧密结合起来,在单个(或少数几个)芯片上完成整个系统的功能。它的设计必须采用VHDL的方法才能实现。在数字逻辑课程教学和实验中,在向学生讲授最基本的数字系统概念和方法时就引入VHDL的方法,其意义和目的也在于此。笔者并不赞成把数字逻辑和VHDL程序设计作为两门课程分开来讲授,尽管许多高校和教材都是这样设计的。

[1]M.Morris Mano,etc.逻辑与计算机设计基础[M].北京:机械工业出版社,2011.

[2]林明权,等,编.VHDL数字控制系统设计范例[M].北京:电子工业出版社,2003.

[3]Mark Zwolinski.Digital System Design with VHDL[M].USA:Pearson Education Limited,2000.

[4]欧阳星明,等,编.数字逻辑[M].武汉:华中科技大学出版社,2009.