基于有限元方法的ARM11核心板信号完整性分析

2013-12-29吴明赞

沈 敏,吴明赞,李 竹

(南京理工大学自动化学院,南京210094)

随着微处理器内部时钟频率的迅速提高、上升和下降时间的缩短,必须对其进行信号完整性分析,否则可能导致系统的可靠性不高,甚至无法正常工作[1]。信号完整性问题主要包括串扰、地弹、延时、振铃、反射等[2]。可以运用传输线理论对 FPGA、DSP等系统进行信号完整性仿真分析[3-6]。文章拟用有限元方法在反射和串扰方面对ARM11核心板进行信号完整性仿真分析。

1 信号完整性原理概述

核心板中ARM芯片时钟频率已经达到533 MHz~667 MHz,并且与DDR RAM等芯片进行高速信号传输;由于CPU和DDR RAM都是BGA封装的芯片,在引脚扇出时就需要使用大量的过孔;另外核心板的布线密度很高。所以必须对核心板进行信号完整性分析。ARM11核心板布线如图1所示。

图1 ARM11核心板图

1.1 反射原理

当信号沿互连线传播时所受到的瞬态阻抗发生变化,一部分信号将被反射,另一部分发生失真并继续传播下去[1]。反射和失真使信号质量下降。这是单一网络中多数信号完整性问题产生的主要原因。

设计互连线的目的是尽量保持信号受到的阻抗恒定,因此在布线时要尽量减少拐角和使用过孔。当传输线时延大于信号上升时间的20%时,可以通过端接电阻来减小噪声[7]。点对点拓扑结构常用的端接方法为源端串联端接和远端并联端接。源端阻抗与传输线特性阻抗相匹配,即源端串联端接,这时传输线的电压为驱动电压的一半,在负载处发生全反射时,接收端的电压正好为驱动电压。终端阻抗与传输线特性阻抗相匹配,即远端并联端接,这时接收端的反射系数为0,接受端电压等于驱动电压。

1.2 串扰原理

串扰是指有害信号从一个网络转移到相邻网络。通常把噪声源所在的网络称为动态网络,而把会有噪声产生的网络称为静态网络。静态网络中距离源端最近的一端称为近端,而离源端最远的一端称为远端。系统中两条网络之间的容性耦合和感性耦合是引起串扰的两个重要原因。

减小串扰的设计特点包括:增加信号路径之间的间距;用平面作为返回路径;使耦合长度尽量短;在带状线层布线;减小信号路径的特性阻抗;使用介电常数较低的叠层;使用两端和整条线上有短路过孔的防护布线[8-9]。对系统级仿真来说,在串扰分析中只包括静态线两边相邻导线产生的噪声就已经足够了,这些噪声为紧耦合总线中串扰的95%。

2 信号完整性仿真

2.1 仿真软件介绍

Ansoft SIwave采用全波有限元算法,是一个精确的整板级电磁场全波分析工具。它可以仿真信号线与供电板间的噪声耦合、传输延迟、过冲和下冲、反射和振铃等时域效应。提供了与当前业界主流的PCB Layout工具之间方便快捷的接口。

2.2 仿真模型

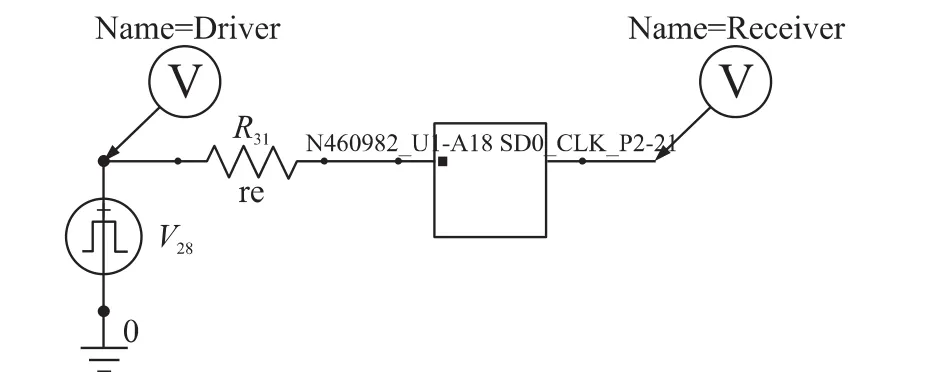

在Ansoft Designer中建立反射仿真模型,如图2所示。其中,电压源设定的参数如下,幅值是3.3 V,上升和下降时间是0.5 ns,脉冲宽度是4.5 ns,时钟周期是10 ns。电阻R31设定为变量,初始值取0。二端口网络是信号线的SIW模型。电压探头Driver和Receiver分别用来测量源端电压和接收端电压。

图2 反射仿真模型

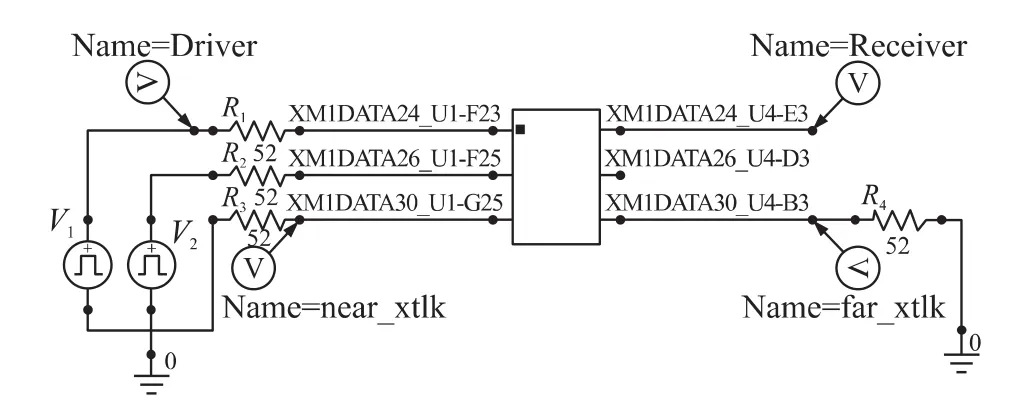

在Ansoft Designer中建立串扰仿真模型,如图3所示。其中,电压源加在动态线上,R1、R2、R3、R4值取信号线的特性阻抗,六端口网络是3条相邻信号线的SIW模型,电压探头Driver和Receiver分别测量动态线的源端电压和接收端电压,电压探头near_xtlk和far_xtlk分别测量静态线的近端串扰电压和远端串扰电压。

图3 串扰仿真模型

3 仿真结果及分析

3.1 仿真结果

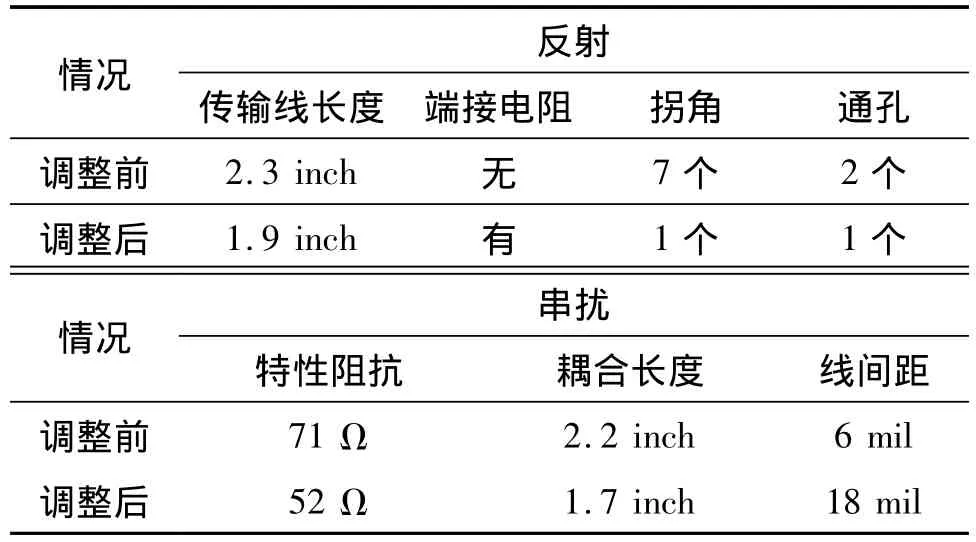

在反射和串扰仿真时,以数据线XM1_DATA30为例进行阐述。分别对调整前后布线进行仿真,调整如表1所示。其中,信号线的线宽为6 mil。

表1 反射和串扰调整情况

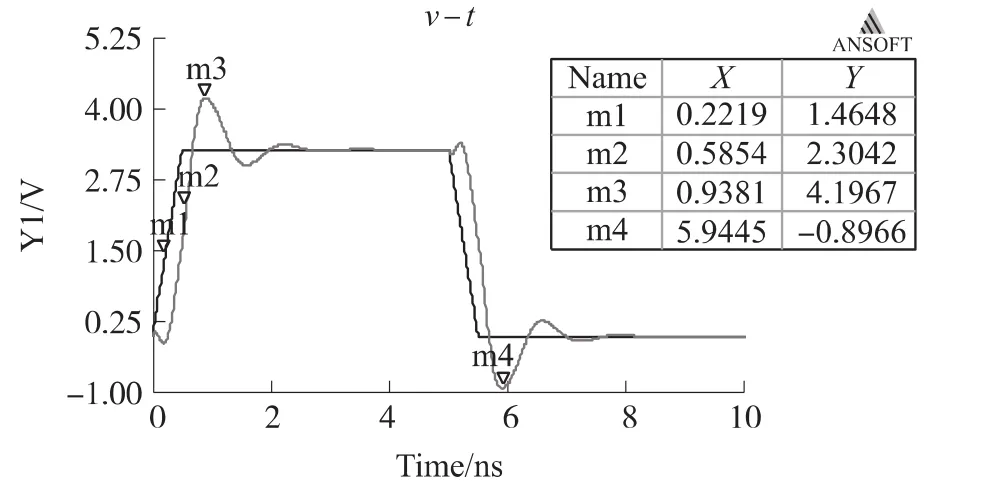

图4 调整前反射模型仿真波形图

反射仿真时,网络XM1_DATA30两端分别接的是CPU和DDR RAM,首先在Ansoft SIwave中对该数据线进行S参数抽取,并在Ansoft Designer中添加其SIwave模型。调整前网络SD0_CLK的反射模型仿真波形如图4所示。由于网络SD0_CLK的特性阻抗约为50 Ω,调整时在源端串联50 Ω的电阻,对串联电阻后的数据线XM1_DATA30重新建立SI-wave模型,调整后网络SD0_CLK的反射模型仿真波形如图5所示。

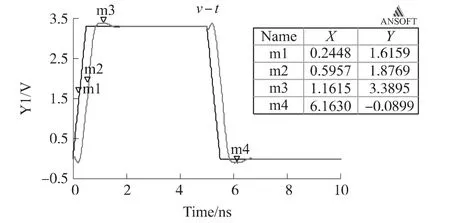

图5 调整后反射模型仿真波形图

对网络XM1_DATA30源端串联的电阻值进行优化,反射仿真模型中的电阻R31的参数re在0至10 Ω间取值,步进为2 Ω,然后在Ansoft Designer中优化参数re,发现将端接电阻设置为58 Ω时效果最好。

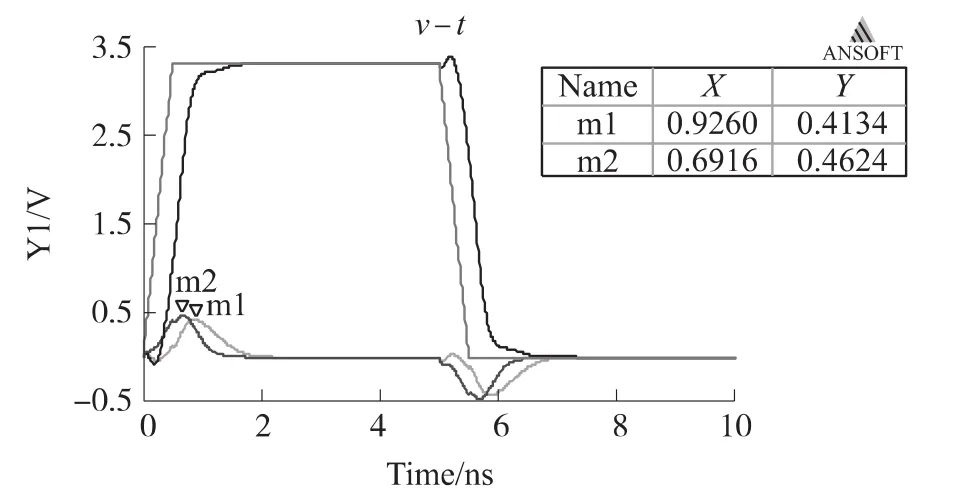

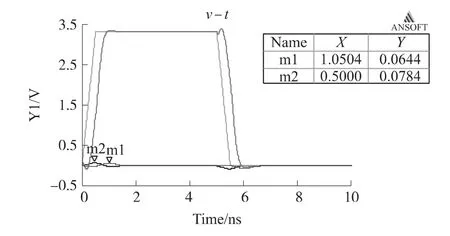

串扰仿真时,以数据线XM1_DATA30作为静态线,以相邻数据线XM1_DATA24和XM1_DATA26作为动态线,这3条数据线两端都分别接CPU和DDR RAM,首先在Ansoft SIwave中分别对调整前后的3条数据线进行S参数抽取,并在Ansoft Designer中添加其SIwave模型。对调整前网络仿真时,取R1~R4为71 Ω,调整前串扰模型仿真波形如图6所示。对调整后网络仿真时,取R1~R4为52 Ω,调整后串扰模型仿真波形如图7所示。

图6 调整前串扰模型仿真波形图

图7 调整后串扰模型仿真波形图

3.2 仿真结果比较分析

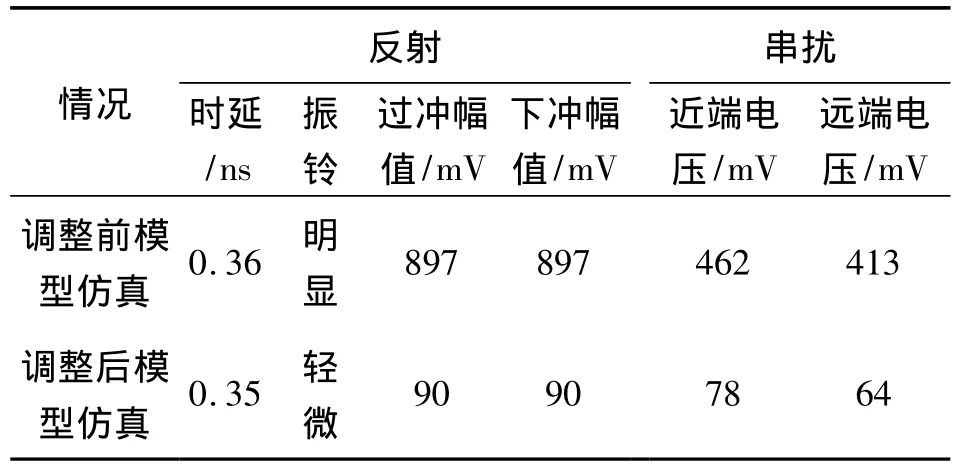

由于文章篇幅有限,文中仅列出少量的仿真结果进行比较,其他未列出仿真结果也是如此的,下面将3.1中的图4、5、6、7的反射和串扰仿真结果进行比较,如表2所示。

表2 反射和串扰仿真结果比较

分析反射参数,网络SD0_CLK的传输线时延大于信号上升时间的20%(0.1 ns),调整前网络SD0_CLK的仿真结果中振铃比较严重,过冲和下冲幅值达到驱动电压的27%,不符合要求。经过源端串联电阻后,振铃噪声就不是很大,接收端电压的过冲和下冲幅值都下降到驱动电压的2.7%,被控制在驱动电压的10%(330 mV)以内,因此,反射噪声得到了有效控制。

分析串扰参数,网络XM1_DATA30在调整前近端串扰电压和远端串扰电压达到驱动电压的14%,不符合要求。把传输线的特性阻抗和耦合长度减小,将线间距扩大到3倍的线宽后,近端和远端串扰电压为驱动电压的2.4%,被控制在驱动电压的5%(165 mV)以内,因此,串扰噪声得到有效控制。

4 结束语

文章运用有限元方法对ARM11核心板的信号完整性问题进行仿真和分析,主要从反射和串扰两方面入手。为了削弱反射噪声对接收端电压的影响,减小传输线的长度,减少拐角和通孔的个数,并且在源端串联电阻,最终使得反射噪声符合要求。为了削弱临近传输线对本线路近端和远端串扰的影响,减小特性阻抗,减小耦合长度,把线间距扩大到线宽的3倍,最终使得串扰噪声符合要求。所以,建立的有限元模型比较正确。而且用该模型对高速电路板信号完整性仿真所得的结果与理论一致。

文章的不足之处在于仿真时没有考虑驱动和负载阻抗的影响,仿真模型还需进一步改善;此外,还需要对延时和地弹等信号完整性问题作进一步的研究分析。

[1]Eric Bogatin著.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2005.

[2]Bogatin E.Essential Principles of Signal Integrity[J].Microwave Magazine,2011,12(5):34-41.

[3]李聪,张国贺,陈宝国.基于HyperLynx的DSP系统信号完整性仿真与改进[J].战术导弹技术,2011(4):110-116.

[4]Piccoli L B,Vargas F L.Signal Integrity Enhancement in Digital Circuits[J].Design and Test of Computers,2010,25(5):452-461.

[5]Jun Fan,Xiaoning Ye,Jingook Kim.Signal integrity Design for Hign-Speed Digital Circuits:Progress and Directions[J].Electronmagnetec Compatibility,2010,52(2):392-440.

[6]吴超,吴明赞,李竹.基于Hyperlynx的变电站状态监测无线节点信号完整性仿真分析[J].电子器件,2012,35(2):173-176.

[7]白红蕊,马秀荣,白媛.高速采集系统的时钟端接设计与仿真[J].电子器件,2012,35(2):158-162.

[8]郭桂林,李文钧.RFID系统的串扰分析及消除[J].电子器件,2012,35(1):99-102.

[9]曾爱凤,王海鹏.板级互连线的串扰规律研究与仿真[J].电子测量技术,2010,33(8):9-12.