一种快速升压的片上电荷泵电路设计

2013-12-29翟艳男程继航汤艳坤石静苑

翟艳男,程继航,汤艳坤,石静苑,焦 阳

(空军航空大学,长春130022)

随着集成电路的迅速发展,各种器件对电源的要求也在不断提高。片上电荷泵作为一种内部电源成为研究热点[1-4],它被应用于需要高压的领域,如串口通信电路、EEPROM、动态随机存储器等等。例如,在EEPROM中,电荷泵用于对悬浮栅器件进行写入或者擦除操作。如果电荷泵泵压速度慢,EEPROM就不能实现高速数据改写,数据可能会丢失、误传,影响器件性能。因此,减小电压上升时间成为设计片上电荷泵的重点。

通过对静态 CTS 电荷泵[5]、浮阱电荷泵[6]、交叉耦合电荷泵[7]、Dickson 电荷泵[8-9]等电路进行研究和分析,并且考虑到工艺库文件的限制,选定Dickson电荷泵作为设计基础,运用电荷在电容中积累产生高压。对Dickson电荷泵进行静态分析和动态分析[10-11]可以看出,无论是二极管还是MOS管连接的Dickson电荷泵,它们输出电压的上升时间都与电源电压、传输管阈值电压、电荷泵级数、耦合电容、负载电容、驱动时钟的周期以及节点初始电压等参数有密切关系。

本文从研究时钟信号以及电荷泵初始电压入手,设计了一个16级MOS管Dickson电荷泵升压电路系统。电路对传统的Dickson电荷泵进行改进,并由占空比约为30%的高频时钟信号驱动,以实现快速升压的目的。

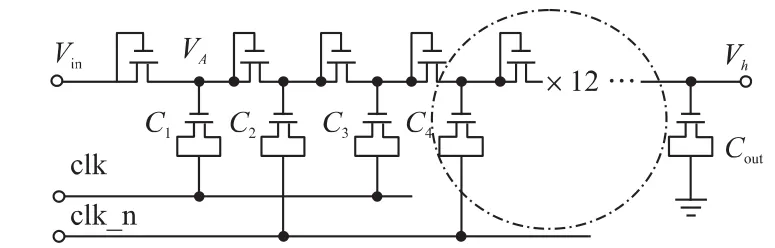

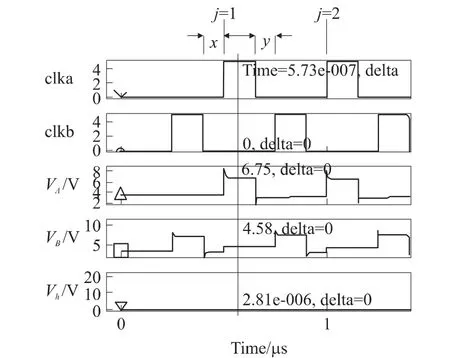

图1 MOS管Dickson电荷泵

1 电荷泵核设计与仿真

考虑到对芯片面积的影响,电荷泵核采用16级MOS管Dickson电荷泵模型,如图1所示,用栅漏相接的NMOS管作为二极管,用源漏相接的NMOS管作为电容,C1、C2…CN是耦合电容,Cout是负载电容,VA是第一个节点的电压,Vh是输出电压。由于二极管的单向导通特性,电荷只能从左边传到右边。随着电荷泵级数的增加,电荷会一级一级的传到输出端,从而得到高压Vh。

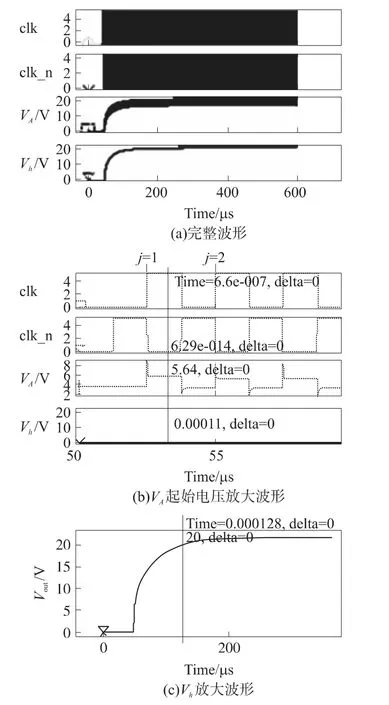

本文采用华虹NEC 0.35 μm CMOS工艺模型,用HSPICE软件对MOS管电荷泵进行仿真。仿真环境设定如下:仿真温度25℃,仿真时间为600 μs。输入电压Vin为5 V。时钟信号clk和clk_n是占空比为50%非交叠时钟,信号如下:v1 clk gnd pulse(0 μs 5 μs 50 μs 2 ns 2 ns 0.25 μs 0.5 μs);v2 clk_n gnd pulse(0 μs 5 μs 50.25 μs 2 ns 2 ns 0.25 μs 0.5 μs)。仿真结果如图2所示。

图2 MOS管电荷泵仿真波形

从图2(a)完整波形中可以看出MOS电荷泵输出电压振荡上升,最终输出稳定电压信号。从图2(b)VA起始电压放大波形中可以看出,在第一个时钟周期(j=1)里,VA(1)=5.64 V。从图2(c)输出电压Vh的放大波形图中可以看出,Vh从50 μs开始升压,0 V升压到20 V需要77.68 μs。

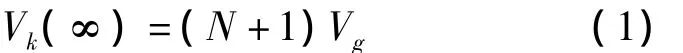

对Dickson电荷泵进行理论分析,在不考虑体效应的情况下,只有当时钟周期的个数j很大时,每个节点的电压Vk才能达到下面的理想值而在第一个时钟周期里,即j=1时刻,各节点处的电压Vk(1)只能达到

可见,每个节点的电压要想达到理论值,需要经过一定的时钟周期。如果增加每个节点的初始电压值,就可以明显减小电压上升时间。因此本文提出在MOS电荷泵中引入NMOS预充管,使每个节点的电压预充到一定值,减小节点电压达到理论值的时间。分别对电荷泵加入不同数目预充管进行仿真分析,研究预充管的数目对升压时间的影响

仿真结果表明,加入偶数个预充管可以提高电荷泵升压速度。预充管数目与升压时间(0 V升高到20 V)的关系如表1所示。

表1 预充管数目与升压时间的关系

从表1中可以看出:加入的预充管的个数越多升压越快;分别加入2个和4个预充管,升压时间减少的十分明显,加入4个预充管使升压时间减小了7.334 μs;在加入6个以上预充管,升压时间减少就没那么明显了。为了在减小升压时间的同时不过多的增加电路面积,本文只在电荷泵电路的前四级加入预充管,改进的Dickson电荷泵模型如图3所示。其中 M2、M3、M4、M54个 NMOS管作为预充管使用。M1管输入高电平导通,M2~M5管也导通,节点电压被预充到一定值。

图3 改进的电荷泵核电路

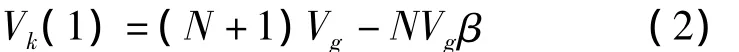

仿真环境不变,对改进的电荷泵核进行仿真。时钟信号仍然是占空比为50%非交叠时钟。对仿真波形进行放大,VA起始波形如图4所示。从图中可以看出,在第一个时钟周期里(j=1),VA(1)=6.750 V,而传统的MOS管Dickson电荷泵VA(1)=5.64 V。可见,改进的电荷泵第一级电压提高了2.11 V。

图4 改进的电荷泵核VA起始电压放大波形

2 时钟产生电路设计与仿真

传统的Dickson电荷泵采用占空比等于50%的两相非交叠时钟驱动信号,信号每次变化时,电容的充电电流和放电电流都同时打开,这无疑将引起电荷泄漏及充放电流失配等不利因素[12]。因此,本文提出使用占空比约等于30%的时钟信号驱动电荷泵,时钟信号理论波形如图5所示。该信号增加了x和y两段都为零的工作过程,此时电荷泵所有的电容都被复位,电容在完全放电之后再进行充放电操作,避免了两个电容充放电不匹配的现象发生。

图5 改进的驱动时钟信号

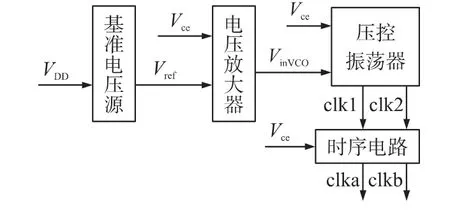

图6 时钟产生电路的结构框图

本文设计的时钟产生电路由基准电压源、电压放大器、压控振荡器和时序电路四个模块组成,其结构框图如图6所示。各模块的内部结构如图7所示。从图7中可见,基准电压源使用电流镜产生参考电流,以得到精确的电流值,再用电阻进行分压,以产生对电源电压不敏感的参考电压Vref。在电压放大器中加入了使能控制信号Vce,当Vce为高电平时,电路迅速复位,VinVCO被下拉到低电平,输出信号clka和clkb均为低电平。当Vce为低电平时,Vref被放大,从而得到振荡器驱动信号VinVCO,同时时序电路开始工作。振荡电路是升压系统的主要部分,如果不能起振,电荷泵就无法正常工作。为了提高电荷的转换效率,本文采用稳定的参考电压作为驱动的压控振荡器(VCO)。在VinVCO的驱动下,压控振荡器产生同频率、等幅值、初相角不同的周期振荡信号clk1和clk2;振荡信号clk1和clk2经时序电路整形产生方波信号,并经过调整产生本文所需要的占空比约为30%的时钟信号clka和clkb。

图7 时钟产生电路内部结构图

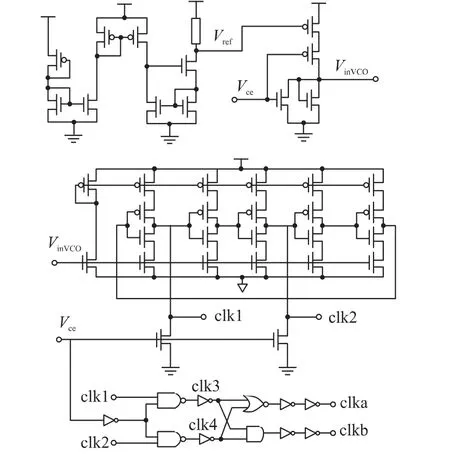

对时钟电路进行仿真,电源电压5 V,使能信号Vce为0 V,仿真时间为250 μs。图8为时钟产生电路一段放大仿真波形。

图8 时钟产生电路放大仿真波形

从波形中可以看出,振荡器输出周期振荡信号clk1和clk2,clk1和 clk2随后被整形为方波信号clk3和clk4,clk3和clk4再被调整为两相非交叠时钟信号clka和clkb。clka周期为0.481 μs,频率为2.079 MHz,高电平时间为 0.139 μs,clka 的占空比为28.900%。clkb周期为0.485 μs,频率为2.062MHz,高电平时间为 0.166 μs,clkb 的占空比为34.230%。clka和clkb的平均频率为2.071 MHz,平均占空比为31.565%,时钟电路产生占空比约为30%的时钟信号,符合设计指标的要求。

3 电荷泵电路系统仿真

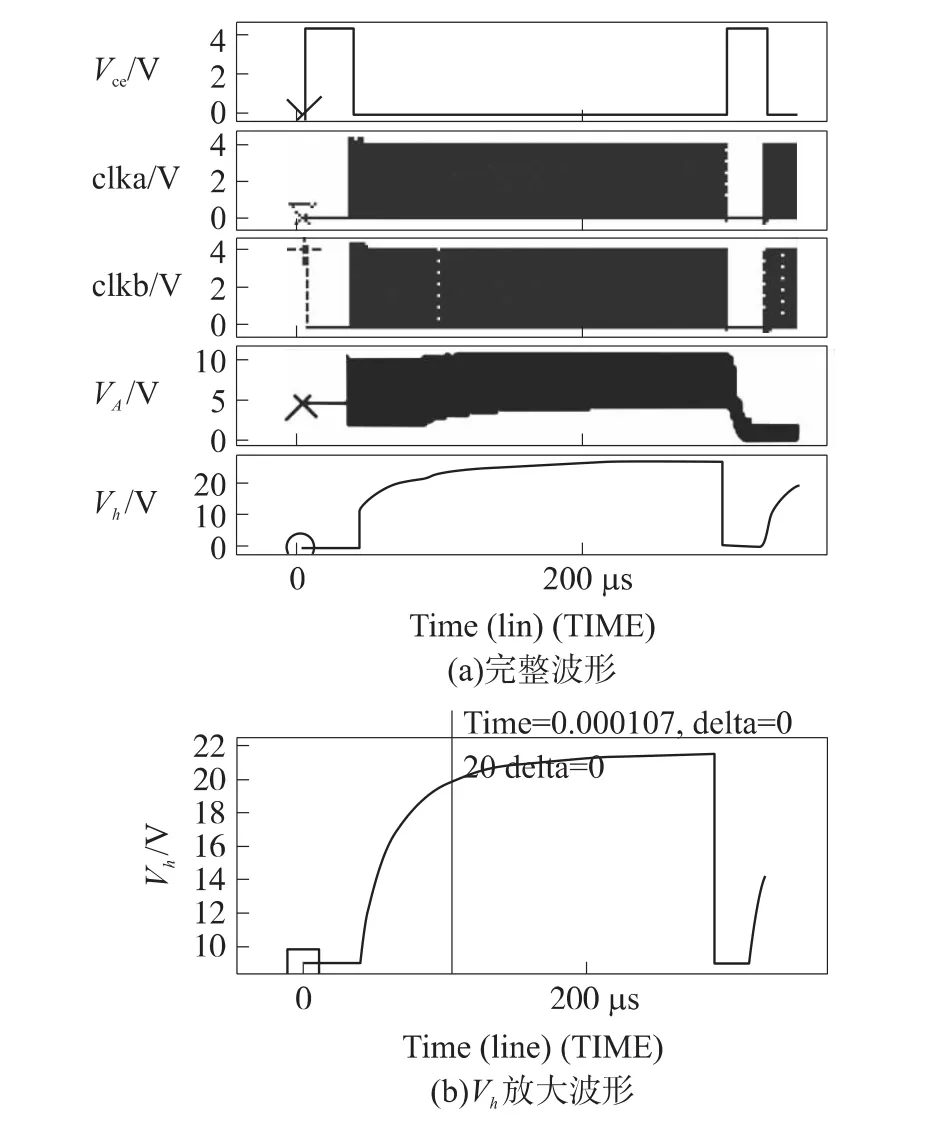

仿真环境不变,采用本文设计的占空比约为30%的时钟信号驱动带有预充管的电荷泵核,仿真输入信号如下:v1Vcegnd pwl(0 μs 0 μs 2 μs 0 μs 2.002 μs 5 μs 50 μs 50.005 μs 0 μs 280 μs 0 μs 280.05 μs 5 μs)。仿真结果如图 9 所示。

图9 电荷泵系统仿真波形

从图9(a)完整波形中可以看出使能信号Vce高电平有效,Vce经过短暂的高电平给电路复位后,变为低电平,电荷泵处于开启模式。电荷泵系统每个节点的电压都振荡上升,最终输出稳定电压。从图9(b)输出电压Vh的放大波形中可以看出,电荷泵输出的高压信号Vh在107.625 μs就升压到20 V。即在电荷泵开启以后,仅仅经过57.625 μs就可以升压到20 V。表1中传统的MOS管电荷泵从0 V升压到20 V需要77.68 μs。可见,同样升压到20 V改进的电荷泵比传统的电荷泵快了20.055 μs。

4 结论

设计了一个能够快速升压的稳定的电荷泵电路结构。通过在MOS管Dickson电荷泵中加入了四级预充管结构,使电容能够快速充电,增加了节点的起始电压,提高了电荷泵的升压速度。设计的时钟产生电路产生占空比约为30%的时钟信号,通过采用这种信号驱动电荷泵核,进一步提高了电荷泵升压速度。电荷泵仅需要57.625 μs就可以升压到20 V,比MOS管Dickson电荷泵升压到20 V快了20.055 μs。仿真结果表明本文设计的电荷泵系统具有升压速度快、可靠性高等特点。它不仅可作为EEPROM的内部模块使用,还可用于需要高速擦、写的电子产品中。

[1]Feng P,Li Y L,Wu N J.A High Efficiency Charge Pump Circuit for Low Power Applications[J].Journal of Semiconductors,2010,31(1):015009-1-015009-5.

[2]钱香,朱芙菁.可变增益电荷泵的分析与设计[J].电子器件,2012,35(1):83-89.

[3]Yu Y Y,Tang Y,Wan X G,et al.Application of Charge Pumping Technology on High-Voltage MOSFET Reliability Investigation[J].Chinese Journal of Electron Devices,2009,32(6):1023-1026.

[4]Cao H M,Yang Y T,Lu T J,et al.A Fast-Settling CMOS Charge Pump[J].Chinese Journal of Electron Devices,2008,31(5):1475-1478.

[5]Maksimovic D,Dhar S.Switched Capacitor DC-DC Converters for Low Power on-Chip Applications[EB/OL].IEEE PESC99.30th Annual,1999,1:54-59.

[6]Cheng K H,Chang C Y,Wei C H.A CMOS Charge Pump for Sub-2.0 V Operation[R].IEEE Int Symp on Ckts and Sys,2003(2):89-92.

[7]Tawfiqu H,Torsten L.A 5 V Charge Pump in a Standard 1.8V 0.18 μm CMOS Process[J].IEEE Journal of Solid-State Circuits,2005(2):1899-1902.

[8]Dickson J.On-Chip High-Voltage Generation in NMOS Integrated Circuits Using an Improved Voltage Multiplier Technique[J].IEEE Journal of Solid-State Circuits,1976,11(6):374-378.

[9]Richard J F,Savaria Y.High Voltage Charge Pump Using Standard CMOS Technology[J].IEEE Regular Session G:High Voltage Techniques and Continuous Time Filtering,2004:317-320.

[10]Mantooth H A,Duliere J L.A Unified Diode Model for Circuit Simulation[J].IEEE Trans on Power Electronics,1997,12(5):816-823.

[11]Toru T,Tomoharu T.A Dynamic Analysis of the Dickson Charge Pump Circuit[J].IEEE Journal of Solid-State Circuits,1997,32(8):1231-1240.

[12]Andersson O.Class D Hearing Aid Amplifier with Feedback[P].United States Patent,1998.5815581.