一种高分辨率遥感卫星高速串行接口设计

2013-12-29程芸王建宇黄巧林

程芸 王建宇 黄巧林

(北京空间机电研究所,北京 100076)

1 引言

随着遥感技术及相应处理方法的不断发展,国内外遥感卫星有效载荷的空间、时间和光谱分辨率不断提高,相应的数据规模呈几何级数增长,对高分辨率遥感卫星数据传输接口提出了更高的要求,其必须具有传输速率快、可靠性高和连接点少等特点。目前,大部分遥感卫星设备间接口类型都是低压差分信号(LVDS),图像数据传输接口的数据形式多为并行输出[1],这就需要大量的连接电缆,并且传输速率较低,带来可靠性、成本、质量等问题,越来越不适应航天遥感技术的发展要求。

为解决卫星遥感器获取的大量图像信息的高速传输问题,本文从硬件电路与互连协议两个方面进行设计,应用高速串行编解码收发器配合现场可编程门阵列(FPGA)器件,编程实现设备间数据传输。本文的设计采用高速串行总线接口技术,由于将时钟与数据合并进行传输,从而克服了时钟和数据的抖动问题,可获得较佳的信号完整性[2],为遥感卫星设备间的大数据量传输提供了一种解决方案。

2 物理链路设计

本文提出的高速数据传输接口设计,其关键是串行器/解串器(Serializer/Deserializer,简称Ser-Des)的应用。在发送端,多路低速并行信号被转换成高速串行差分信号,接收端再将串行差分信号转换为并行信号。这种点对点的串行通信技术,充分利用传输媒介的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

基于SerDes的高速串行接口,采用以下3点措施突破传统并行I/O接口的数据传输瓶颈,提高传输性能。①采用差分信号传输代替单端信号传输,从而增强抗噪声、抗干扰能力[3-4];②采用时钟和数据恢复技术代替同步传输数据和时钟,从而解决限制数据传输速率的信号时钟偏移问题[5];③采用8B/10B编码技术,使编码后的数据中0、1的数量基本一致,连续的0、l不会超过5位,从而保证信号的直流平衡,能很好地满足高速信号传输的需求[6]。

本设计应用SerDes芯片配合FPGA 编程实现设备间数据传输,其接口总体框图见图1。

图1 高速串行数据传输总体方案框图Fig.1 Layout of high-speed serial data transmission interface

高速串行传输电路系统包括以下几个部分:时钟产生模块、发送(接收)数据处理模块、数据发送(接收)模块和传输电缆。工作时,发送部分的FPGA 作为发送数据处理模块,产生多路16bit的数据包,这些数据包符合所使用的高速串行协议。发送器接收到数据包之后进行8B/10B编码,再进行并/串转换,串行数据由一对差分线串行送出。

接收部分与发送部分之间传输线上的阻抗匹配关系如图2 所示,传输线上通过50Ω 电阻进行匹配[7],以保证信号的完整性。

图2 接口阻抗匹配框图Fig.2 Impedance matching of interface

为了适应航天应用,保证数据高速、可靠传输,收发端使用高速连接器连接,收发接口间的连接线采用两芯同轴电缆连接,以传输一对差分信号,信号线屏蔽关系如图3所示,信号线上屏蔽层通过连接器接地。

图3 传输接口信号屏蔽与接地Fig.3 Shield and grounding of transmission interface

3 传输接口互连协议设计

为了启动串行接口数据传输,在建立物理链路之后,还要对所传送数据的格式进行更详细的定义,数据才可在发送器和接收器之间传送。基于Ser-Des的高速串行接口,在互连协议上对于采用何种同步码只给出了一些选择项,并未明确规定,也未确定数据帧的格式。因此,在SerDes的高速串行接口协议框架下,针对航天应用的实际情况,本文设计出了一种传输协议,其中包括数据帧的定义、协议规定和协议工作过程。

3.1 协议数据帧方案

考虑实际应用情况,从提高可靠性的角度出发,数据帧增加帧头、帧尾。设计传输协议的控制字符定义如表1所示,包括数据帧的帧头、帧尾以及同步字符。以16bit作为一个基本的传输单位,每一个控制字符都定义成2个字节,分别由D码和K码组成[5]。

表1 控制字符格式Table 1 Control character formats

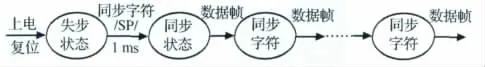

数据帧包括帧头(/SF/)、帧尾(/EF/)和数据单元(DATA)三部分,如图4所示。传输时,帧和帧之间发送同步字符/SP/,保证传输链路的同步。

图4 数据帧的定义Fig.4 Definition of data frame

3.2 协议规定

本协议是基于点对点的单工串行传输制定的,对协议作如下的规定。

(1)数据在通道上以数据帧的形式传递。每个数据帧的开始和结束,分别用帧头控制字符/SF/和帧尾控制字符/EF/标出。每一帧的数据(DATA)个数(不包括数据帧的帧头和帧尾标记)按约定输出。

(2)传输中,数据帧与数据帧之间发送同步字符/SP/,以保持传输链路的同步状态,如果在传输过程中收发双方失去同步,则通过帧间的同步字符重新建立同步。

(3)在系统上电或复位后,收发双方要首先建立同步,发送端先发送同步字符/SP/并保持1 ms,以建立与接收端的同步关系,之后发送数据帧。

3.3 协议工作过程

协议的工作过程见图5。系统上电或复位后,收发双方处于失步状态(要求在发送端复位后,接收端要保证已处于接收状态),发送端发送同步字符/SP/,时间长度为不小于1ms,1ms结束后认为系统完成同步过程,发送端开始数据帧的发送。在数据帧之间,发送端要发送同步字符,以保持数据传输链路的同步状态,发送同步字符的个数由传输逆程的长度决定,依此循环直至遥感相机停止工作。在同步状态建立后,接收端不断检测,输出控制信号RKLSB和RKMSB(K 码标志信号),如果在发送数据过程中控制信号出现高电平,即认为出现失步。接收端如果在数据帧传输过程中失步,依靠数据帧间的同步字符重新建立起收发间的同步关系;同步关系建立后,立刻转入正常数据接收状态。

图5 协议工作过程Fig.5 Protocol working procedure

4 高速数据传输试验

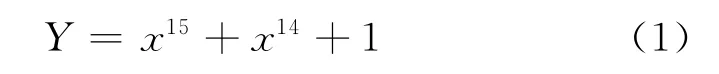

伪随机码序列具有良好的抗干扰性和抗衰落能力[8],利用发送端发送伪随机码,在接收端接收测试传输误码,在通信领域是一种常用方式。针对本文提出的串行接口设计方案,选取特征多项式为

式中:Y为序列输出;X为原始序列。

伪随机码序列可以很方便地用若干个移位寄存器来产生,最常用的是D 触发器[9]。图6演示了一种采用带线性反馈的移位寄存器产生伪随机码序列的原理机制[10]。级联移位寄存器根据选取的特征多项式,抽取寄存器的输出反馈,产生伪随机码。

图6 伪随机码发生器原理Fig.6 Protocol of PRBS generator

试验中,利用FPGA 编程实现伪随机码发生,通过串行编码器进行8B/10B 编码,经串行器转换成为2Gbit/s的高速串行信号,传输到解串器转换成并行信号后送到安捷伦公司误码仪,进行长时间数据传输误码率测试,测试结果如图7所示。经过6个多小时的数据传输试验,累计多达2.191 537×1015位数据中无误码出现,充分证明了高速串行接口设计的稳定、有效。

图7 误码率测试结果Fig.7 Test results of BER(bit error rate)

5 结束语

卫星遥感器获取的大量高速图像信息,使设备间大数据量的传输成为技术发展瓶颈。高速串行总线接口技术由于将时钟与数据合并进行传输,从而克服了时钟和数据的抖动问题,能够极大提高传输速率,减少IC外围引脚数,降低功耗,并能获得较佳的信号完整性。本文论述了用于卫星遥感器高速数据传输的设计过程,应用高速串行编解码收发器配合FPGA 编程,实现了设备间数据传输,通过伪随机码传输测试,实现了2Gbit/s的高速串行传输。目前,遥感卫星设备间数据传输一般采用并行方式,速率仅有800 Mbit/s,本文的设计无疑为高分辨率遥感卫星的数据传输问题提供了一种解决方案。不过,串行接口设计对时钟信号质量,包括占空比、时钟抖动等要求较高,为此,要在如何保证信号完整性方面进行更多的研究,以更好地提高数据传输率与可靠性。

(References)

[1]肖龙,万旻,李涛.高速数字图像数据传输的研究及实现[J].航天返回与遥感,2009,30(2):50-55

Xiao Long,Wan Min,Li Tao.Research and implementation of a high-speed digital image data transmission[J].Spacecraft Recovery & Remote Sensing,2009,30(2):50-55(in Chinese)

[2]高志,黄生叶.基于FPGA 的通用高速串行互连协议设计[J].计算机测量与控制,2009,17(9):1826-1830

Gao Zhi,Huang Shengye.Design of high-speed serial interconnection protocol based on FPGA[J].Computer Measurement & Control,2009,17(9):1826-1830 (in Chinese)

[3]叶菁华.高速串行数据发送器的研究[D].上海:复旦大学,2005

Ye Jinghua.Study on high-speed transmitter[D].Shanghai:Fudan University,2005(in Chinese)

[4]曹跃胜,胡军,刘烨铭.高速SERDES的多板传输技术与SI仿真[J].计算机工程与科学,2008,30(8):139-143

Cao Yuesheng,Hu Jun,Liu Yeming.The multi-board transmission technology and the SI simulation for highspeed SERDES design[J].Computer Engineering &Science,2008,30(8):139-143(in Chinese)

[5]Cole C R.100Gbit/s and beyond transceiver technologies[J].Optical Fiber Technology,2011,17(5):472-479

[6]杜旭,于洋,黄建.基于FPGA 的高速串行传输接口的设计与实现[J].计算机工程与应用,2007,43(12):94-96

Du Xu,Yu Yang,Huang Jian.Design and implementation of high-speed serial transmission interface based on FPGA[J].Computer Engineering and Applications,2007,43(12):94-96(in Chinese)

[7]黄乘顺,李星亮,蔡益宇.传输线阻抗匹配模型及精确计算[J].通信技术,2007,40(11):119-120

Huang Chengshun,Li Xingliang,Cai Yiyu.Impedance matching model and its precise computing of transmission line[J].Communication Technology,2007,40(11):119-120(in Chinese)

[8]于燕,焦晖.基于FPGA 的伪随机码序列发生器实现方案研究[J].电脑与电信,2006(6):47-52

Yu Yan,Jiao Hui.Research of the realization plan of pseudo-stochastic-code generator based on FPGA[J].Computer & Telecommunication,2006(6):47-52 (in Chinese)

[9]吴炜祺,艾勇,左韬,等.基于SOPC 的无线激光通信误码仪设计及实现[J].光通信技术,2008,32(2):52-55

Wu Weiqi,Ai Yong,Zuo Tao,et al.Design of embedded wireless laser communication BER tester based on SOPC[J].Optical Communication Technology,2008,32(2):52-55(in Chinese)

[10]Zid M,Scandurra A,Tourki R,et al.A high-speed four-phase clock generator for low-power on-chip Ser-Des applications[J].Microelectronics Journal,2011,42(9):1049-1056