数字逻辑设计的冗余与检错纠错

2013-12-25李仲秋

李仲秋

(长沙航空职业技术学院,湖南 长沙 410124)

1 数字逻辑电路的特点

在数字逻辑中,不方便采用如同存储器中使用的编解码技术。原因之一是数据的位置分散,不方便统一的编码,如最常用的线性分组码,被编码的位数越多,编码的效率越高,但如果数据分散,不容易进行高效率统一编码,而且使面积和功耗变得难以接受。如果强行提高被编码的数据位数,可能涉及到对原逻辑电路的改变,至少是对其布局布线的改变,这就影响原设计性能。另一原因是数据使用不同步,不方便解码(和检错),很可能在某一周期,只需要对一组寄存器中的某一个数据进行使用,(比如,[k+r, k]分组码,这组k个寄存器一组被编码,产生r个监督位),k位中其他的k-1位在这个周期并无使用价值,那么为了使用这一位数据,需要在这周期中对全部的k+r位进行校验计算,这样带来的硬件性能降低就会到不可容忍的程度。

2 复杂时序逻辑电路检错的难点

1)输入和输出的映射关系不明确

在复杂的时序数字逻辑中,在某一时刻来看,总输入和总输出的映射关系不明确。数据在关键路径上的传播所经历的空间跨度和时间跨度都可能很大,有可能当前的输出,是由之前多个周期的输入所决定的。这种不明确,使得检错需要的信息必须从中间的寄存器节点中去得到,加大了检错的成本。

2)逻辑关系交织

数据受到的干扰源不确定,错误产生后,往下传播对后一级(结构上,逻辑上)电路造成的影响也难以确定。一般需要对于关键数据进行保护(比如状态机的状态标志,处理器中的指令单元和运算单元),但是这样的保护,显然是不够的。例如,有限状态机中的状态跳转是由现有的状态和输入信号共同决定的,如果周围电路的输入中有错误,仅仅保护了状态机的标志位,状态机的跳转还是会发生错误。值得指出的是,有的电路有反馈逻辑,错误的影响更难以捉摸。

3 冗余与可靠性

数字逻辑设计可靠性的提高就是电路系统容错能力的提高,各种类型的容错设计方法都涉及到一定的冗余,根据冗余的类型可分为空间冗余、时间冗余、信息冗余等。

空间冗余(Space Redundancy),主要是硬件多模冗余。 三模冗余(TMR)、二模冗余(DMR),以及它们的改进版本,都属于这个范畴。

TMR通过对多路冗余结果进行表决,实现检纠错。TMR的改进版本几乎都是各种“局部三模冗余”(partial TMR),这些方法对电路中的某一部分进行TMR,在可接受的容错能力范围内尽量减少面积占用和电路功耗。局部三模冗余的关键,在于如何选取需要冗余涉及的子电路部分,有各种确定子电路是否进行冗余的优先级的方法,比如有的以信号的使用频率作为选择的准绳,使用频率高的单元优先进行冗余;有的以电路的逻辑结构特点作为准绳,将存在反馈的子电路优先进行冗余(考虑到反馈电路可能造成错误的累积)。

DMR能够侦错,但不能纠错,这是DMR的特点,但有些改进的DMR,局部融入TMR,能够一定程度上实现纠错时间冗余(Time Redundancy),这种方法的硬件占用相比于空间冗余较小,涉及到对于相关信号在多个时间点的采样[1]。时间冗余因为需要新的采样时钟,甚至需要利用传输线的延时特性,所以实施起来难度较大,一般会对性能有负面影响[2]。

信息冗余(information redundancy)的范畴较为广泛,凡是涉及到编码技术的检纠错EDC( error detection and correction)技术,都属于信息冗余[3]。

4 检错纠错

如果将一个可靠性设计划分为两部分,可分为功能部分和检纠错部分。

“功能部分”是指实现一个应用本身需要的电路,在没有SEU/SET情况下,功能部分能正常的完成所需的功能。

“检纠错部分”是指为了消除异常的翻转,而进行的容错设计部分。可以肯定地说,检纠错电路的输入信号都来自功能部分。

根据功能部分和检纠错部分两者的逻辑关系(结构关系),分为侵入方法和非侵入方法[4]。

“非侵入”的加固方法一般是仅对功能部分的输入和输出进行并行的数据分析,实现检纠错的目的。检错电路不干参与功能部分的关键路径,因此原有的功能在性能上没有负面影响。

“侵入”的方法将检纠错电路和原电路融合到一起,被加固的电路有时为了方便加入检错结构,甚至需要重新综合(re-synthesizing),对于性能要求高的电路的加固,侵入的方法不适用(如cores, macrocells,handcrafted designs ,legacy designs)。

一般的应用场合都要求“在线检纠错/ 实时检纠错”,所以功能部分的信号必须实时的作为检纠错部分的输入,检纠错电路需要不时的对关心的一些信号做检查来确定是否有异常的情况。如此一来,检错带来的额外的功耗就不可避免,检错电路本身成为硬件上的冗余,也不可避免。甚至可以说,没有硬件和功耗上的冗余,就无法检错和纠错。

5 一种改进的单元加固型容错触发器结构设计

从总体上看,可靠性的设计有两个努力的方向,一个方向是努力减少翻转的产生,另一个是在翻转发生后控制它向下一级电路的传播,使其不影响最终的功能实现。

如果将工艺改进和电磁兼容设计归为一条路(防错),容错设计归为另一条路(纠错),那么还有一些在独立的功能单元内部实施加固,实现抗干扰的单元,可以称之为中间路线。

单元可以是指锁存器、寄存器,也可以是复杂的加法单元、乘法单元,有的还是PLA逻辑阵列单元。这类容错的方法是介于前面提到的两个方向之间,但更接近前者的思路,将已发生的错误翻转限制在单元的内部,相邻的单元感觉不到异常的存在。

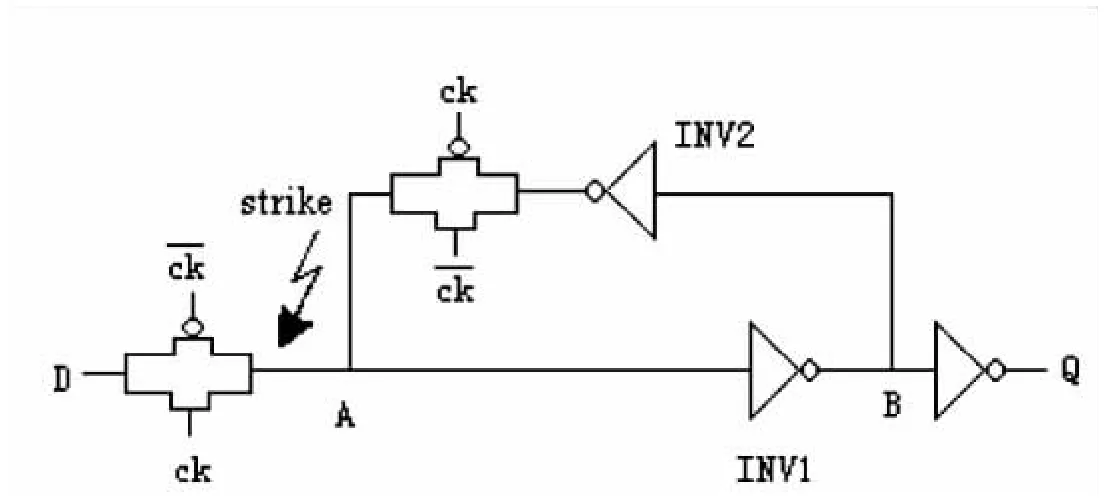

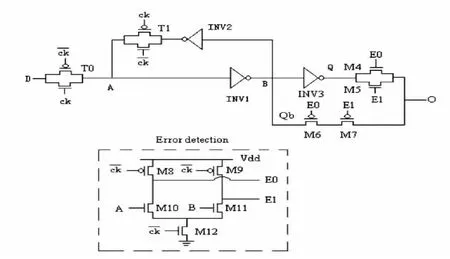

普通的触发器结构如图1所示,该结构未加固,容易受到外来粒子的干扰产生翻转。改进的单元加固型触发器结构如图2所示。

图2中提出的对普通的触发器单元改进的设计,是一种抗干扰的触发器设计[5]。这种触发器在干扰下会发生翻转,但这种错误在触发器内部通过某些方法被屏蔽掉,其输出是对的(至少在下一级电路的采样时刻是对的)。

时钟沿处发生的翻转,默认为正常的翻转,其他时刻的翻转,被认为是异常的翻转。在模拟设计中,这种检测可以通过电压,电流的检测电路来实现。

不过这种思路也存在上面提到的问题,如果时钟沿处有扰动,那么将被误认为是一次正常翻转。

图1 普通的触发器结构

图2 改进的单元加固型触发器结构

改进后的触发器,在输出端(B)加入M4、M5、 M6、M7,检纠错电路受到粒子撞击,发生异常的翻转的时候,产生M4、M5、 M6、M7的栅极电压E0、E1。虽然A、B处的逻辑电平发生了错误,但是由于M4-M7四个管子的作用,能使得输出端维持正确的输出值。

[1] Michael Nicolaidis.“Time Redundancy Based Soft-Error Tolerance to Rescue Nanometer Technologies”[A]. 17th Proceedings. VLSI Test Symposium[C]. 1999 IEEE. 86-94.

[2] V. Prasanth, Virendra Singh, Rubin A. Parekhji:“Robust detection of soft errors using delayed capture methodology”[A]. 16th International On-Line Testing Symposium[C]. 2010 IEEE. 277-282.

[3] K.Nepal.“Using implications for online error detection”[A]. International test conference[C]. 2008 IEEE.

[4] Avijit.“Combinational logic circuit protection using customized error detecting and correcting codes”[A]. 9th international symposium on quality electronic design[C]. 2008 IEEE.

[5] Xiaoxuan She.“SEU tolerant latch based on error detection”[A]. IEEE transactions on nuclear science[C]. 2012.