基于EPON系统的ONU LSW数据接收控制器设计

2013-12-17朱华伟

朱华伟

(四川文理学院 国有资产管理处,四川 达州 635000)

0 引言

EPON是由位于局端的OLT、位于用户端的ONU和由无源分光器和光纤线路构成的ODN等构成的点到多点系统,ONU端 LSW位于ONU MAC同用户侧之间,负责数据发送与接收的过滤,缓存,调度等,其设计效果直接影响着ONU与用户侧数据交互的质量.本文旨在设计一个数据接收控制器,用来对ONU发往用户侧的数据进行接收控制.[1]

1 功能描述

LSW数据接收控制器接收MAC发送来的帧数据并缓存在FIFO中,当MAC发送来的帧头指示信号有效时,开始接收帧数据及控制信号,并将接收到的帧数据和帧控制信号组成72位数据写入FIFO.[2]如果在接收数据帧的中途,FIFO 溢出,则丢弃当前正在接收的帧,等待下一个帧头指示信号.数据接收控制逻辑每接收一个数据帧或丢弃一个数据帧都要向CPU接口模块发送相应的指示信号.

2 子模块设计

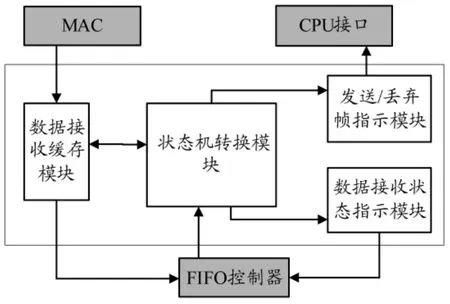

数据接收控制器主要由4个子模块组成,分别为数据接收缓存模块,状态机转换模块,数据接收状态指示模块,发送/丢弃帧指示模块.图1所示为数据接收控制器的各子模块结构框图.

图1 数据接收逻辑结构框图

2.1 状态机转换模块

状态机转换逻辑根据数据发送有效指示信号和FIFO满状态标志信号的状态生成状态机控制逻辑,控制数据的接收.通过发送控制信号,状态机转换模块在FIFO溢出时指示FIFO控制器丢弃当前帧,并要求CPU接口对丢弃的数据帧进行计数.同样通过发送控制信号,状态机转换模块在接收完一个完整数据帧时要求CPU接口对就收的数据帧进行计数.与状态机转换模块的数据控制逻辑相关的信号及其内涵如下:

mac2lsw_vlu:接收来自MAC的数据有效指示信号,该信号为高电平时,表示MAC正在发送的数据有效.

mac2lsw_sop:接收来自MAC的数据帧头指示信号,高电平脉冲信号,该信号为高电平时,表示接收到数据帧的帧头数据.

mac2lsw_eop:接收来自MAC的下行数据帧尾指示信号,高电平脉冲信号,该信号为高电平时,表示接收到数据帧的帧尾数据.

dgf2cpuif_drop_fra:发送给CPU接口的丢帧指示信号.每从低电平向高电平跳变一次,表示丢弃一个数据帧.

dgf2cpuif_wr_fra:发送给CPU接口模块的接收帧指示信号.每从低电平向高电平跳变一次,表示接收到一个数据帧.

full:数据缓存FIFO满状态标志.高电平有效,FIFO满时,必须停止向FIFO写入数据.

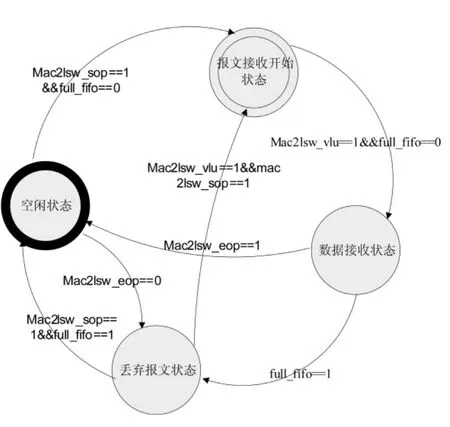

图2 数据接收状态转换图

数据接收处理逻辑包括4个状态,分别为数据接收开始状态,数据接收状态,数据丢弃状态,空闲状态.图2所示为数据帧接收处理逻辑的状态转换图.系统复位时,状态机处于空闲状态.当帧头指示信号有效时,如果FIFO没满,就开始接收数据.在接收数据帧的过程中,如果FIFO满了,则向FIFO控制器发送丢弃帧指示,指示FIFO控制器丢弃已经接收的帧数据,同时向CPU接口发送丢弃帧指示,用于丢帧计数.如果接收到一个完整帧,则向CPU接口模块发送接收帧指示,用于接收帧计数.同时等待接收下一个数据帧.

2.2 数据接收缓存模块

从MAC发送来的数据包含帧数据信号和帧控制信号.帧数据信号位宽为64位,共8个字节,按照低字节到高字节的顺序排列;帧控制信号位宽5位,包含帧头指示信号1位,帧尾信号指示1位,帧数据有效指示信号1位,字节指示信号3位.当收到MAC的数据发送指示时,数据接收缓存逻辑开始从MAC接收数据并把接收的数据按表1所示格式重新进行组装,新组装的数据在下一个时钟周期被发送给FIFO控制器.

表1 FIFO数据保存格式

2.3 发送/丢弃帧指示模块

每接收或丢弃一个完整数据帧都要向CPU接口发送指示信号,以便CPU接口进行接收数据帧和发送数据帧的统计.

2.4 数据接收状态指示模块

数据接收处理逻辑向FIFO控制器发送的数据包含帧数据和控制信号,帧数据如表一所示,控制信号包括写数据指示信号和丢弃数据指示信号.当状态机处于开始状态或数据传送状态时,置写数据指示信号有效,指示FIFO控制器接收数据;当状态机跳转到丢弃数据帧状态时,置丢弃数据指示信号有效,指示FIFO控制器丢弃当前正在接收的数据帧,包括该数据帧已经接收的数据和将要接收的数据.

3 功能验证

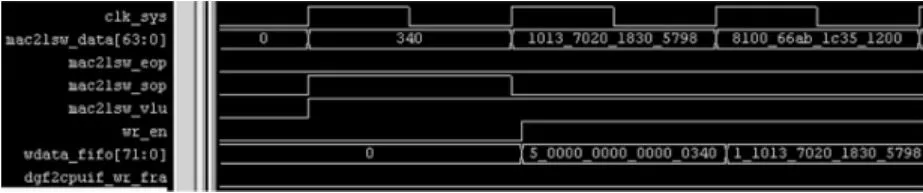

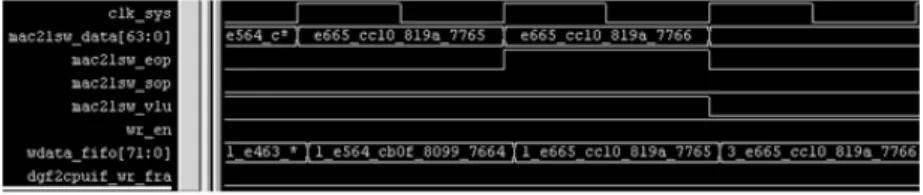

图3,4所示为数据接收控制逻辑仿真波形图,从图中可以看出,从 MAC接收的帧数据(mac2lsw_data)及帧数据控制信号在入口缓存了一个时钟周期后,被重新组成72位数据并被写入了FIFO(wdata_fifo).一个完整帧写入RAM后,数据接收处理逻辑向CPU接口模块发送了一个持续两个高电平时钟周期的接收帧指示信号(dgf2cpuif_wr_fra),与设计理论相符.

图3 数据接收处理波形图(帧头处理部分)

图4 数据接收处理波形图(帧尾处理部分)

4 结束语

本文针对LSW数据接收控制器提出了一种设计方案,并使用Verilog语言进行了描述,编写Testbench对RTL电路进行了验证,[3-4]结果表明设计方案较好的实现了LSW数据接收控制功能.

[1]朱华伟.10G EPON系统ONU交换模块设计[D].成都:电子科技大学硕士学位论文,2010:44-46.

[2]朱华伟,税奇军.基于异步FIFO的多时钟域同步技术研究[J].四川文理学院学报,2012(5):37-40.

[3]伯杰龙.System Verilog验证方法学[M].北京:北京航空航天大学出版社,2007.

[4]克里斯·斯皮尔.System Verilog验证:测试平台编写指南[M].张 春,麦宋平,赵益新,等,译.北京:科学出版社,2009:33.