基于CPLD的可编程PWM控制器的设计

2013-12-17周欣

周 欣

(南京信息工程大学电子与信息工程学院,江苏南京 210044)

PWM[1]成为现代电子系统中的重要技术手段,在电机调速、开关电源、逆变电源、D类功放、弧焊机和超声波清洗设备等方面有广泛的应用[2]。在电机调速中适当得选择PWM的开关频率能有效地降低电机的噪声[3]。目前许多单片机和DSP中都集成了一定功能的PWM控制器。但也有一些共有的局限性。主要表现在:(1)位数较。,一般不会超过16位,因而精度较低。(2)功能受指令的限制。(3)使用时占用微控制器的引脚[4]。当前有关使用CPLD进行PWM模块的设计,都局限于使用定宽调频法、调频调宽法和定频调宽法3种中的一种方法[5],这3种方法各有相应的优点和局限。本文提出了一种基于CPLD的可编程PWM控制器的设计,有效地避免了上述缺点。由于是可编程设计,因而可以与微处理器接口使用,通过微处理器对可编程PWM控制器的初始化,做到在系统工作中根据要求灵活合理地使用上述3种PWM实现方法中的任意一种。

1 系统的内部结构设计

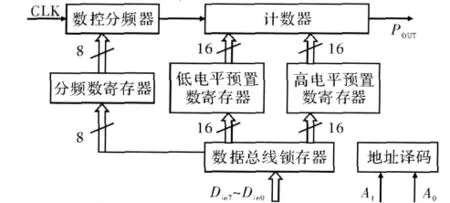

CPLD选用Altera公司MAX II系列的EPM570,可编程PWM控制器设计的内部结构如图1所示。

图1 可编程PWM控制器设计的内部结构

该系统由一个加法计数器、16位的高低电平预置数寄存器、分频数寄存器、数控分频器、数据总线缓冲器以及地址译码器构成[6]。CLK提供基准频率信号,经过一个数控分频器进行分频可以控制输出频率,分频数由分频数寄存器确定。将分频后的时钟送入计数器进行计数。当计数值分别等于高低电平预置数寄存器的值时,让计数器的输出发生逻辑翻转,这样就实现了PWM波的输出。假设CLK的频率为Fs;分频数寄存器的值为Ndiv,则分频后的时钟频率为Fs/(Ndiv+1);若高低电平预置数寄存器的计数值分别为Nh、Nl,则PWM波的频率为Fs/((Ndiv+1)(Nl+Nh));占空比为Nh/(Nh+Nl)。可见该系统的输出频率和占空比均数控可调,如果希望频率不变,占空比可调,只需保持Nl+Nh为常数即可。

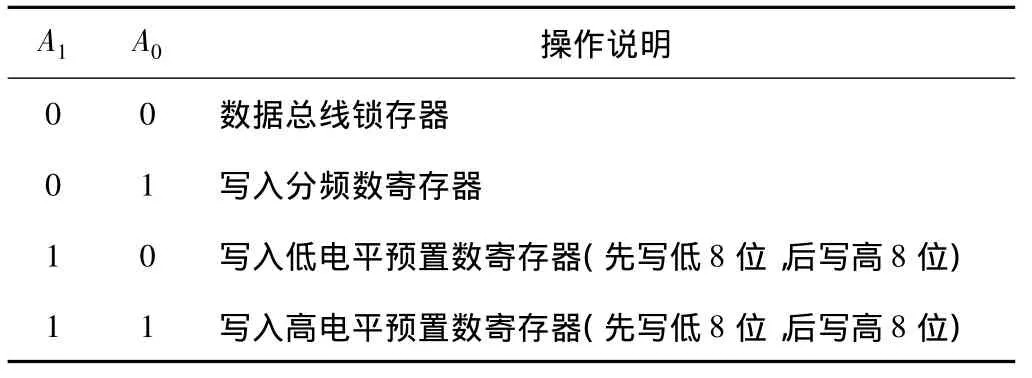

表1 端口地址译码表

2 硬件描述

该系统的硬件描述采用VHDL语言,利用Quartus II进行编译、适配、综合。其硬件描述的顶层文件如图2所示。其中clk_div为数控分频器,pre_freq_div_reg为8位分频数寄存器,pre_low_reg和pre_high_reg分别为16位预置低字节和预置高字节寄存器,其预置值通过data_buffer8位数据锁存器分两次写入,先写入低字节,后写入高字节,address_decoder为2/4线地址译码器。其端口译码如表1所示。counter为16位输出计数器,使计数器清零开始计数,Pout输出为高电平当其计数达到预置高字数时Pout输出翻转为低电平,并使计数器清零且重新计数,当计数达到预置低字数时,使计数器清零重新开始计数且Pout输出翻转为高电平。如此往复产生相应的PWM波形。其初始化编程步骤为:(1)向数据总线锁存器写入相应的分频数,然后向地址总线输入00,将数据输出使能。(2)向地址总线输入01,将分频数写入到分频数寄存器中。(3)向数据总线锁存器写入低电平预置数的低字节,然后向地址总线输入00,将数据输出使能。(4)向地址总线输入10,将低电平预置数的低字节写入到低电平预置数寄存器中的低字节中(5)向数据总线锁存器写入低电平预置数的高字节,然后向地址总线输入00,将数据输出使能。(6)向地址总线输入10,将低电平预置数的高字节写入到低电平预置数寄存器中的高字节中(7)向数据总线锁存器写入高电平预置数的低字节,然后向地址总线输入00,将数据输出使能。(8)向地址总线输入11,将高电平预置数的低字节写入到高电平预置数寄存器中的低字节中(9)向数据总线锁存器写入高电平预置数的高字节,然后向地址总线输入00,将数据输出使能。(10)向地址总线输入11,将高电平预置数的高字节写入到高电平预置数寄存器中的高字节中。初始化编程结束,从 Pout输出相应的PWM波。

3 仿真与实验结果

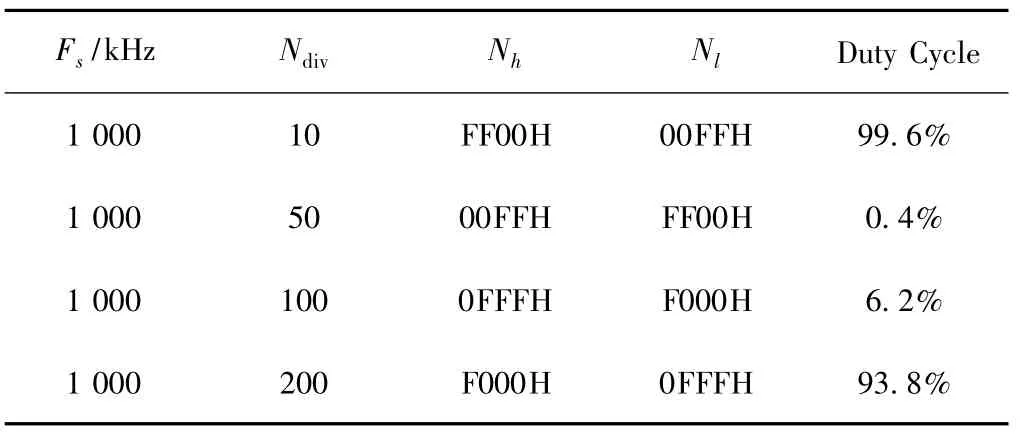

图2 硬件描述的顶层原理图

使用Quartus II仿真功能对设计的系统进行仿真[7],其仿真如图 3所示。通过在自行开发的KMCPLD-II型实验开发系统上进行下载实验,输入频率为1 MHz的方波信号,分频数分别为10、50、100、200,任意选择高低电平的预置值,只要使得Nl+Nh=常数其实验结果如表2所示。从仿真和实验的结果可以看出,设计结果符合预计的设计要求。

图3 系统仿真图

表2 实验结果表

4 结束语

提出的基于CPLD的可编程PWM控制器的设计方法,具有结构简单,稳定可靠,数控精度高,频率设置灵活的优点。由于采用CPLD技术,因而可以根据实际应用要求调整数控精度。由于其采用可编程设计,因而可受各种CPU控制,通过对该可编程PWM控制器的初始化,实现在系统的工作中根据系统要求在较宽的范围内任意使用定宽调频法、调频调宽法和定频调宽法3种中的一种方法,并随时改变其PWM的输出频率和占空比参数。

[1]李旭,谢运祥.PWM技术实现方法综述[J].电源技术应用,2005(2):40-43.

[2]刘松,熊腊森.使用VHDL设计基于CPLD/FPGA逆变电源的 PWM 波形[J].焊接学报,2002,23(6):89-91.

[3]满永奎,边春元,许宁.零空间矢量和PWM开关频率对异步电机噪声的影响[J].东北大学学报:自然科学版,2002,23(8):738 -739.

[4]冯小平,张林,赵焕军.一种基于CPLD实现的数字化PWM 波形产生器[J].现代电子技术,2003(3):71-72.

[5]杨志刚,蒋欣.CPLD在基于PCI总线的功率模块设计中的应用[J].国外电子元器件,2008(4):29-31.

[6]梁中华,肖丹,杨霞.一种基于CPLD的SPWM控制波形生成方法[J].沈阳工业大学学报,2005,27(2):187-191.

[7]任爱锋.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.