一款32位定点DSP电路的设计

2013-12-05薛海卫张庆文王月玲徐新宇

薛海卫,张庆文,王月玲,徐新宇

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

数字信号处理器DSP广泛应用于现代通信、信息处理、自动控制等领域中,通过指令程序,DSP能实现滤波、快速傅里叶变换等各种算法,是现代信号处理的关键器件之一。DSP通常由CPU、存储器、外设等逻辑部件组成,根据处理数据的位宽分为16位或32位、根据处理数据的类型分为定点和浮点。本文设计的32位定点DSP可以在单周期内实现16×16位有符号整数乘法、累加和32位数据的算术逻辑运算,处理精度高。本电路采用正向设计流程,自主设计了CPU、ROM和SCI、TIMER等外设,通过0.5 μm 1P3M CMOS工艺流片,实现了一种快速实时的32位定点数字信号处理器电路。

2 32位DSP体系结构

2.1 32位DSP总体架构

DSP体系结构是设计DSP的核心和基础,决定了该DSP所达到的性能。根据开发时间与性能指标的要求,这款32位定点DSP的研制目标是中低速、低功耗及高可靠,由此决定32位DSP体系结构及指令系统。该DSP由CPU、总线、外设、ROM等功能部件组成,CPU采用增强的硬件,包含32位乘法器、32位ALU、32位寄存器队列,4条CPU内部总线分别可以从存储器和寄存器队列中传递操作数,两个独立的专用地址运算逻辑单元ARAU可以在单周期内产生2个地址。CPU与外设间采用哈佛总线结构,由4条总线组成,增强程序执行速度和数据吞吐带宽。

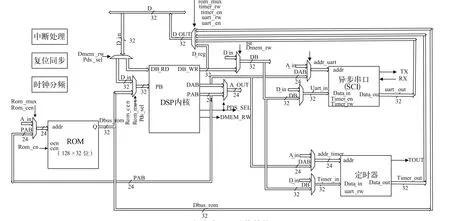

根据该体系结构,32位DSP电路可以实现2操作数和3操作数的加、减、乘等算术运算及与、或、非、异或、移位等逻辑运算,通过跳转、返回、堆栈等操作实现程序控制,该电路具有4级流水线。32位定点DSP的总体结构图如图1所示。

图1 32位定点DSP总体结构图

2.2 32位DSP的总线结构

32位DSP采用哈佛总线结构,片内总线包括32位的程序总线PB、数据总线DB和24位的程序地址总线PAB、数据地址总线DAB。DB通过多路复用器连接到定时器和串口的数据端,DAB连接到定时器和串口的地址端。因BOOTROM存放只读程序,其数据输出端与PB相连,地址端与PAB相连。

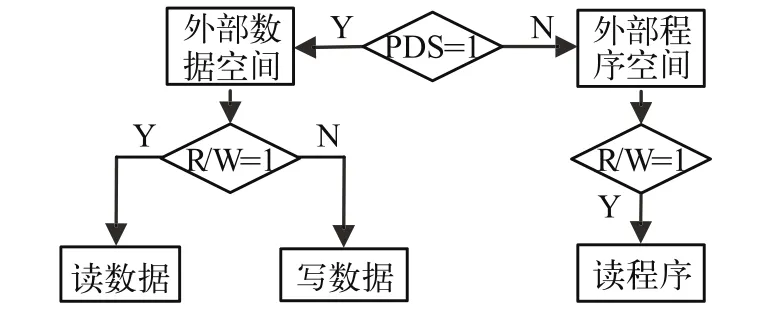

当电路处于微处理器(MP)模式时,程序从片外存储器读取到PB上,数据也从片外存储器读写到DB,外部启动该DSP;当电路处于微计算机模式(MC)时,引导程序从BOOTROM读取到PB上,内部启动该DSP。片内的PB和DB复用到32位外部数据总线DATA上,片内的PAB和DAB复用到24位外部地址总线ADDR上,通过外部存储器接口的双向数据总线DATA、地址总线ADDR和PDS、RW等片选信号实现对片外存储器的读写访问。外部存储器的读写接口如图2所示。

2.3 32位DSP 的CPU核

32位DSP的CPU由定点乘法器、算术逻辑运算单元ALU、移位器、辅助寄存器运算单元ARAU以及寄存器队列组成。

图2 外部存储器读写接口

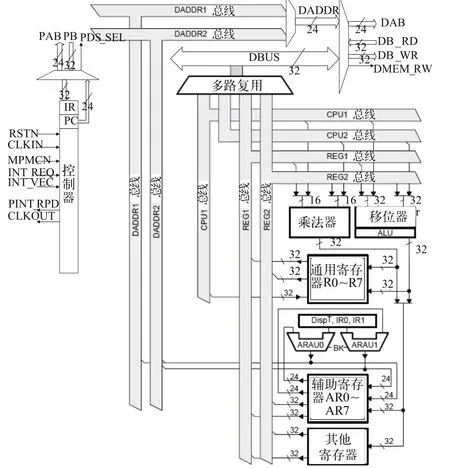

为提高并行性,CPU内部采用4条32位的数据总线CPU1、CPU2、REG1、REG2,2条24位地址总线DADDR1、DADDR2。REG1、REG2总线与内核寄存器队列相连,CPU1、CPU2总线与核外数据总线相连。CPU内部结构图如图3所示。CPU1、CPU2、REG1、REG2总线通过复用器与内核数据总线DBUS相连,CPU与核外交互的接口总线为读数据总线DB_R、写数据总线DB_W、程序总线PB、数据地址总线DAB和程序地址总线PAB。控制信号DMEM_RW控制数据总线的读写,PDS_SEL控制程序空间和数据空间的选择。当读取指令时,PDS_SEL为低,程序计数器PC产生24位程序地址给程序地址总线PAB,通过PAB寻址,程序指令送入32位的程序总线PB上,PB再把指令送入指令寄存器IR进行指令译码。当读写数据时,PDS_SEL为高,ARAU0、ARAU1产生24位的地址给2条内核数据地址总线DADDR1和DADDR2,DADDR1和DADDR2复用到DADDR总线并生成24位数据地址总线DAB。根据DAB和读写信号DMEM_RW,读数据时把DAB寻址的数据通过核外DB总线读到32位数据读总线DB_R上并送入内核的32位双向总线DBUS上,写数据时把内核DBUS上的数据写到数据写总线DB_W上并把它送出到核外DB总线上。

24个寄存器组成寄存器队列,包括8个通用寄存器R0~R7、8个辅助寄存器AR0~AR7、数据页指针DP、索引寄存器IR0~IR1、块长度寄存器BK、堆栈指针SP和状态寄存器ST、程序计数器PC和指令寄存器IR。

图3 CPU结构图

2.3.1 ALU

ALU在单周期内完成对32位整数、32位逻辑的运算。逻辑运算包括与、或、非、异或、左右移位等操作。移位器在单周期内完成左右移位操作,移位数最多可达32位。CPU总线或REG总线上的数据经移位器移位后送入ALU运算单元,ALU根据指令译码完成相应的运算后把结果送入32位通用寄存器R0~R7。

2.3.2 乘法器

32位DSP的乘法器采用移位加方式,在单周期内实现16×16位的无符号数和带符号数的乘法运算。假设两个16位的带符号数为A16和B16,其中A16=a15a14……a2a1a0=-a15×215+=-a15×215+A15,B16=b15b14……b2b1b0=-b15×215+=-b15×215+B15,其中A15、B15为无符号数。乘积P32=A16×B16=(-a15×215+A15)×(-b15×215+B15)=a15×b15×230+(-a15×B15)×215+(-b15×A15)×215+A15×B15,其中第1项和第4项为无符号数乘法,第2和第3项为负数。因负数可以表示为取反加1即-N=+1,所以-a15×B15=-a15×,可以表示为1×216+1×215++1。同理,-b15×A15也可用上述方法表示,而无符号数乘法就是各位相与的过程。

由以上分析可知,根据乘法运算规则,整数相与、负数相与后取反加一再移位相加即可实现所有乘积项相加,所以用简单的与门、与非门、移位器和加法器就能实现该乘法运算。

乘法器的乘数和被乘数来自CPU总线或REG总线,32位乘积存入寄存器R0~R7中。

2.3.3 辅助寄存器运算单元ARAU

ARAU通过加、减等操作完成与地址相关的运算,ARAU可以操作8个32位辅助寄存器AR0~AR7,并对其进行修改,产生24位地址。AR也可以作为32位的通用寄存器供乘法器和ALU使用。

32位DSP单周期可以实现3操作数操作,两个独立执行的ARAU同时生成两个地址,以提高寻址能力和数据吞吐率。

在间接寻址中,ARAU可以通过自动加一、减一实现顺序寻址,通过加减偏移量实现偏移量寻址,通过加减32位索引地址IR0/1,实现索引寻址。

循环寻址时ARAU用32位的块寄存器BK标示数据块的大小,ARAU把辅助寄存器中的地址加减循环块大小BK产生新的地址。

位反寻址时ARAU把辅助寄存器地址以位反加减的方式产生新的地址。

2个ARAU的输入是偏移量DISP0、索引寄存器IR0/1、循环块寄存器BK或辅助寄存器AR0~AR7中的一个,计算后的24位地址输出到AR0~AR7以更新辅助寄存器中的地址或直接输出到数据地址总线DADDR1、DADDR2。

通过多种寻址方式的译码控制ARAU的地址计算方式。

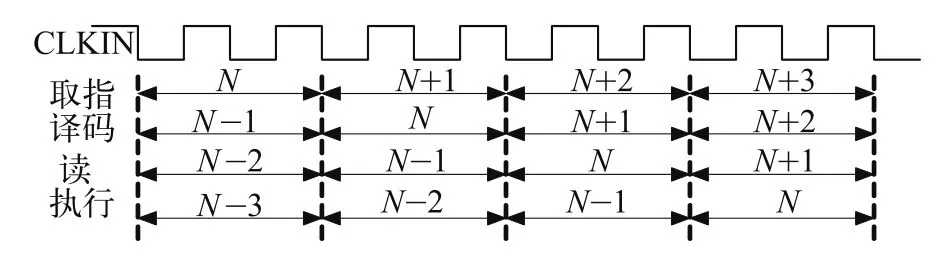

2.3.4 流水线

电路采用4级流水线方式,包括取指(F)、译码(D)、读数(R)和执行(E)。在取指阶段,通过PAB总线从存储空间取指令到PB,送入IR,刷新程序计数器PC。在译码阶段,指令译码控制器产生与操作数相关的指令译码,ARAU产生与数据地址相关的辅助寄存器寻址运算结果,并产生指令操作数相关的地址(读数据地址)到DAB总线。在读数据阶段,数据从存储空间读到数据总线DB_R上。在执行阶段,将指令中指定的数据或是存储空间读出的数据执行专门的操作,如加减、乘除、位运算,更新状态寄存器ST标志,结果通过DB_W总线写入存储空间(或通过REG总线写入专用寄存器)。

图4是4级流水线操作示意图,图5是流水线逻辑示意图。

图4 4级流水线示意图

图5 流水线逻辑图

2.4 32位DSP指令集及寻址方式

32位DSP指令集包括实现加法、减法、乘法、左右移位、存储、跳转、堆栈和逻辑运算等操作。DSP取指令后放入指令寄存器IR,通过指令译码控制ALU、ARAU、移位器和乘法器的动作,同时实现程序控制,包括跳转、堆栈、条件返回等操作。

32位DSP提供寄存器寻址、直接寻址、间接寻址、立即寻址、PC相关寻址、循环寻址、位反寻址等7种灵活的寻址方式。直接寻址是地址由32位数据页指针DP中的低8位和指令中的低16位组成。DP中的低8位用来作为直接寻址中的数据页,共256页,每页64 K字长度;寄存器寻址是操作数直接在CPU寄存器中;立即寻址的操作数是一个16位或24位的立即数;PC相关寻址是一个16位或24位的偏移量载入PC;间接寻址是辅助寄存器通过ARAU运算生成操作数的地址;循环和位反寻址常用于滤波、FFT等DSP算法中。

3 32位DSP的实现

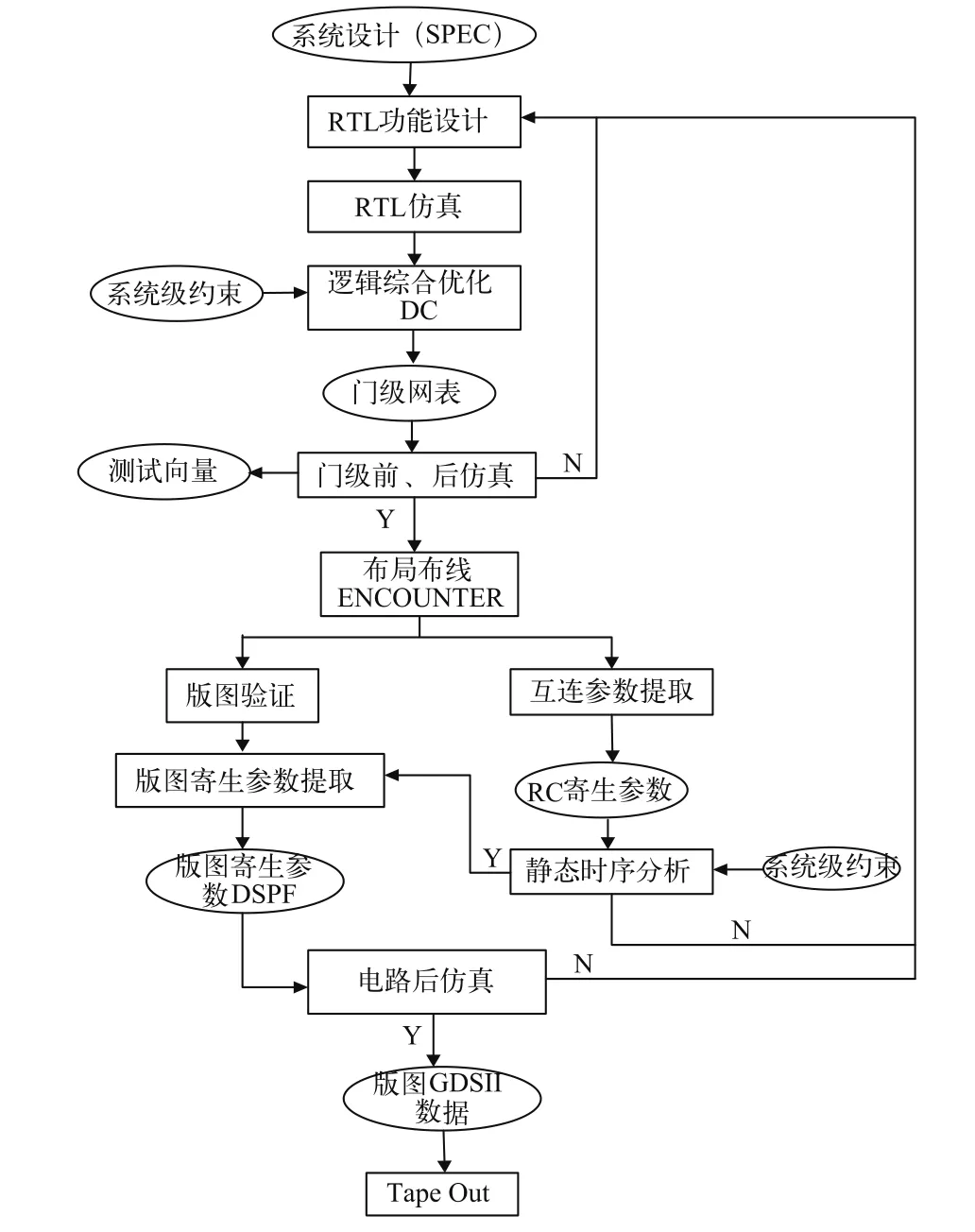

32位DSP采用标准单元的设计方法,基于0.5 μm标准单元库正向设计。通过功能规范定义、模块划分、RTL代码、RTL仿真、DC综合、门级前后仿、布局布线、静态时序分析、晶体管级后仿到出GDSII数据等流程。该设计流程如图6所示。

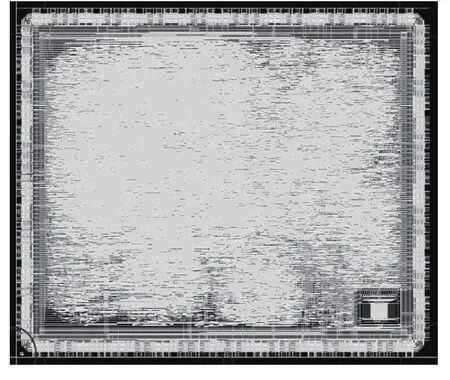

该电路集成规模为7万门,芯片面积10.0 mm×8.4 mm,版图如图7所示。经流片后测试得到该芯片的工作电流为108 mA,静态电流为15 μA,最高工作频率36 MHz,单指令周期55.5 ns,功能和性能达到设计目标。

图6 设计流程

4 结论

通过对DSP的架构及总线结构、ALU、乘法器、ARAU和流水线等分析,弄清了CPU中的各个关键部件及其实现方式。采用标准单元的正向设计流程,实现了一款基于0.5 μm工艺的DSP芯片。该芯片集成度7万门,经过流片、测试后,该芯片的工作频率可达36 MHz,动态功耗594 mW,所设计的指令和外设等功能均工作正常,达到了预期的设计目标。

图7 32位DSP芯片版图

[1] 支长义,等. 浮点DSP原理及应用[M]. 成都:电子科技大学出版社,2003.

[2] 帕特森·亨尼西. 计算机组成与设计——硬件/软件接口[M]. 北京:机械工业出版社,2010.

[3] 虞希清. 专用集成电路设计实用教程[M]. 杭州:浙江大学出版社,2007.

[4] 李亚民. 计算机原理与设计——Verilog HDL版[M]. 北京:清华大学出版社,2011.