基于ARM平台的FIFO接口设计及其应用

2013-12-01罗明璋王军民

徐 菲,罗明璋,王军民

(长江大学电子信息学院,湖北 荆州434023)

传统的测控系统采用前端采集后经由串口传输给PC机的采集模式,因采集传输速率有限,无法满足测控系统的实时性要求。另外,PC机功耗高、体积大,难以适应野外施工需求[1-2]。为此,笔者基于ARM平台进行了FIFO接口设计。

1 FIFO接口电路设计

1.1 数据线部分

对于传输通道来说,采集卡发送数据,处理器接收数据,其数据总线宽度应保持一致。C8051F060使用的是8位数据总线,IDT7208使用的数据总线是9位FIFO,S3C6410使用32位数据总线,因此系统的传输通道每次传输8位数据[2]。作为FIFO数据输入端,C8051F060的外部数据总线接入到IDT7208的数据输入总线,而FIFO输出数据给ARM,则IDT7208的数据输出总线接S3C6410的数据总线的低8位LDATA0~LDATA7[3]。

1.2 控制线部分

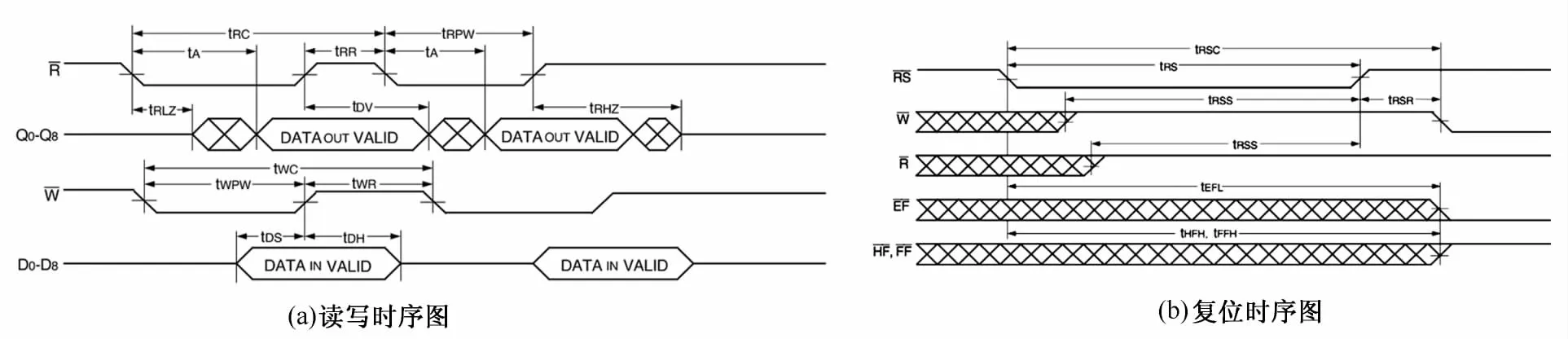

由FIFO的异步时钟先入先出结构及IDT7208的读写时序图(见图1(a))可知,系统中ARM和单片机都不需要使用地址线选择数据,只需对FIFO的读控制(/W)和写控制(/R)分别给予读时钟和写时钟即可。鉴于ARM内部片地址选址机制,可将ARM的外部存储器片选信号(/n CS1)与外部数据读控制信号(/Ln OE)进行逻辑或后作为FIFO的读控制(/R),这样ARM只要访问0X08000000~0x10000000之间的任意地址都能访问到FIFO[4]。

图1 IDT7208读写时序图及复位时序图

C8051F060如果要将采样所得数据实时地送入FIFO,必须使用DMA(Direct Memor y Access,直接内存存取)方式。将C8051F060中可DMA访问的外部数据总线(P7)接IDT7208数据输入总线(D0~D7),然后让单片机的P0.5输出与外部写控制线(/WE-P4.7)进行逻辑或后将其连接至FIFO的写控制(/W)。

根据IDT7208芯片手册描述,IDT7208在重新上电及出现后需要进行复位,因此将C8051F060的P0.6与IDT7208的/RS相连用以复位FIFO(见图1(b))。

1.3 状态线部分

IDT7208提供了3个状态信号,即空信号(/EF)、半满信号(/HF)和满信号(/FF),将这3个状态信号分别与单片机和ARM相连,用以触发外部中断及状态监测。

2 FIFO接口软件设计

2.1 采集卡的FIFO接口软件设计

在C8051F060开始采集前,通过程序将其内部ADC输出配置成DMA模式。采样时,使单片机的P0.5引脚输出为低电平,此时ADC完成采集后DMA会将转换后的数据放入FIFO的D0~D7,与此同时将从/WE脚输出下降沿。因单片机的P0.5脚与/WE脚通过一个或门连接到FIFO的写信号(/W),这样此时FIFO的写信号(/W)也为下降沿,D0~D7上的数据将写入FIFO。这样ADC每完成一次采集点的采样,DMA都会把当次采集到的数据分成高、低字节按顺序分2次存入FIFO。

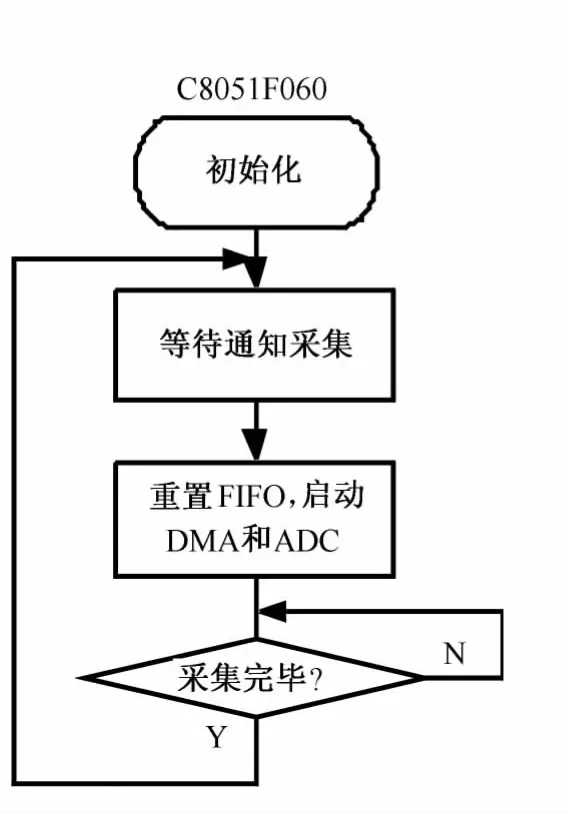

在进行数据采集前,C8051F060需要将IDT7208先复位,这样可以更充分地保证FIFO的读、写指针的稳定。根据IDT7208的复位时序图,首先将C8051F060的P0.6脚配置成通用输出口,然后给IDT7208的/RS引脚输入一个不小于25ns的低脉冲,即在C8051F060的P0.6脚输出一个低脉冲,并在复位完成后延时10ns再开始进行采集。C8051F060的软件流程如图2所示。

2.2 ARM的FIFO接口软件设计

ARM外部存储器片选信号(n CS1)和外部数据读控制信号(/Ln OE)进行逻辑或后与FIFO的读信号(/R)连接在一起,这样ARM每执行一次外部存储器I/O读操作,FIFO的/R脚便会接收到一个负脉冲,此时ARM读取到FIFO的一个数据。

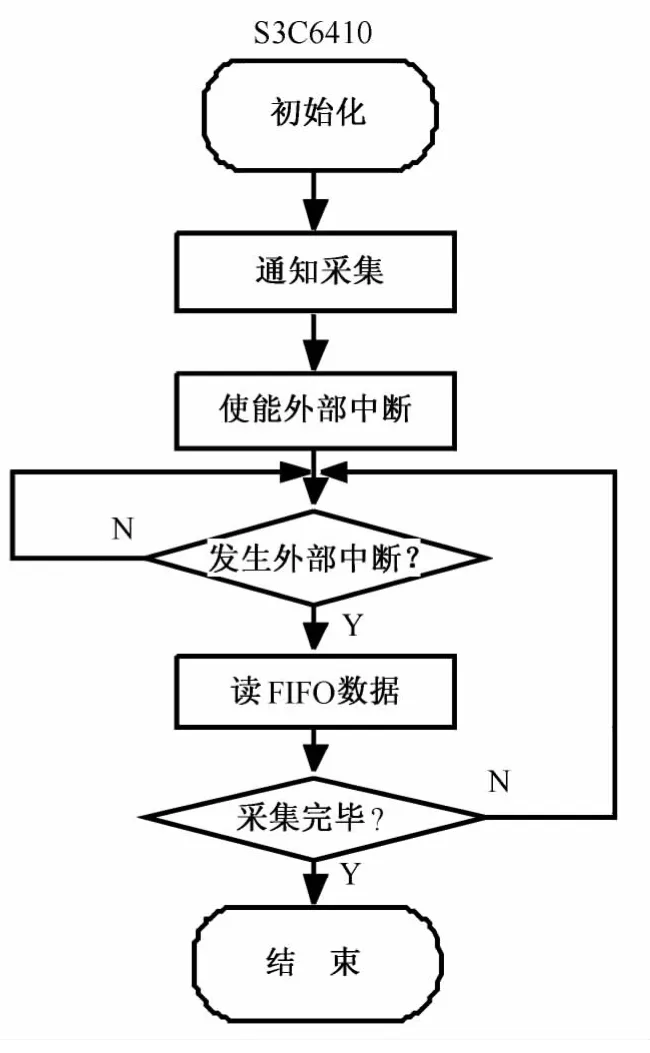

IDT7208的数据最大存储容量为64 Kb,在C8051F060完成16K次采集转换后,IDT7208已经存入一半的数据,此时FIFO存储器半满信号标志(/HF)输出低电平(在不到半满时输出高电平)。S3C6410的外部中断EINT4已经连接到了FIFO存储器的/HF信号,利用其由高到低的变化产生的中断可以说明数据传输状态。当ARM接收到/HF发出的中断后,ARM开始连续执行32 K次I/O读操作,数据便依次从IDT7208送入S3C6410中了。S3C6410的软件流程如图3所示。

图2 C8051F060的软件流程图

图3 S3C6410的软件流程图

3 实例应用

将上述设计应用于基于声频应力波无损检测法的锚杆锚固无损检测系统中。在该系统中,声波探头的接收频率一般为20 Hz~20 KHz,根据采样定理,采样率最好大于探头接收频率的5~8倍,因此测量时设置 C8051F060采样率为500 KHz[5]。

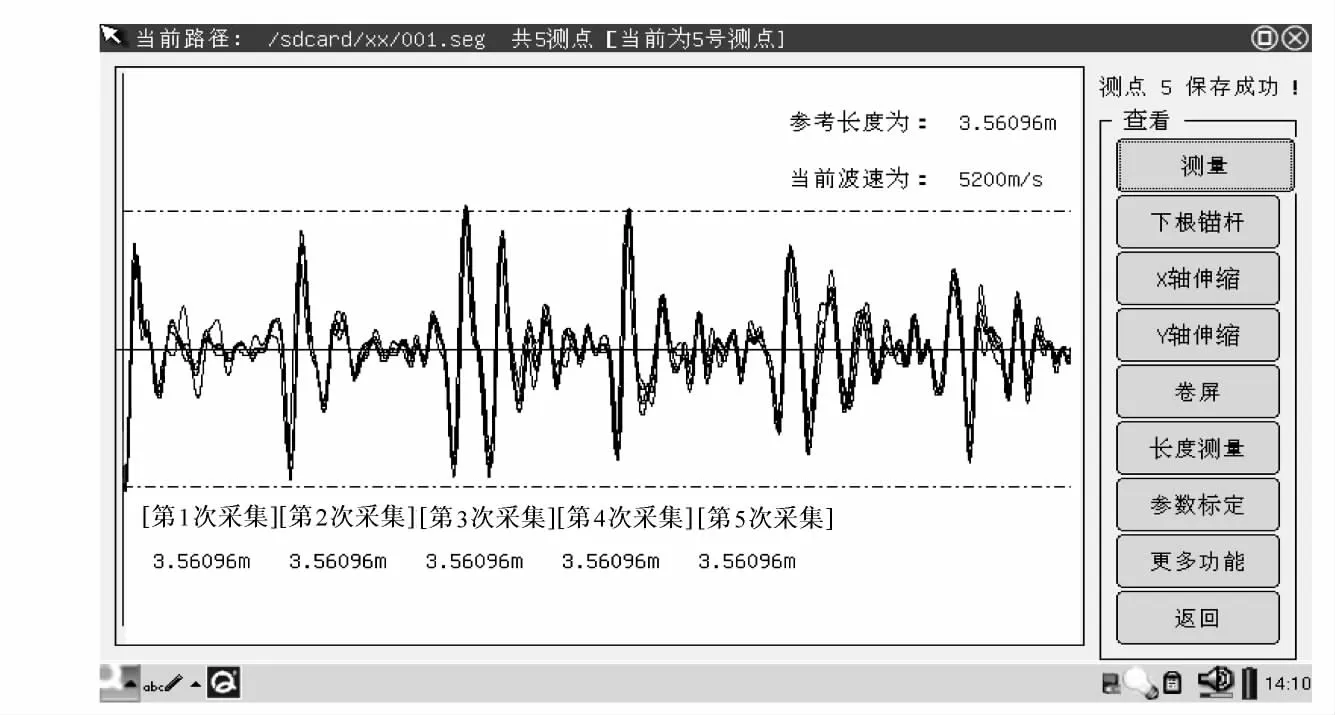

图4 仪器工作界面

当被测锚杆长度为10 m,检测信号长度取前8个周期的情况下,每次采集需要采样16 K个点,因此每次采样有256 Kb数据量,并在32 ms内完成采样及传输,此时传输率达到8 Mb/s。

根据文献[6](JGJ/T182-2009)要求,每根锚杆测量必须超过3次,试验中采用每根锚杆测量5次,并将每次采集到的波形按不同颜色叠加显示在同一屏幕上,这样可以更直观地显示测量的质量。

图4所示为一次野外测量的仪器工作界面,实际锚杆长度为3.5 m,5次测量结果都为3.56096 m,误差为1.7%,在文献[6]所要求的5%误差标准以内。仪器每次进行采集时反应迅速(即测即显示),极大地提高了工作效率。

[1]罗明璋,徐菲,王军民,等 .锚杆锚固质量检测仪应用软件在Ar m-Linux下的实现[J].长江大学学报(自科版),2008,5(3):199-201.

[2]朱晓鹏.ARM+FPGA的实时数据采集系统设计[J].计算机工程与设计,2009,30(13):3088-3090.

[3]金明 .FIFO芯片在高速系统中的应用[J].电子技术应用,1998,28(3):61-62.

[4]罗明璋,王军民,徐菲,等 .声频应力波实时检测分析仪[J].振动、测试与诊断,2012,32(2):292-295.

[5]王军民,陈义群,陈华 .高速公路锚杆锚固质量无损检测技术研究[J].地球物理学进展,2004,19(4):782-785.

[6]JGJ/T2009,锚杆锚固质量无损检测技术规程[S].