三相并网逆变器的软件锁相环研究

2013-11-12王艳姗王文光

潘 健, 王艳姗, 陈 融, 王文光

(1 湖北工业大学电气与电子工程学院, 湖北 武汉 430068;2 云南电投新能源开发有限公司, 云南 昆明 650051; 3 湖北化肥厂, 湖北 宜昌 443200)

并网逆变器作为能量传输的通道,是新能源发电、光伏发电和分布式发电系统等的重要组成部分,其性能的好坏会对电力系统中的电能质量产生很大的影响.当电网出现频率波动等问题时,要使并网过程中并网电流严格跟踪电网电压的频率和相位,必须保证锁相环及时做出反应,保证相位不变,减小对电网产生的冲击.锁相技术是实现高质量并网发电的关键技术,因此对锁相环的研究非常重要.

传统锁相环的硬件过零检测法的动态性能较差,且当电网电压出现畸变或三相不平衡时,可能导致同步信号的零点与基波零点不一致,或出现多个信号过零点的情况,从而导致锁相失败[1].文献[2]在传统软件锁相环的基础上,添加了一个低通滤波器(LPF),使得在电压畸变的情况下,锁相环仍然具有高精度,但没有考虑三相电压不平衡的情况.文献[3]利用T/4(T为三相电压周期)延时算法实现了正、负序分量的分离,解决了三相电压不平衡条件下锁相精度不高的问题,但计算相对比较复杂.

本文综合考虑三相电压畸变和三相电压不平衡两种情况,对传统软件锁相方法进行了改进.在传统软件锁相环基础上添加了2ω陷波器环节,其主要作用是滤掉与基波非常接近的2倍频负序分量.通过理论分析说明此种方法的优点,并模拟三相电压不平衡和电压畸变的情况,运用Matlab进行仿真.同时设计了一种基于FPGA的软件锁相环实现方案,以便通过实验平台进行验证.

1 三相并网逆变器

三相并网逆变器系统要求输出的正弦电流、电压与电网电压同步,且不含直流分量,总谐波畸变率要小[4].锁相环能对电压相位进行跟踪与锁定,对三相并网逆变器的锁相环研究显得尤为重要.

三相并网逆变器采用的三相桥式逆变电路的拓扑结构见图1,其中T1、T2、T3、T4、T5、T6分别代表主电路部分的6个开关管,利用LC滤波器进行滤波,滤波器输出并网电流为Ioa、Iob、Ioc.

图 1 三相并网逆变器拓扑结构

2 三相软件锁相环的基本原理

2.1 锁相环的基本原理

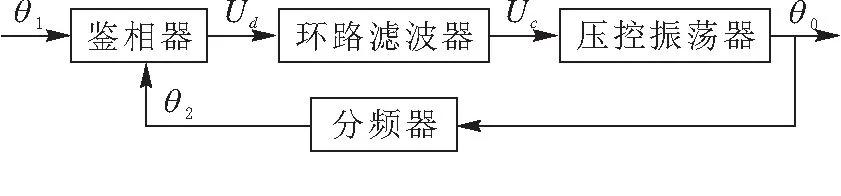

锁相环其实质是对系统的相位误差进行控制,从而准确锁定系统的相位,基本的锁相环主要由鉴相器、环路滤波器、压控振荡器和分频器四部分组成.其结构见图2.

图 2 锁相环结构图

鉴相器的输出信号既包含直流部分也包含交流部分.相位信息包含于直流部分中,谐波、各种干扰均为交流部分,交流部分经环路滤波器被滤除,直流部分作用于压控振荡器,并通过反馈形成闭环控制.

2.2 传统软件锁相环

传统的软件锁相环在电压不存在畸变,且三相平衡的条件下,能达到很好地效果,其原理见图3.但当三相电压不平衡或存在畸变时,很难保证锁相的精度和动态性能.

图 3 过零鉴相锁相环原理图

三相软件锁相环的输出为θ,当锁相成功时,q轴正序分量Usq量应为0,d轴正序分量Usd为额定值.因此可将参考值0与Usq相减得到误差信号,再将其送入PI调节器进行调节,得到误差信号ωcon,再将ωcon与理论角频率ω相加,得到时间角频率,经过积分环节,得到输出相位θ,从而实现闭环控制.

2.3 改进型软件锁相环

在传统软件锁相环基础上添加了2ω陷波器环节,其主要作用是滤掉与基波非常接近的2倍频负序分量.利用锁相环的低通滤波特性,使其在三相电压不平衡且有畸变的情况下,仍能很好的完成锁相.为简化分析,A/D采样环节采用了一阶延时模型.其原理如图4所示.

图 4 改进锁相环原理图

输入的三相不平衡电压为Usa、Usb、Usc,只考虑基波电压时,可将其表示为正序、负序和零序三者电压之和,即

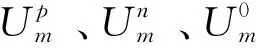

式中Tαβ-abc为两相坐标与三相坐标变换的矩阵,R(θ)、R(-θ)分别为正序、负序旋转坐标变换矩阵,且

进而可以得到

由上式可见,在旋转坐标系下,基波分量中的正序部分为直流量,而负序部分变成2次谐波分量,可将负序分量利用2ω陷波器将其滤除.经过坐标变换,高次谐波在原始基础上降低了一次,负序分量在原始基础上增加了一次,两者均呈现为交流量,软件锁相环利用自身的低通滤波特性将其滤除.将陷波器输出与给定值进行比较,然后通过PI调节器进行调节,再与理论角频率相加,最后通过积分环节,得到相角θ,从而实现闭环控制.

3 改进型软件锁相环仿真

3.1 改进型软件锁相环的特性分析

改进SPLL的控制框图如图5所示,其中1/s为积分环节,1/(1+Ts)为一阶延时环节,T为三相电压周期,Kp、Ki分别为比例和积分系数.

图 5 SPLL控制框图

系统的闭环传递函数

要保证系统稳定,则需

从闭环传递函数可以看出,系统是三阶系统,从系统的跟踪速率、稳定性和滤波效果三个方面考虑,合理设计Kp和Ki等参数,可以同时满足跟踪速度和滤除高次谐波的要求.三相电压不平衡时,输入电压含有2ω负序基波分量,利用2ω陷波器将其滤除.

3.2 改进型软件锁相环仿真

为验证所设计的改进型软件锁相环的可行性,利用Matlab仿真工具对其进行了仿真.

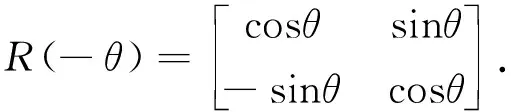

图6给出了模拟的三相不平衡且有畸变的电压波形,其对应的dq轴上电压波形见图7.与之前的分析一致,dq轴上的电压均为时变量.

图 6 三相不平衡且有畸变电压波形

图 7 dq轴电压波形

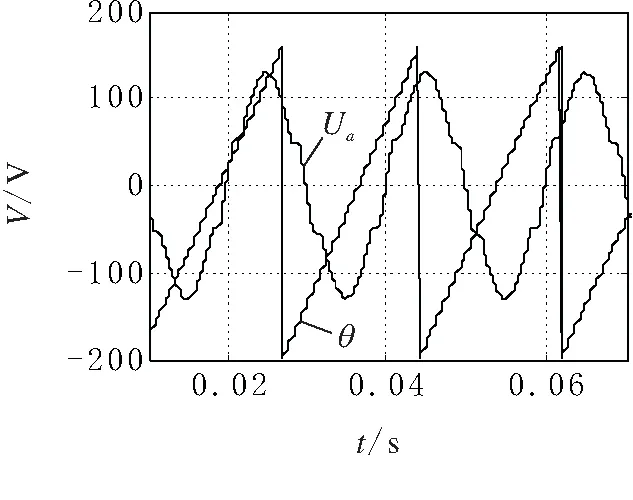

传统软件锁相环无法跟踪快速变化的q轴分量,这直接导致其锁相性能出现较大的误差.锁相环以A相电压相位作为参考,指导输出波形的相位,图8中锁相相角θ无法精确锁定A相电压的相位.图9给出了本文提出的改进型软件锁相方法的锁相波形,图中可以明显看出,锁相环的收敛速度和收敛精度比传统方法有了很大的提升,这种优异的抗扰动性能来源于所设计的陷波器,其能够消除大部分负序分量.本文所设计的陷波器能够较好地稳定q轴电压,加速锁相收敛过程.

图 8 传统软件锁相环锁相波形

图 9 改进型软件锁相环波形

4 基于FPGA的软件锁相方案

为了更准确地验证本文所设计的改进型软件锁相环的功能,设计出了基于FPGA的实现方案,以期在基于FPGA的变频调压电源实验平台上得到实现.FPGA通过软件编程可以实现坐标变换,正、负序分量分离,2ω陷波器,滤波器,PI控制器,积分器及一阶延时器等功能,从而实现锁相,为三相逆变器提供基波正序分量.设置相位补偿部分来解决FPGA实现软件锁相环过程中出现的采样延迟和滤波延迟.

其中压控振荡器和分频器的功能均由FPGA实现,同步信号由FPGA内部定时器的循环计数来产生,FPGA的A/D转换由分频后的输出信号启动,在一个工频电压周期内,利用锁相倍频输出实现等间隔的采样脉冲.其软件实现流程图见图10.

具体的实现过程为:在FPGA内部设计定时器PWM,初始值为0,当计数到N时,触发采样中断,开启PLL控制算法,计算下次计数周期值,刷新定时器比较值,当计数器再次计数到N时自动载入,滞后一拍.

图10 锁相环软件流程图

当第一次eCAP同步中断触发后,开启PWM定时器,并使能中断;第一次进行PWM定时器中断,采样值smpnum=1,相位为smpnum*2*pi/256,将其值送入3/2变换坐标系;此后每次进入PWM中断,采样值smpnum都自增1.当PWM中断计数到256时,采样值计算重置,smpnum=1.

5 结论

本文在传统的软件锁相环基础上,添加了2ω陷波器环节,设计了一种改进型软件锁相环,从理论分析和仿真实验两个方面证实了该方法锁相的精确度高于传统软件锁相环,锁相的收敛速度和收敛精度对比传统软件锁相环也有很大的提升,抗干扰性能好,且具有较好的动态响应特性.较好地解决了在三相电压不平衡且有畸变的情况下,锁相环精度不高、动态响应慢的问题.同时设计了一种基于FPGA的软件锁相环实现方案,通过实验平台进行验证.

[参考文献]

[1] 周国梁,石新春,付超.三相电压畸变条件下软件锁相环分析与实现[J].电力电子技术,2007(41):47-49.

[2] 李东,韦统振,霍群海,高绪华.电压畸变条件下软件锁相环精度提高[J].电力电子技术,2011(45):95-97.

[3] 吉正华,韦芬卿,杨海英.基于dq变换的三相软件锁相环设计[J].电力自动化设备,2011(31):104-106.

[4] 王磊,陈亦文,陈道炼.三相并网逆变器基准正弦电路的研究[J].电力电子技术,2011(45):33-34.