基于DSP Builder的FIR数字滤波器设计与仿真

2013-10-22郑争兵

郑争兵

(陕西理工学院物理与电信工程学院,陕西 汉中 723003)

0 引言

数字滤波器根据其单位冲击响应函数的时域特性可分为两类:无限冲击响应(Infinite Impulse Response,IIR)滤波器和有限冲击响应(Finite Impulse Response,FIR)滤波器。与IIR滤波器相比,FIR滤波器具有精确的线性相位、易于硬件实现和系统稳定等优点,在数字音频、图像处理、卫星导航和军事通信等领域得到了广泛应用[1-3]。

目前,FIR数字滤波器的主要实现方法有许多种。基于DSP芯片的设计方法采用内部特有的硬件结构实现滤波算法,需要进行指令编程同时还必须在DSP硬件上进行实时的在线仿真调试,开发流程复杂[4];基于MATLAB和DSP硬件的设计方法利用MATLAB进行辅助设计提取滤波器系数,但是需要在DSP上编写专门适合数字信号处理的指令代码,指令对硬件的依赖性强,可移植性差;基于FPGA芯片的设计方法采用VHDL语言进行算法设计,具有硬件可修改性且代码不依赖于芯片,但是代码仿真和调试相对复杂,开发周期相对较长[5-6]。因此,提出了一种基于DSP Builder工具的设计方法。该方法在MATLAB软件的Simulink环境下,采用Altera公司的DSP Builder工具箱,实现系统级的图形化模型仿真,并生成最终用于FPGA下载的VHDL代码。该方法能够灵活地设计滤波器结构,开发容易,易于进行功能的扩展和升级。

1 DSP Builder设计方法

DSP Builder是Altera公司推出的FPGA的系统级设计开发工具,将MATLAB/Simulink系统级设计工具的算法开发、仿真和验证功能与VHDL综合,仿真和实现结合在一起,简化设计过程,提高设计效率,进一步推动了FPGA在数字信号处理领域的应用。DSP Builder在Simulink环境中以Simulink的图形模块形式出现,利用自身Altera DSP Builder模块和已有的MATLAB函数和Simulink模块进行图形化模型设计和仿真。另外,DSP Builder利用 SignalCompiler模块把MATLAB/Simulink中的设计算法模型转换为QuartusⅡ软件工具可编译的VHDL文件。基于DSP Builder工具设计FIR滤波器的过程如图1所示。

首先根据FIR滤波器设计指标确定滤波器结构,在MATLAB/Simulink环境中建立一个模型文件(后缀mdl文件),用图形方式调用Altera DSP Builder模块和其它Simulink库中的模块,构成算法级设计框图;接着使用MATLAB中使用滤波器设计工具箱FDATool获取滤波器的设计参数,对图形模块进行参数配置,利用Simulink的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真;然后SignalCompiler工具将Simulink的模型文件转化为寄存器传输级的VHDL文件;最后在QuartusⅡ9.0中编译VHDL文件,下载FPGA硬件进行功能测试验证。

图1 基于DSP Builder设计FIR滤波器流程图

2 FIR滤波器基本原理

FIR滤波器的差分方程表达式为

其中,N是滤波器的阶数,单位脉冲响应h(n)是滤波器系数,x(n)是输入信号,y(n)是滤波后的输出信号。由(1)式可见,FIR滤波算法实质是一种乘累加运算。据此可知FIR滤波器采用直接型的结构来实现较为简单。如图2所示,输入信号x(n)经过不同的延迟因子z-1与适当的系数h(k)加权,然后将所得乘积相加就得到输出信号y(n)。x(n)是经A/D转换后得到的数字采样序列,y(n)是经过滤波器后的输出数字序列。该结构中,FIR滤波器的实现关键是系数h(k)的确定和延迟因子z-1的实现[7]。

图2 FIR滤波器的结构

3 基于DSP Builder的FIR滤波器设计

FIR滤波器设计方法主要有窗函数法、频率采样法和等波纹最佳逼近法,这里采用窗函数法。本文以设计FIR低通滤波器为例,说明基于Altera DSP Builder的FIR数字滤波器的实现方法。设计的FIR低通滤波器具体指标为:阶数8,通带截止频率1000 Hz,采样频率8000 Hz,采用汉明窗,10位输入数据宽度,8位系数数据宽度,直接型I型结构。

3.1 滤波器的系数计算

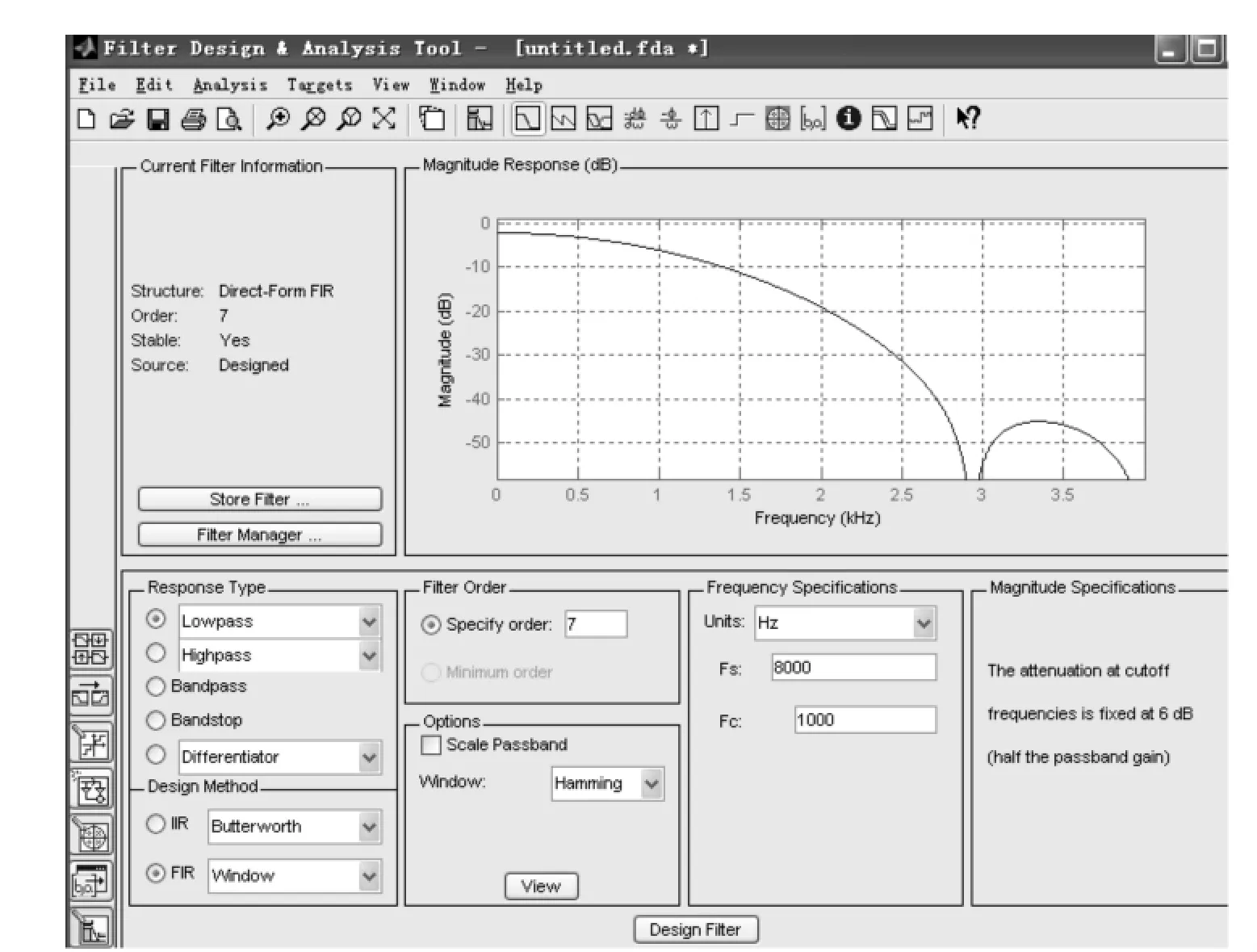

MATLAB中的滤波器设计工具箱FDATool具有良好的操作界面,能够完成滤波器的设计,实现参数提取和性能分析功能。首先打开MATLAB,在命令窗口中输入FDAtool,设置当前设计的滤波器参数,其FDAtool设计滤波器的界面如图3所示。

根据设计的要求,滤波器的类型指定为Lowpass(低通),滤波器的设计方法为FIR(Window),Window窗函数选为 Hamming,指定滤波器阶数设置为7[8],采样频率 Fs为8000 Hz,截止频率 Fc为1000 Hz,滤波器结构选为直接I型。指定完成这些滤波器设计参数后,点击DesignFilter,开始生成滤波器系数。由于浮点小数在FPGA中实现比较困难,因而需要将滤波器的系数转化为整数。在菜单File→Export→Variable Numbers中导出生成滤波器系数数值Num,利用函数round(Num*(2^10))得到10位的整数系数数值如下:

图3 FDAtool设计滤波器的界面

3.2 FIR滤波器模型建立

Simulink是MATLAB中一个专门用于对动态系统进行建模、仿真和分析的软件包[9]。通过调用Altera DSP Builder和Simulink库中的图形模块,构成FIR数字滤波器的系统结构框图(图4)。该模型主要由8阶直接型FIR滤波器模块和测试输入信号模块组成。8阶直接型FIR滤波器模块主要通过延时模块、系数增益模块和累加模块完成滤波功能。测试输入信号模块主要由扫频电路产生一个包含任意频率的扫频信号,该信号用来验证FIR滤波器模块的正确性。为了便于观察,通过示波器模块获取仿真结果。

在设计的过程,关键是对图形模块的参数配置。增益 Gain模块:(Gain0,Gain1,Gain2,Gain3,Gain4,Gain5,Gain6,Gain7)在库 Altera DSP Builder中 Ahmetic库,参数“Gain Value”分别设为“3,30,129,238,238,129,30,3”,参数“Gain Value number of bit”设为“10”,参数“Number of Pipeline Levels”设为“0”,不选择Use LPM;延时器Delay模块的延时参数“Number of Pipeline Stages”设置为“1”;加法减法器Parrallel Adder Subtractor模块的输入信号路数“Number of Inputs”设置为“8”,“Add(+)Sub(-)”设置为“+”,其他模块均要进行相应的设置。

3.3 FIR滤波器系统级仿真

在Simulink中建立好基于DSP Builder的FIR滤波器模型后,直接进行系统级的功能仿真验证。为了便于观察结果,设置示波器Scope模块的仿真时间参数要合理。选中其中的“Data history”,把Limit data points to tast:设为100000。选择Simulation菜单下的Start项,或按下“Ctrl+T”键开始启动仿真,得到的仿真波形如图5所示。

从图5可以看到,测试输入信号模块产生一个周期等幅的扫频测试信号,信号频率从低频变化到高频。等幅的扫频测试信号经FIR滤波器滤波后,信号的幅度随频率增加衰减增大,最终衰减至0,高频信号得到了有效抑制,FIR滤波器模型满足低通的滤波特性,达到了设计要求。

图4 FIR滤波器模型顶层图

图5 FIR滤波器的仿真波形图

3.4 FIR滤波器模型的工程文件生成

在Simulink中,对基于DSP Builder的FIR滤波器模型进行系统验证仿真,还需要在QuartusⅡ环境进行VHDL代码的时序仿真。SignalCompiler工具为系统仿真到硬件实现提供了一种有效的代码转换接口。在系统功能验证成功后,将FIR滤波器模型中的测试输入信号模块去掉,使用SignalCompiler工具生成QuartusⅡ的FIR滤波器工程文件和相应的VHDL文件,进行FPGA硬件测试验证。

4 结束语

基于DSP Builder的FIR滤波器的设计方法运用Altera DSP Builder和Simulink库中的图形模块进行模块化设计,配置图形模块参数,有效地完成了FIR滤波器模型和模型仿真。该方法操作方便,极大地缩短了滤波器的开发周期,避免了繁琐的VHDL语言编程,仿真验证过程简单,提高了数学信号处理算法的开发效率。该方法将为FPGA芯片在信号处理领域的应用提供更为广阔的空间。

[1]郑争兵.一种适用于电视频段的接收系统[J].电视技术,2011,35(19):62-64.

[2]陈正涛.光纤HFBR-1414发射器的驱动电路设计[J].国外电子测量技术,2010,29(5):79-80.

[3]郑争兵.开放式通信教学实验系统设计[J].实验室研究与探索,2012,31(3):55-58.

[4]郑争兵.基于MATLAB和DSP的数字滤波器设计[J].电子质量,2011(10):30-31.

[5]韩团军.基于VHDL步进电机控制器研制[J].电脑知识与技术,2009,25(5):7300-7302.

[6]郑争兵.基于FPGA的FSK调制解调系统设计[J].陕西理工学院学报:自然科学版,2012,28(5):20-21.

[7]郑争兵.基于FPGA的FIR滤波器的设计[J].通信电源技术,2008,25(3):45-46.

[8]罗韩君,刘明伟,王成.基于DSP Builder的FIR滤波器设计与实现[J].微计算机信息,2009,25(1):148-149.

[9]彭雪峰,汪临伟,许建平.基于 MATLAB与 QUARTUSⅡ的 FIR滤波器设计与验证[J].电子设计工程,2009,17(11):118-119.