不同表面修饰制备高性能柔性薄膜晶体管

2013-10-21林广庆熊贤风吕国强王晓鸿邱龙臻

林广庆,李 鹏,熊贤风,吕国强,王晓鸿*,邱龙臻*

(1.特种显示技术教育部重点实验室,特种显示技术国家工程实验室,现代显示技术省部共建国家重点实验室培育基地,合肥工业大学 光电技术研究院,安徽 合肥 230009;2.合肥工业大学 化工学院,安徽 合肥 230009;3.合肥工业大学 仪器科学与光电工程学院,安徽 合肥 230009)

1 引 言

有机薄膜晶体管(OTFT)因具有成本低、质量轻、可低温加工、适于制作柔性显示器件等优点,在平板显示中有非常大的应用前景[1-9],因此受到科研工作者的重视。自从1987年第一个有机薄膜晶体管诞生以来[10],无论是对OTFT 绝缘材料、半导体材料、电极材料的研究,还是对器件结构的改良,都取得了长足的发展。OTFT 的一大优势就是可以制作成柔性器件,而制作柔性器件首先需要选择可以弯曲的绝缘层,同时尽量提高绝缘层的介电常数,降低漏电流。本文选用PVP 材料做为绝缘层,采用表面镀有ITO(氧化铟锡)的PET(聚对苯二甲酸乙二酯)塑料做基底,制作柔性OTFT。

在众多对半导体材料的研究中,并五苯可以得到较高迁移率,因此本文中的OTFT 仍选取并五苯[11-13]做为半导体材料。在对并五苯的研究中,通过修饰绝缘层表面制备高性能的OTFT 已经引起了许多科研工作者的重视。其中最常用的方法是用单分子层进行表面修饰,修饰后改变了并五苯分子结晶时的结构序列和形态,使并五苯拥有更好的结晶性,最终OTFT 获得更好的电学性能。Bao[14]课题组采用HMDS 进行表面修饰,制作的并五苯的OTFT 器件迁移率达到3.5 cm2·V-1·s-1。在这些相关研究中,表面结构决定了半导体分子的生长密度和结晶结构。由于在绝缘层与有源层之间的界面上靠近半导体薄膜几个纳米的半导体薄膜结晶性能和排列方式对整个有机薄膜晶体管的性能有至关重要的影响,因此通过表面修饰可以控制栅绝缘层的表面特性(表面能、粗糙度和表面分子结构等),从而可以控制第一层半导体分子的生长方式,最终控制有机薄膜晶体管的电学性能。目前,有机薄膜晶体管中大多研究的是顶接触的器件,但是在实际应用时顶接触器件中电极的图案化往往会破坏半导体材料的性能。底接触器件由于首先制备电极再制备半导体薄膜,从而更适用于大面积工业化生产。

本文采用聚乙烯基苯酚(PVP)做绝缘层,分别用六甲基二硅胺(HMDS)和聚苯乙烯(PS)与氯硅烷的复合材料对栅绝缘层表面进行修饰,真空蒸镀并五苯作为半导体层制备了底接触的OTFT 器件。采用接触角和原子力显微镜研究了薄膜的表面形貌,并表征了OTFT 的迁移率、开关比、输出特性曲线,偏压应力等电学性能。还采用HMDS 作为表面修饰层制备了柔性OTFT。

2 实 验

2.1 实验试剂与仪器

N 型硅片购于合肥科晶公司;并五苯购于TCI 公司,纯度大于98%;六甲基二硅胺(HMDS)、聚乙烯基苯酚(PVP)、甲基化聚(三聚氰胺-co-甲醛)(PMF)、丙二醇单甲醚乙酸酯(PGMEA)、聚苯乙烯(PS,Mw=140 kg·mol-1)、1,6-二(三氯甲硅烷基)己烷(C6)均购于Aldrich chemicals Co.。甲苯(经过蒸馏提纯)、浓硫酸、双氧水购于国药集团化学试剂有限公司。

薄膜厚度采用Ambios XP-100 测试,器件的电学性能采用Keithley 4200 室温条件下测量,器件的偏压应力性能采用Lakeshoore TTPX 真空条件下测量。接触角测试采用Data Physics OCA-15。薄膜的表面形貌采用原子力显微镜(Digital Instruments Multimode)观察。

2.2 实验过程

硅片清洗:将N 型硅片浸泡在piranha 溶液(体积分数为70% 浓硫酸和30% 双氧水)中90℃加热30 min,超纯水洗净,氮气吹干。在热台上加热使硅片表面干燥,臭氧等离子机清洗20 min。

PVP 绝缘层的制备:1.085 g PVP 中加入交联剂0.744 g PMF,加入9 mL PGMEA 振荡均匀。3 500 r/min 45 s 旋涂得到PVP 薄膜,180 ℃真空烘箱中干燥90 min。PVP 薄膜的厚度为480 nm。PVP 膜表面没有经过修饰,在下文中称为PVP。

PVP 表面修饰:PS 和氯硅烷溶于甲苯,分别配制5 mg/mL 的溶液10 mL,1∶1进行混合,振荡均匀,3 500 r/min 45 s 旋涂在PVP 薄膜上,120℃热台上烘干,这种表面修饰在下文中简称CPS+PVP,该薄膜厚度为490 nm。HMDS 在同样的旋涂烘干条件下制备得到480~490 nm 厚的薄膜,这种表面修饰在下文中简称HMDS+PVP。

在上述绝缘层表面制备底栅底接触结构的并五苯薄膜晶体管器件,并五苯半导体薄膜的厚度为60 nm,蒸镀65 nm 的金作为源、漏电极,沟道长度为135 μm,沟道宽度770 μm。图1 所示为器件的结构图以及实验中使用的材料化学结构图。

图1 OTFT 结构图及材料的化学结构图Fig.1 Schematic illustration of OTFT and chemical materials

3 结果与讨论

3.1 绝缘层的结构、表面能及表面形貌

图1 所示为本文中器件的底接触结构图及使用的PVP 绝缘层材料,氯硅烷交联PS 及HMDS的化学结构图,PVP 绝缘层的交联采用文献中常用的方法;氯硅烷形成硅氧键与PS 聚合物链形成物理交联[15]。

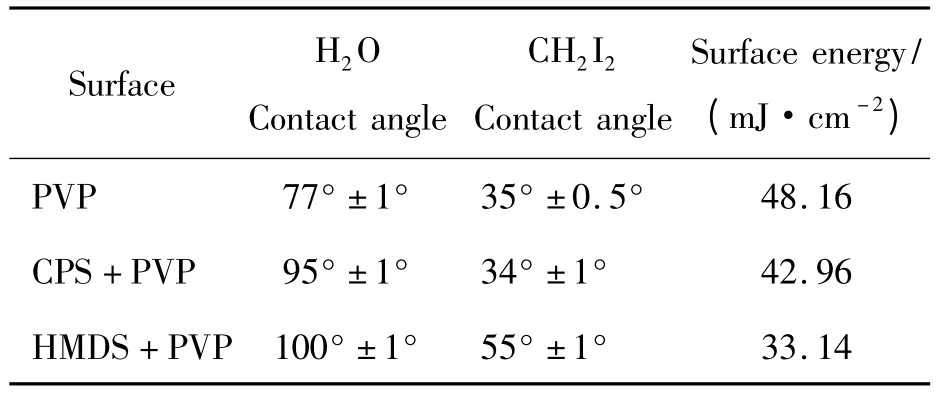

PVP 表面能为48.16 mJ·cm-2;CPS+PVP表面能为42.96 mJ·cm-2;HMDS +PVP 表面能为33.14 mJ·cm-2,表面能是一个逐渐变低的过程,表面能变化影响并五苯分子的生长排列方式和结晶结构。而根据文献报道[16],基底的表面能越小,生长的并五苯晶粒越大有利于获得高性能的晶体管器件。

表面修饰不仅影响薄膜表面的接触角和表面能,还对薄膜表面的粗糙度造成影响。图2 为原子力显微镜观察到的不同的表面修饰PVP 薄膜的表面形貌。从图中可以看出PVP 薄膜表面均方根粗糙度为0.322 nm,CPS +PVP 薄膜表面均方根粗糙度为1.139 nm,HMDS +PVP 薄膜表面均方根粗糙度为0.223 nm。表面粗糙度不同,并五苯的生长方式也发生了改变。根据文献[17]报道,在表面能相同的情况下,只改变表面粗糙度,并五苯分子在粗糙度低的薄膜上形成晶核数目少,形成的并五苯晶粒大;在粗糙度高的表面上形成晶核数目多,此时并五苯分子的晶粒小。

表1 不同衬底表面的接触角、表面能Table 1 Contact Angle,surface energy of the different substrate

在OTFT 器件中,在绝缘层和半导体层的界面处,第一层几个纳米的半导体分子的排列方式是决定器件电学性能的最重要因素。根据文献[18]报道,在整齐排列的第一层并五苯分子上更容易生长整齐排列的并五苯分子;而杂乱排列的第一层并五苯分子上更容易生长杂乱排列的并五苯分子。当在PVP 表面旋涂交联PS 薄膜和HMDS 后,由于表面能和表面粗糙度的改变,从而改变了第一层并五苯分子的排列和结晶方式,影响半导体层的生长方式。另外,不同修饰层上的并五苯具有不同的结晶特性,薄膜在单位面积下的晶粒数量越少,晶粒尺寸越大,会降低薄膜中的晶界密度,从而也减少了OTFT 器件工作时晶界陷阱对载流子的捕获,增强了载流子的传输能力,增强了OTFT 的电学性能。图2(d,e,f)分别为PVP、CPS+PVP、HMDS+PVP 并五苯薄膜的原子力图。由原子力图可以得出,在PVP 薄膜上沉积的并五苯晶粒尺寸都小于150 nm,而在CPS +PVP 表面上生长的并五苯晶粒尺寸多在200~400 nm,在HMDS +PVP 表面生长的并五苯晶粒尺寸多在400~600 nm。HMDS 修饰的并五苯薄膜晶粒尺寸最大,晶界对电荷载流子捕获最少,载流子输运能力高于PVP 薄膜和CPS+PVP 薄膜。

图2 不同衬底表面及该表面沉积60 nm 并五苯的AFM 照片。(a)PVP;(b)CPS+PVP;(c)HMDS+PVP;(d)PVP 上的并五苯膜;(e)CPS+PVP 上的并五苯膜;(f)HMDS+PVP 上的并五苯膜。Fig.2 AFM images of the different substrate surfaces and the 60 nm pentacene film on them.(a)PVP.(b)CPS+PVP.(c)HMDS+PVP.(d)Pentacene on PVP.(e)Pentacene on CPS+PVP.(f)Pentacene on HMDS+PVP

3.2 器件的电学性能

不同的表面修饰对器件的电容造成了影响。本文采用金属-绝缘层-金属(MIM)结构来测量不同修饰绝缘层的电容性质。图3 所示为不同薄膜的电容频率图,测量得到PVP 薄膜的电容密度为7.53~8.37 nF/cm2,CPS +PVP 薄膜的电容密度为7.39~8.30 nF/cm2,HMDS+PVP 薄膜的电容密度为7.32~8.16 nF/cm2。经过CPS 和HMDS修饰后,PVP 薄膜的电容密度降低很少,说明PVP薄膜是一种优异的聚合物绝缘层材料。

图3 不同衬底电容密度与频率的关系Fig.3 The change of capacitance density of different substrate with frequency

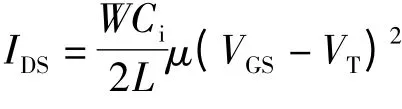

在栅压一定的条件下,HMDS +PVP 修饰的器件输出曲线中,可以看到明显的线性区和饱和区,栅电压可以实现对源漏电流良好的调控性能,PVP 薄膜和CPS+PVP 薄膜器件的电流开关比均为103,HMDS+PVP 薄膜器件的电流开关比可以达到105。

计算32~39 个器件的平均迁移率可知,未经过修饰的PVP 薄膜器件的平均迁移率只有1.56 ×10-3cm2·V-1·s-1,CPS +PVP 薄膜器件的平均迁移率为9.19 ×10-2cm2·V-1·s-1,HMDS+PVP 薄膜器件的平均迁移率为0.128 cm2·V-1·s-1。PVP 薄膜经过CPS 和HMDS 修饰后,与未修饰的器件相比迁移率分别提高了58倍和82 倍。阈值电压VT的平均值在经过不同的表面修饰时也发生了明显变化,PVP 薄膜和CPS+PVP薄膜器件的VT的平均值分别为3.59 V和-2.51 V,经HMDS 修饰的VT的平均值为0.41 V。亚阈值摆幅(SS)在不同表面修饰上也发生了明显变化,PVP 薄膜和CPS +PVP 薄膜器件的SS 的平均值分别为-12.81 V/dec 和-8.63 V/dec,经HMDS 修饰的SS 的平均值仅为-5.72 V/dec。亚阈值摆幅控制着器件从关态到开态的电压摆幅,目前无机硅器件的亚阈值摆幅在0.06 V/dec,通过HMDS 修饰的绝缘层SS 相比较未修饰PVP 和CPS +PVP 有了明显降低。结合器件的迁移率性能和开关比说明HMDS 是一种更优异的表面修饰材料。

进行不同的表面修饰改变了栅绝缘层的界面,致使并五苯的成膜结构发生了改变,施加电压时陷阱载荷数目不同,导致器件性能变化不同。为了研究不同表面修饰器件的稳定性,本文对各种不同绝缘层的器件做了偏压应力测试,因为水分对偏压的影响是非常大的[20],因此本文偏压应力测试条件是在真空条件下,持续加电压(VGS=-60 V,VDS=-5 V),分别在持续一段时间后测试转移曲线,共持续2 730 s。图5 所示为器件在施加偏压后转移曲线的变化,器件在施加偏压后,转移曲线均发生位移,器件的迁移率等性能都有较大降低。图6 为不同表面修饰的OTFT 器件加上偏压后器件的漏电流IDS和VT随时间的变化曲线。由该图可以看出,1 min 后PVP、CPS +PVP、HMDS+PVP 薄膜的漏电流分别下降35%、39%和52%;10 min 后薄膜的漏电流则分别下降了44%、87%和79%;45 min 后PVP 薄膜的漏电流基本维持不变,但CPS +PVP 和HMDS +PVP 器件IDS分别下降了91%和89%。小分子HMDS 的IDS相比于PVP 和CPS 下降更快,可能是由于PVP和CPS 绝缘层经过交联后聚合物链末端减少,从而降低了俘获载流子的陷阱浓度。不同的表面修饰的器件的漏电流IDS和阈值电压VT随时间变化下降均比较明显,PVP 薄膜经过CPS 和HMDS 修饰后,虽然器件的迁移率得到提高,但器件的漏电流在施加偏压应力后下降较纯PVP 薄膜更为明显。器件的阈值电压随偏压应力逐渐向负值变化,经过修饰后的PVP 薄膜变化也比纯PVP 薄膜变化更明显。偏压实验结果说明3 种不同表面修饰绝缘层器件在施加电压时,绝缘层半导体层界面上俘获载流子的缺陷浓度都比较高,导致器件连续工作时性能出现了比较大的下降。由此可得,经过HMDS 修饰的器件电学性能虽然有明显提升,但是偏压应力性能变差。因此,如何在提高器件迁移率的基础上,同时有良好的偏压应力性能是我们下一步要研究的重点内容。

图4 不同界面修饰的OTFT 器件的转移特性曲线(a,b,c)和输出曲线(d,e,f)。(a,d)PVP 薄膜;(b,e)CPS+PVP 薄膜;(c,f)HMDS+PVP 薄膜。转移曲线中VDS=-60 V,沟道宽度W=770 μm,长度L=135 μm,W/L=5.7。Fig.4 Electrical properties of pentacene OTFT on PVP (a,d),CPS+PVP (b,e)and HMDS+PVP(c,f).(a,b,c)Transfer characteristics.(d,e,f)Output characteristics.W=770 μm,L=135 μm,W/L=5.7.

表2 不同衬底表面OTFTs 的电学性能Table 2 Electrical characteristics of the OTFTs on different substrate

图5 不同衬底表面的偏压应力曲线。(a)PVP;(b)CPS+PVP;(c)HMDS+PVP。Fig.5 Bias-stress curve of the OTFT device on different substrate surfaces.(a)PVP.(b)CPS+PVP.(c)HMDS+PVP.

图6 (a)偏压应力下不同表面修饰OTFT 器件IDS(t)/IDS(0)与时间的关系;(b)偏压应力下不同表面修饰OTFT 器件VT与时间的关系。Fig.6 (a)-IDS(t)/-IDS(0)change of the different substrate surfaces.(b)VTH change of the different substrate surfaces.

因PVP 材料做绝缘层具有透明、可弯曲等优势,因此本实验以PET 材料做基底,PVP 薄膜做绝缘层,制作透明柔性的OTFT 器件。从上述实验分析中可知HMDS +PVP 的OTFT 器件的迁移率最高,因此在制作透明柔性OTFT 时采用HMDS +PVP 作为绝缘层。图7(a)为柔性实物图,图7(b)为转移特性曲线,图7(c)为输出特性曲线,可以发现用该方法制备的OTFT 器件开关比超过104,最高迁移率0.338 cm2·V-1·s-1,在输出特性曲线中看到明显的线性区和饱和区,栅电压对源漏电流的调控性能优异。由此可见,修饰PVP 绝缘层在制备柔性OTFT 器件中有很大的潜在应用。

图7 柔性OTFT 器件电学性能。(a)柔性器件实物图;(b)转移特性曲线;(c)输出特性曲线。沟道宽度W=770 μm,长度L=135 μm。Fig.7 Electrical performance of flexible OTFT device.(a)Digital photographic image of the flexible OTFTs.(b)Transfer characteristics.(c)Output characteristics.W=770 μm,L=135 μm.

4 结 论

分别采用交联聚苯乙烯(CPS)、六甲基二硅胺(HMDS)修饰聚乙烯基苯酚(PVP)绝缘层,研究了不同绝缘层的表面性质以及制备的并五苯OTFT 器件的电学性能。通过实验结果可以得出,经过HMDS 修饰后可以得到一种表面能、粗糙度相对较低的修饰层,并五苯分子容易形成较大晶粒,减少了器件工作时的陷阱浓度,从而提高了器件的迁移率。虽然经表面修饰的器件电学性能有明显提升,但是偏压应力性能下降很多。采用该方法在PET 基底上制备出了性能优异的OTFT 器件,为有机薄膜晶体管在柔性方面的应用提供了可供选择的绝缘层和修饰层,也为制备柔性显示器件提供了良好的研究基础。

[1]Crone B,Dodabalapur A,Lin Y Y,et al.Large-scale complementary integrated circuits based on organic transistors[J].Nature,2000,403(6769):521-523.

[2]Zhang H,Zhang L,Li J,et al.Improvement of ZnO-TFT performance by annealing ZnO Film[J].Chin.J.Lumin.(发光学报),2011,32(12):1281-1285 (in Chinese).

[3]Sekitani T,Noguchi Y,Hata K,et al.A rubberlike stretchable active matrix using elastic conductors [J].Science,2008,321(5895):1468-1472.

[4]DeLongchamp D M,Kline R J,Lin E K,et al.High carrier mobility polythiophene thin films:Structure determination by experiment and theory[J].Adv.Mater.,2007,19(6):833-837.

[5]Yan H,Chen Z H,Zheng Y,et al.A high-mobility electron-transporting polymer for printed transistors[J].Nature,2009,457(7230):679-686.

[6]Cho J H,Lee J,Xia Y,et al.Printable ion-gel gate dielectrics for low-voltage polymer thin-film transistors on plastic[J].Nat.Mater.,2008,7(11):900-906.

[7]Tsao H N,Cho D M,Park I,et al.Ultrahigh mobility in polymer field-effect transistors by design[J].J.Am.Chem.Soc.,2011,133(8):2605-2612.

[8]Sun X N,Di C A,Liu Y Q.Engineering of the dielectric-semiconductor interface in organic field-effect transistors[J].J.Mater.Chem.,2010,20:2599-2611.

[9]Jiao Y,Zhang X A,Zhai J X,et al.Effect of channel layer thickness on the device characteristics of room temperaturefabricated In2O3thin-film transistors[J].Chin.J.Lumin.(发光学报),2013,34(3):324-328 (in English).

[10]Lin Y Y,Gundlach D J,Nelson S F,et al.Stacked pentacene layer organic thin-film transistors with improved characteristics[J].IEEE.Elect.Device Lett.,1997,18(12):606-608

[11]Klauk H,Halik M,Zschieschang U,et al.High-mobility polymer gate dielectric pentacene thin film transistors[J].J.Appl.Phys.,2002,92(9):5259-5263.

[12]Kato Y,Iba S,Teramoto R,et al.High mobility of pentacene field-effect transistors with polyimide gate dielectric layers[J].Appl.Phys.Lett.,2004,84(19):3789-3791.

[13]Yoneya N,Noda M,Hirai N,et al.Reduction of contact resistance in pentacene thin-film transistors by direct carrier injection into a-few-molecular-layer channel[J].Appl.Phys.Lett.,2004,85(20):4663-4665.

[14]Yang H C,Shin T J,Ling M M,et al.Conducting AFM and 2D GIXD studies on pentacene thin films[J].J.Am.Chem.Soc.,2005,127(33):11542-11543.

[15]Yoon M H,Yan H,Facchetti A,et al.Low-voltage organic field-effect transistors and inverters enabled by ultrathin crosslinked polymers as gate dielectrics[J].J.Am.Chem.Soc.,2005,127(29):10388-10395.

[16]Yang S Y,Shin K,Park C E.The effect of gate-dielectric surface energy on pentacene morphology and organic field-effect transistor characteristics[J].Adv.Funct.Mater.,2005,15(11):1806-1814.

[17]Min H G,Seo E,Lee J,et al.Behavior of pentacene molecules deposited onto roughness-controlled polymer dielectrics films and its effect on FET performance[J].Synth.Met.,2013,163:7-12.

[18]Walter S R,Youn J,Emery J D,et al.In-situ probe of gate dielectric-semiconductor interfacial order in organic transistors:Origin and control of large performance sensitivities[J].J.Am.Chem.Soc.,2012,134(28):11726-11733.

[19]Choi D,Ahn B,Kim S H,et al.High-performance triisopropylsilethynyl pentacene transistors via spin coating with a crystallization-assisting layer[J].ACS Appl.Mater.Interf.,2012,4(1):117-122.

[20]Choi H H,Lee W H,Cho K.Bias-stress-induced charge trapping at polymer chain ends of polymer gate-dielectrics in organic transistors[J].Adv.Funct.Mater.,2012,22(22):4833-4839.