接入网多时钟域系统中异步FIFO控制器的设计

2013-10-20朱华伟

朱华伟

(四川文理学院,四川 达州635000)

1 引言

随着接入网技术的发展,单芯片的数据集成度越来越大,很多系统设计,比如EPON系统,GPON系统都是多时钟域系统。数据在不同时钟域之间传输时,容易产生亚稳态[1]。亚稳态不可避免,但是,可以通过设计高效的同步器,对信号进行同步,降低亚稳态产生的概率。目前比较常用的同步方式有握手信号同步和异步FIFO同步。握手信号同步准确性比较好,但是速度比较慢,仅仅适合对单一的信号进行同步,不适合总线信号。对总线信号进行同步,大多采用异步FIFO实现。

2 异步FIFO结构

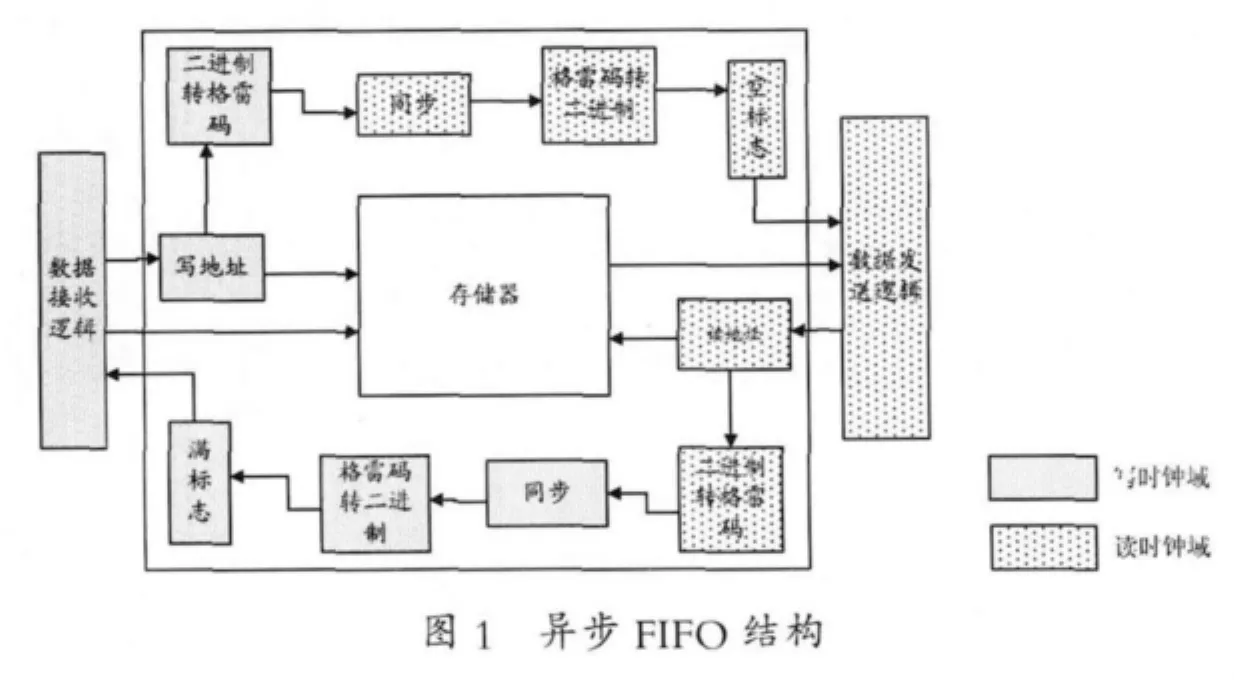

异步FIFO是一种双端口结构[2]。在输入端口方向,数据在写时钟信号和写使能信号的控制下被控制器写入RAM存储器;在输出端口方向,数据在读时钟信号和读使能信号的控制下从RAM存储器中读出来。当用读时钟取样写地址信号或用写时钟取样读地址信号时,取样结果具有不可预知性,可能产生亚稳态。因此,在写时钟域取样读地址信号时,需要对读地址信号进行同步处理,同理,在读时钟域取样写地址信号时,也需要对写地址信号进行同步处理。空满标志生成逻辑的实质是比较读写地址等信息来判断异步FIFO的状态,但是由于受同步过程的影响,同步后的读写地址信号与原信号相比存在延迟,这直接影响了空满标志信号的生成机制。此外,与一般系统中使用的异步FIFO相比,接入网系统中的异步FIFO还需要处理丢包的问题。本文阐述了一种基于二级同步技术的适用于接入网的高效异步FIFO控制器设计。图1所示为其结构框图,主要由存储器模块、写地址模块、读地址模块、同步模块、空满标志模块组成。

3 子模块设计实现

3.1 存储器

目前,通用的存储阵列主要有SRAM,DRAM和flash,这里使用SRAM来构成存储阵列。SRAM既不像DRAM那样需要预充电-求值过程,也不像Flash那样需要编程-擦除过程,使用效率较高。

为了满足当前接入网广泛采用的1G以上的数据传输速率,存储阵列深度设为512,宽度设为72,可以存储2个最大长度为2000字节的数据帧,通过循环读写的方式实现数据输入输出操作。

3.2 写地址模块

写地址模块控制FIFO的数据输入操作。当FIFO未满且写使能有效时,写数据控制逻辑在写系统时钟的上升沿,向当前写地址所指的存储空间写入数据。写地址总指向下一个要写入数据的地址,初始化时写地址指向位置0,每输入数据一次,写地址增加1,当到达存储器最大位置时,写地址又复位为0,如此循环往复实现异步FIFO数据的循环输入。当遇到接入网数据传输中普遍存在的丢包问题时,写数据控制逻辑还需要执行写地址复位操作,使写地址复位到开始写数据包的状态。

写地址模块通过生成写地址指针和写地址基址指针两个寄存器来控制数据的写入和丢弃处理。写地址指针存储FIFO写数据的写地址,位宽为10,其中低9位作为RAM写地址,最高位为写数据的标志位,用于控制生成空满指示信号。写地址基址指针存储数据包开始输入时的写地址,主要用于丢弃数据包时恢复写地址指针,因此,开始接收数据包时,写地址指针自增前应以写地址指针值置位写地址基址指针;收到丢弃帧指示时,以基址指针值来复位写地址指针,从而实现丢弃数据包的系统复位操作。也就是说,丢弃数据包并不需要复位所有待丢弃数据所在的存储器,只需复位写地址指针即可。

3.3 读地址模块

读地址模块控制数据的输出操作。当FIFO未空且读使能有效时,在读系统时钟的上升沿,从当前读地址所对应的存储单元中读出数据。读地址也总是指向下一个要读出数据的读地址,初始复位时,读地址指向存储器的0地址,每读一次数据,读地址自增1,读到存储器的最大地址时,重新复位为0。

读地址模块通过生成读地址指针来控制数据读取。同写地址指针一样,读地址指针也采用10位计数器实现,其中低9位作为RAM地址,最高位为标志位。

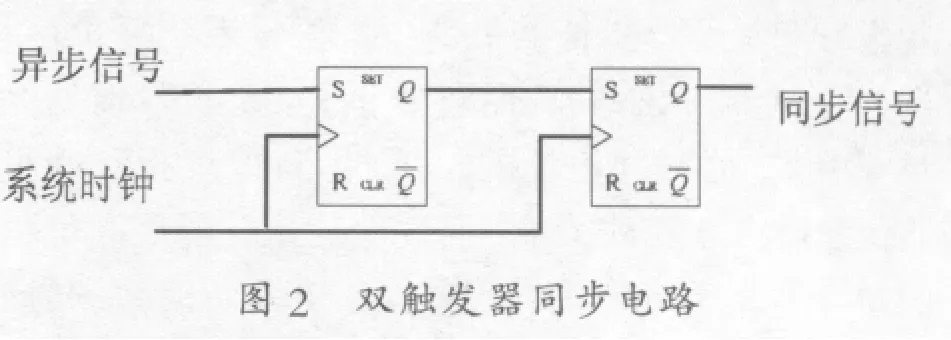

3.4 同步模块

当信号从一个时钟域向另一个时钟域传输时,为了保证信号正确采样,避免产生亚稳态,需要对信号进行同步。为了提高同步效果,这里采用同时使用双触发器同步和格雷码同步的二级同步技术对异步信号进行同步。双触发器同步器是通用同步器[3-4],如图2所示,异步信号在经过两级触发器后,输出信号即为同步信号。但是同步后的信号在数据采样时还是会出现采样错误,假如16位地址指针在0x0和0xffff之间变化,显然,出现变化的位的数量同出错概率成正比。为了减少出错概率,我们另外采用格雷姆来编码地址指针,格雷码是最小码,每次只有一位变化,同步时,出错的概率相应较小。

异步FIFO控制器主要有两个同步逻辑单元,分别为在读时钟域同步写地址指针和在写时钟域同步读地址指针,它们的实现逻辑相同,这里以前者为例对同步的流程进行阐述:

(1)在写时钟域变换二进制写地址指针为格雷码写地址指针,二进制转换为格雷码的公式为:

GN=BNB表示二进制数据,G表示格雷码数据

GI=BI异或BI+1I≠n,N表示最高位,I表示其它位

(2)在读时钟域同步格雷码写地址指针,同步采用双触发器同步电路,见图2。

(3)在读时钟域变换格雷码写地址指针为二进制写地址指针,格雷码转换为二进制的公式为:

BN=GNB表示二进制数据,G表示格雷码数据

BI=GI异或BI+1I≠n,N表示最高位,I表示其它位

3.5 空满标志模块

对FIFO进行读写之前,需要正确判断FIFO的空满状态,以免产生读空或溢出错误[5-7]。受同步器的延时影响,在写时钟域采样的读地址指针值与当前的读地址指针值是不相同的,依据该采样值生成的满标志信号显然也存在滞后性的问题,不能反映当前异步FIFO的已满/非满状况。这样就可能出现满标志置位,而异步FIFO没满的情况,与实际相比出现了少写的问题。显然,阻止额外的写操作虽然降低了FIFO的利用效率,却避免了出现溢出错误。为此,在具体实现时,如果满标志置位,即便FIFO还有空间,也阻止进一步的写操作。同理适用于读操作。

空满标志模块生成FIFO空满标志信号。通常空满标志生成逻辑实现主要有三种方法,第一种是设置标志位,第二种是设置计数器,第三种是比较读写地址。这里综合第一和第三种方法生成空满标志信号。一般情况下,写地址大于空地址时,异步FIFO处于非满非空状态。当写地址和读地址相等时,就可能出现两种情况,一种是没有数据写入或者写入的数据已被读完,即异步FIFO处于空状态;另外一种是异步FIFO已写满,写地址循环了一周又赶上了读地址,即异步FIFO处于满状态。因此,仅仅比较读写地址值判断异步FIFO空满状态是不够的,为此,这里又重新设置了一个标志位,即读地址指针和写地址指针的最高位。假设系统复位后,即向存储器写数据,此时停止读操作,当写地址循环了一周,返回读地址的位置时,写地址指针的最高位已经由0变到了1,而读地址指针的最高位仍旧是0,此时异步FIFO已满。此后开始读数据,同时停止写操作,当读地址循环了一周,返回到写地址的位置时,读地址指针的最高位已经由0变到1,同读地址指针最高位相同,此时异步FIFO已空。

满标志实现逻辑如下:

(1)初始化时,满标志信号值置为0。

(2)写指针与读指针最高位值不相等,低9位值相等时,置满标志信号值为1。

(3)除此之外,置满标志信号值为0。

空标志实现逻辑如下:

(1)初始化时,空标志信号值置为0。

(2)读指针与写指针相等时,置空标志信号值为1。

(3)除此之外,置空标志信号值为0。

4 设计仿真

系统设计时,利用ISE10.1进行RTL级逻辑设计和综合处理,然后设计仿真测试平台[8-9],利用Midelsim5.4a仿真工具对系统进行了门级仿真。仿真结果如图3,图4所示。在异步FIFO输入端口,系统工作在clk_ge时钟域,数据被写入异步FIFO(data_gewr[71:0])。在异步FIFO输出端口,系统工作在clk_sys时钟域,帧数据又重新从异步FIFO中读了出来(data_gerd[71:0])。

5 结语

根据异步FIFO和接入网多时钟域系统的特点需求,本文提出了一种适用于接入网多时钟域系统的异步FIFO控制器设计方案,并用硬件描述语言及相应的仿真工具进行了功能仿真,仿真结果表明,设计能很好地按照设计的意图工作。

[1]刘飞,卢结成,姜文奇,等.一种基于音频解嵌的异步FIFO设计及 FPGA 实现[J].微型机与应用,2011(9):15-17.

[2]彭瑶,周端,杨银堂,等.高速环形FIFO的设计[J].计算机辅助设计与图形学学报,2011(3):489-491.

[3]胡昌顺,高嵩,吴春瑜,等.SOC设计中多bits数据跨时钟域的解决方法[J].辽宁大学学报,2011(1):12-14.

[4]李冬,赵志凯.一种高性能异步FIFO的设计与实现[J].微电子学与计算机,2010(8):145-148.

[5]张莹,阳璞琼.FIFO可靠性设计与研究[J].微处理机,2008(6):171-172.

[6]夏琴香,周思聪,王石子,等.高速大容量FIFO缓冲存储器设计[J].微计算机信息,2009(35):7-9.

[7]柳震,郭黎利,王鹏宇.通信数据同步中基于FPGA的一种有限任意长FIFO的生成办法[J].自动化技术与应用,2011(3):41-42.

[8]伯杰龙.System Verilog验证方法学[M].北京:北京航空航天大学出版社,2007.

[9]克里斯·斯皮尔著,张春,麦宋平,赵益新等译.SystemVerilog验证:测试平台编写指南[M].北京:科学出版社,2009.